# In the Matter of Certain Wireless Consumer Electronics Devices and Components Thereof

Investigation No. 337-TA-853

# Complainants' Technology Tutorial

Before the Honorable E. James Gildea

March 5, 2013

# **Pioneering Technology**

- Co-inventors Charles Moore and Russell Fish

- In 1988 and 1989, Moore and Fish designed a 32bit microprocessor called "ShBoom"

- The IEEE identified ShBoom as one of "The 25 Microchips that Shook the World"

- Moore was inducted into the Computer Design Hall of Fame and received a Presidential Commendation, among other awards

# **Pioneering Technology**

- On August 3, 1989, the inventors filed a comprehensive patent application, from which seven patents issued

- The '336 patent has been subjected to six ex parte reexamination requests since 2006

- Over 600 separate prior art references have been cited against the '336 patent in the reexaminations

# **Pioneering Technology**

- Over 100 global electronics firms have licensed the Moore patents, including:

- Sony

- Intel

- Hewlett Packard

- Motorola

- General Electric

- Panasonic

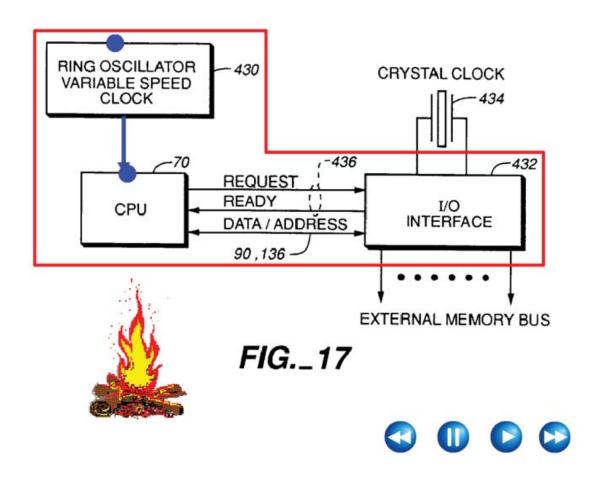

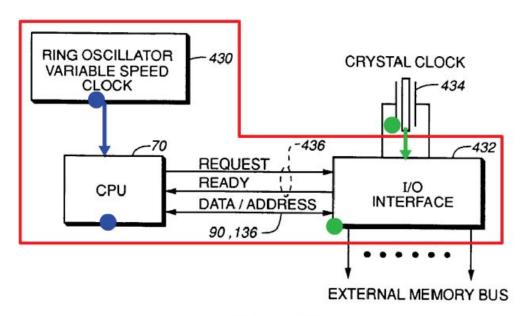

- The '336 patent teaches the use of two independent clocks in a microprocessor system:

- an on-chip first clock to time the CPU, and

- a second, independent, clock to time the input/output (I/O) interface.

- Decoupling the system clock from the I/O clock allows the clocks to run independently (or "asynchronously"), and thus allows the CPU to run faster when needed (or more slowly to conserve power).

- The on-chip oscillator that is used to clock the CPU is constructed on the same integrated circuit as the CPU

- The invention takes advantage of the laws of physics

- Because the clock is on the same silicon die as the CPU, the capability of both will vary similarly with respect to variations in temperature, voltage, and manufacturing

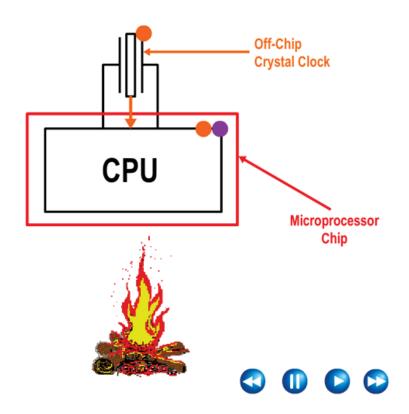

# Old Way of Clocking CPU

5.809.336

- As shown in FIG. 13, the microprocessor 50 provides both conchip registers 134 and a stack 74 and seep the benefits of both.

1. Stack matched engine to the read to be evaluable.

1. Stack matched engine rouly matchin. Most programmers and optimizing complex can take adversary of this feature.

2. Sinteen registers are available for on-chip seeing of both variables which can transfer to the stack for computation. The accessing of variables for matching the control of the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for matching the stack for computation. The accessing of variables for the superior of the stack for computation. The accessing of variables for a lipid to the longer state of the superior of the stack for computation. The accessing of variables is the ten fine adversariage of SKIP operation in the righter 104. As indicating on the 2-th interioristical concerns the substantian of the register 104. As observed, the size of the register 104. As observed, the size of the register 104. As observed, the size of the register 104 to a size of 104 to a size

time likely to be encountered from a lightly to heavily loaded memory system. When the OE line 152 has reached a predetermined level to generate the READY signal, driver 418 generates an OUTPUT ENABLE signal on OE line 152. SKIP WITHIN THE INSTRUCTION CACHE

memory cycle and stores them in a 32-bit instruction register 108, as shown in FIG. 16. A class of "test and skip" instructions can very rapidly execute a very fast jump operation within the four instruction cache. SKIP CONDITIONS:

ACC negative

ACC equal zero

compare acagness or oparating compares and the mix of transfer versus such as an attached in the mixture of the

The microprocessor 50 was the technique shown in FIGS.

517–19 to generate the system clock and its required flauses.

Clock circuit 430 is the familiar "ring socillate" used to test

process performance. The clock is fabricated on the same

silicon chip as the rost of the microprocessor 50.

The ring oscillator frequency is determined by the paramicollects of temperature, voltage, and process. At resem

temperature, the frequency wall be in the one-glock-ordered of

ACC positive

ACC positive

Cryp flag qual logic zero

The SMF instruction can be located in zero of the first

blue positions. 240 in the 23-bit instruction register [48 if II] with 18 is stages. 441 producing phase before a Comparison of the test is successful, SSIP will jump over the remaining

one, two, or three 8-bit instructions in the instruction register.

ACC produced by the position and place in the account of the control of the

"Traditional CPU designs are done so that with the worse case of the three parameters [temperature, voltage and variations in semiconductor processing], the circuit will function at the rated clock speed."

"The result are designs that must be clocked a factor of two slower than their maximum theoretical performance, so they will operate properly in worse case conditions."

# **Old Way of Clocking CPU**

# The Moore Solution: On-Chip System Clock On-Chip Devices of the CPU and System Clock Vary Together

5.809.336

- on an equivalent register only machine. Most program-mers and optimizing compilers can take advantage of

- 2. Sixten registers are available for ne-chip sorrage of local variables which can transfer to the stack for computation. The accessing of variables is three to four times as fast a variable or a strictly stack medicine. The combined stack 74/register 134 architecture has not been used previously to be inactured understanding by computer resigners of optimizing compiters and the max of second consideration of the consideratio ransfer versus math/logic instructions. ADAPTIVE MEMORY CONTROLLER

ADAPTIVE MEMORY CONTROLLER

Amicroprocessor must be designed to work with small or large memory configurations. As more memory tous due to the signals slowes down. The microprocessor 50 miles (see a signal slowes down. The microprocessor 50 miles (see a signal slowes down. The microprocessor 50 miles (see a signal slowes down. The microprocessor 50 miles (see a signal slowes down. The microprocessor 50 miles (see a signal slowes down. The microprocessor 50 miles (see a signal slowes down the signal sl

memory dips connected. A speed compromise of as mean as 50% is required.

As shown in FIG. 14, the microprocesser 59 uses a feethed technique to allow the processor to algod memory of the feethed technique to allow the processor to algod memory of the feethed technique to allow the processor to algod memory of the feethed technique to allow the processor of the feethed technique to allow the feethed technique to allow the feethed technique to the feethed technique to

time likely to be encountered from a lightly to heav loaded memory system. When the OE line 152 has react a predetermined level to generate the READY signal, dri em. When the OE line 152 has reached rates an OUTPUT ENABLE signal on OE line 152. SKIP WITHIN THE INSTRUCTION CACHE

108, as shown in FIG. 16. A class of "test and skir

ACC negative

ACC complizero

Carry flag equal logic zero

The SKIP instruction can be located in any of the four type positions 420 in the 32-bit instruction register 108. If he lest is successful, SKIP will jump over the remaining

108 and cause the next fear-instruction group to into the regioner 108. As shown, the SSLP or implemented by resetting the 2-bit microinteract. 180 to necessor line 422 and simultaneously taskly instruction group into the register 108. Any is following the SSLP in the instruction register are:

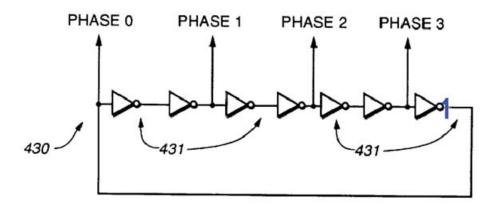

The patent discloses a microprocessor embodiment where "[t]he clock is fabricated on the same silicon chip as the rest of the microprocessor 50."

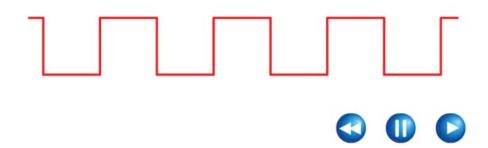

The "[c]lock circuit 430 is the familiar 'ring oscillator' ...." "The ring oscillator 430 is useful as a system clock ... because its performance tracks the parameters which similarly affect all other transistors on the same silicon die."

- A "ring oscillator" An oscillator having a multiple, odd number of inversions arranged in a loop.

- Specifically, a Ring Oscillator must have:

- At least 3 inversion stages that invert the inputted value.

- The multiple odd number of inversions ensure a change of state (Hi to Low, or Low to Hi) at each inversion stage.

- Even numbers become stuck at logic high or low state.

- While other types of oscillators exist they should not be confused with the "continual inversion" phenomenon that causes the oscillation in a ring oscillator.

# The '336 Patent: Ring Oscillator

FIG.\_18

- On-Chip oscillators vary due to one or more of "PVT":

- The semiconductor manufacturing or fabrication Process

- The Voltage supplied

- The Temperature of the circuit

- Since the CPU and the on-chip oscillator are on the same integrated circuit, they will be similarly affected by Process, Voltage, Temperature variations.

# I/O Interface Timed by Independent Off-Chip Clock

FIG.\_17

# Thank you