| 1 2                                          | Michael J. McKeon ( <i>Pro Hac Vice</i> ), mckeon@fr.c<br>Christian A. Chu (SBN 218336), chu@fr.com                                                                                      |                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                                            | Richard A. Sterba ( <i>Pro Hac Vice</i> ), sterba@fr.com<br>FISH & RICHARDSON P.C.                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |

| 4                                            | 1425 K Street, NW, Suite 1100<br>Washington, DC 20005                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                |

| 5                                            | Telephone: (202) 783-5070<br>Facsimile: (202) 783-2331                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                |

| 6                                            | Wasif Qureshi ( <i>Pro Hac Vice</i> ), <u>qureshi@fr.com</u> FISH & RICHARDSON P.C.                                                                                                      |                                                                                                                                                                                                                                                                                                                                                |

| 7                                            | 1221 McKinney Street, Suite 2800<br>Houston, TX 77010                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                |

| 8                                            | Telephone: (713) 654-5300<br>Facsimile: (713) 652-0109                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                |

| 9                                            | Olga I. May (SBN 232012), omay@fr.com<br>FISH & RICHARDSON P.C.                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                |

| 10                                           | 12390 El Camino Real                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                |

| 11                                           | San Diego, CA 92130<br>Telephone: (858) 678-4745                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                |

| 12                                           | Facsimile: (858) 678-5099                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                |

| 13                                           | Attorneys for Defendants LG ELECTRONICS, INC. and LG ELECTRONIC                                                                                                                          | CS U.S.A., INC.                                                                                                                                                                                                                                                                                                                                |

| 14                                           | UNITED STATES I                                                                                                                                                                          | DISTRICT COURT                                                                                                                                                                                                                                                                                                                                 |

| 15                                           | NORTHERN DISTRIC<br>SAN JOSE I                                                                                                                                                           | CT OF CALIFORNIA                                                                                                                                                                                                                                                                                                                               |

| 15<br>16                                     | SAN JOSE I<br>TECHNOLOGY PROPERTIES LIMITED LLC,                                                                                                                                         | CT OF CALIFORNIA                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                                                                                                                                                          | CT OF CALIFORNIA<br>DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC.                                                                                                                                                                                                                                                       |

| 16                                           | SAN JOSE I<br>TECHNOLOGY PROPERTIES LIMITED LLC,<br>PHOENIX DIGITAL SOLUTIONS LLC, and                                                                                                   | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO                                                                                                                                                                                         |

| 16<br>17                                     | SAN JOSE I<br>TECHNOLOGY PROPERTIES LIMITED LLC,<br>PHOENIX DIGITAL SOLUTIONS LLC, and<br>PATRIOT SCIENTIFIC CORPORATION,                                                                | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY,                                                                                                                                      |

| 16<br>17<br>18                               | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG                           | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON                                                                                      |

| 16<br>17<br>18<br>19                         | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC., | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON CHARTED PROCESSORS                                                                   |

| 16<br>17<br>18<br>19<br>20                   | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG                           | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON CHARTED PROCESSORS  DATE: June 30, 2015 (by order) TIME: 10:00 AM                    |

| 16<br>17<br>18<br>19<br>20<br>21             | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC., | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON CHARTED PROCESSORS  DATE: June 30, 2015 (by order)                                   |

| 16<br>17<br>18<br>19<br>20<br>21<br>22       | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC., | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON CHARTED PROCESSORS  DATE: June 30, 2015 (by order) TIME: 10:00 AM PLACE: Courtroom 5 |

| 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | SAN JOSE I TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,  Plaintiffs,  v.  LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC., | CT OF CALIFORNIA DIVISION  Case No. 3:12-cv-03880-VC  DEFENDANTS LG ELECTRONICS, INC. AND LG ELECTRONICS U.S.A., INC.'S NOTICE OF MOTION AND MOTION TO STRIKE INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY, COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON CHARTED PROCESSORS  DATE: June 30, 2015 (by order) TIME: 10:00 AM PLACE: Courtroom 5 |

28

### **TABLE OF CONTENTS**

| 2                               | I.   | INTRO | DDUCTION                                                                                                                                                           | 2  |

|---------------------------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3 4                             | II.  | FACT  | UAL BACKGROUND                                                                                                                                                     | 3  |

| 5                               |      | A.    | Case History                                                                                                                                                       | 3  |

| 6                               |      | B.    | Deficiencies in Plaintiffs' Infringement Contentions                                                                                                               | 4  |

| 7                               |      |       | 1. Cover Pleading                                                                                                                                                  | 5  |

| 8                               |      |       | 2. Exhibit A                                                                                                                                                       | 5  |

| 9                               |      |       | 3. Claim Charts                                                                                                                                                    | 5  |

| 10                              |      | C.    | The Parties' Meet-and-Confer Process                                                                                                                               | 8  |

| 11                              | III. | LEGA  | L STANDARD                                                                                                                                                         | 9  |

| 12                              | IV.  | ARGU  | JMENT                                                                                                                                                              | 9  |

| 13                              |      | A.    | Plaintiffs' Contentions with Respect to All Products that Do Not<br>Contain the Seven Charted Processors Should Be Stricken for<br>Lack of Any Evidentiary Support | 9  |

| <ul><li>14</li><li>15</li></ul> |      |       | 1. Allegations as to "Each Accused Microprocessor" Based on "Information and Belief," Knowledge of One Skilled                                                     |    |

| 16                              |      |       | in the Art or Generic Information Fail to Meet Rule 3-1                                                                                                            | 10 |

| 17                              |      |       | 2. Allegations based on "Representative" Products Fail to Meet Rule 3-1                                                                                            | 11 |

| 18                              |      | B.    | Infringement Charts as to Seven Named Processors Are Deficient                                                                                                     | 13 |

| 19                              |      | C.    | Infringement Contentions based on the '890 and '749 Patents as to the Accused Products that Were Released after the Expiration                                     |    |

| 20                              |      |       | of These Patents Should Be Stricken                                                                                                                                | 14 |

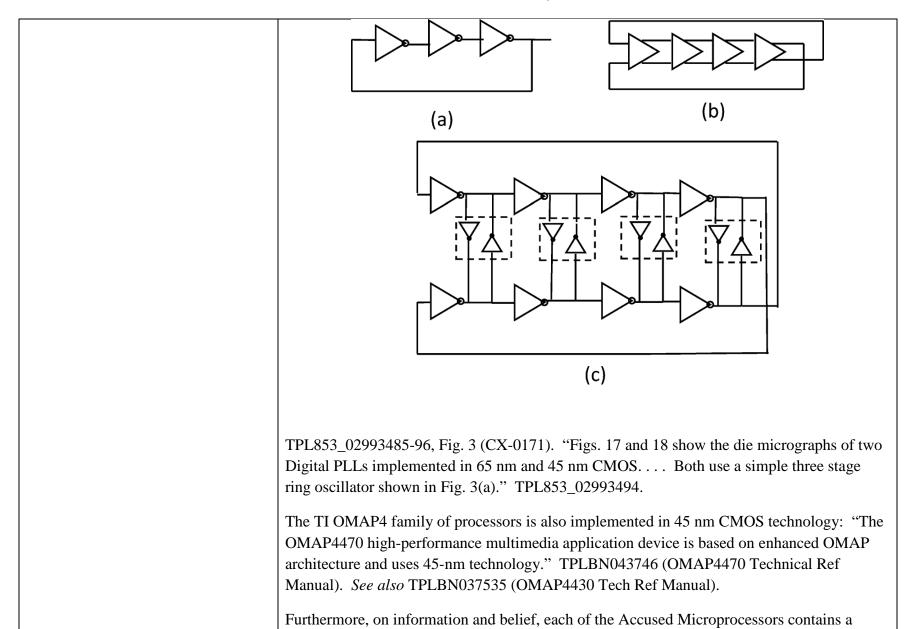

| 21 22                           |      | D.    | Infringement Contentions as to the Accused Products that LG Has Never Made, Used, Imported, Sold, or Offered for Sale in the United States Should Be Stricken      | 14 |

| 23                              |      | E.    | If the Court Permits Plaintiffs to Supplement Their Contentions,                                                                                                   |    |

| 24                              |      |       | Any Amendment Should Be Limited to Products with the Seven Charted Processors                                                                                      | 15 |

| 25                              | V.   | CONC  | LUSION                                                                                                                                                             | 16 |

| 26                              |      |       |                                                                                                                                                                    |    |

| 27                              |      |       |                                                                                                                                                                    |    |

### **TABLE OF AUTHORITIES**

| 2                               | Page(s)                                                                                                                            |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 3                               | Cases                                                                                                                              |

| 4                               | Ameranth, Inc. v. Pizza Hut, Inc., 2013 WL 3894880, at *7 (S.D. Cal. July 26, 2013) Nos. 12-cv-00729                               |

| 5<br>6                          | Atmel Corp. v. Information Storage Devices, Inc., 1998 WL 775115 (N.D. Cal. Nov. 5, 1998)15                                        |

| 7<br>8                          | Bender v. Freescale Semiconductor, Inc.,<br>No. C 09–1156 PHJ (MEJ), 2010 WL 1689465 (N.D. Cal. Apr. 26, 2010)9, 11                |

| 9                               | CSR Tech. Inc. v. Freescale Semiconductor,<br>No. C-12-02619 RS (JSC), 2013 WL 503077 (N.D. Cal. Feb. 8, 2013)10                   |

| 10<br>11                        | Digital Reg of Texas, LLC v. Adobe Sys., Inc.,<br>No. 12-CV-01971-CW (KAW), 2013 U.S. Dist. LEXIS 93814 (N.D. Cal. July 3, 2013)15 |

| 12<br>13                        | Fujitsu Ltd. v. Netgear Inc.,<br>620 F.3d 1321 (Fed. Cir. 2010)                                                                    |

| 14                              | Halo Elecs., Inc. v. Pulse Elecs., Inc., 769 F.3d 1371 (Fed. Cir. 2014)                                                            |

| <ul><li>15</li><li>16</li></ul> | Infineon Techs. v. Volterra Semiconductor,<br>No. 11-cv-6239-MMC, 2012 U.S. Dist. LEXIS 146499 (N.D. Cal. Oct. 9, 2012)10          |

| 17<br>18                        | InterTrust Techs. Corp. v. Microsoft Corp.,<br>No. C 01-1640-SBA, 2003 WL 23120174 (N.D. Cal. Dec. 1, 2003)9                       |

| 19                              | MEMC Elec. Materials, Inc. v. Mitsubishi Materials Silicon Corp., 420 F.3d 1369 (Fed. Cir. 2005)14                                 |

| <ul><li>20</li><li>21</li></ul> | Microsoft Corp. v. AT & T Corp.,<br>550 U.S. 437 (2007)14                                                                          |

| 22<br>23                        | Shared Memory Graphics LLC v. Apple, Inc.,<br>812 F.Supp.2d 1022 (N.D. Cal. 2010)                                                  |

| 24                              | Silicon Labs., Inc. v. Cresta Tech. Corp.,<br>No. 5:14-cv-03227-PSG, 2015 WL 846679 (N.D. Cal. Feb. 25, 2015)                      |

| <ul><li>25</li><li>26</li></ul> | Solannex, Inc. v. MiaSole, Inc.,<br>2013 WL 1701062 (N.D. Cal. April 18, 2013)10                                                   |

| 27                              | Technology Properties Limited LLC, et al. v. LG Electronics Co., LTD.,  Case No. Case No. 3:12-cv-03877-VC (PSG)                   |

| 28                              |                                                                                                                                    |

| 1  | Statutes           |

|----|--------------------|

| 2  | 35 U.S.C. § 154(c) |

| 3  | 35 U.S.C. § 271(a) |

| 4  | Other Authorities  |

| 5  | Local Rule 3-1(c)  |

| 6  |                    |

| 7  |                    |

| 8  |                    |

| 9  |                    |

| 10 |                    |

| 11 |                    |

| 12 |                    |

| 13 |                    |

| 14 |                    |

| 15 |                    |

| 16 |                    |

| 17 |                    |

| 18 |                    |

| 19 |                    |

| 20 |                    |

| 21 |                    |

| 22 |                    |

| 23 |                    |

| 24 |                    |

| 25 |                    |

| 26 |                    |

| 27 |                    |

| 28 |                    |

2 3

4

5

6

7 8

9

10

11 12

13

14 15

16

17

18 19

20

21 22

23

24

25 26

27

28

### **NOTICE OF MOTION AND MOTION**

TO THE COURT AND ALL COUNSEL OF RECORD:

NOTICE IS HEREBY GIVEN that on August 11, 2015, at 10:00 a.m., or as soon thereafter as counsel may be heard in Courtroom 5 of the above-titled court, located at 280 S. 1st St, San Jose, CA 95113, Defendants LG Electronics, Inc. and LG Electronics U.S.A., Inc. (collectively "LG") will and hereby do move the Court for an order striking Plaintiffs Technology Properties Limited LLC, Phoenix Digital Solutions LLC, and Patriot Scientific Corporation (collectively "Plaintiffs")' Patent L.R. 3-1 Disclosure of Asserted Claims and Infringement Contentions or, in the alternative, an order compelling Plaintiffs to provide supplemental infringement contentions that comply with Patent L.R. 3-1.

This motion is based upon this notice, the accompanying memorandum of points and authorities, the accompanying declaration of Olga May, all pleadings, papers and records on file in this action, and such oral argument as may be presented before or at the hearing in this matter.

#### STATEMENT OF REQUESTED RELIEF

LG requests that the Court strike Plaintiffs' January 20, 2015 Disclosure of Asserted Claims and Infringement Contentions in its entirety for failure to comply with Patent Local Rule 3-1.

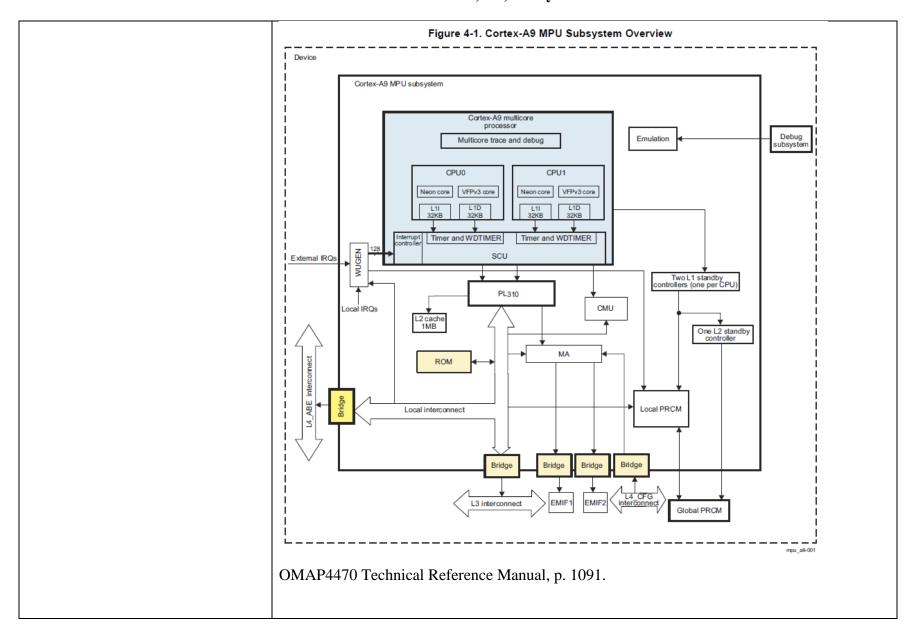

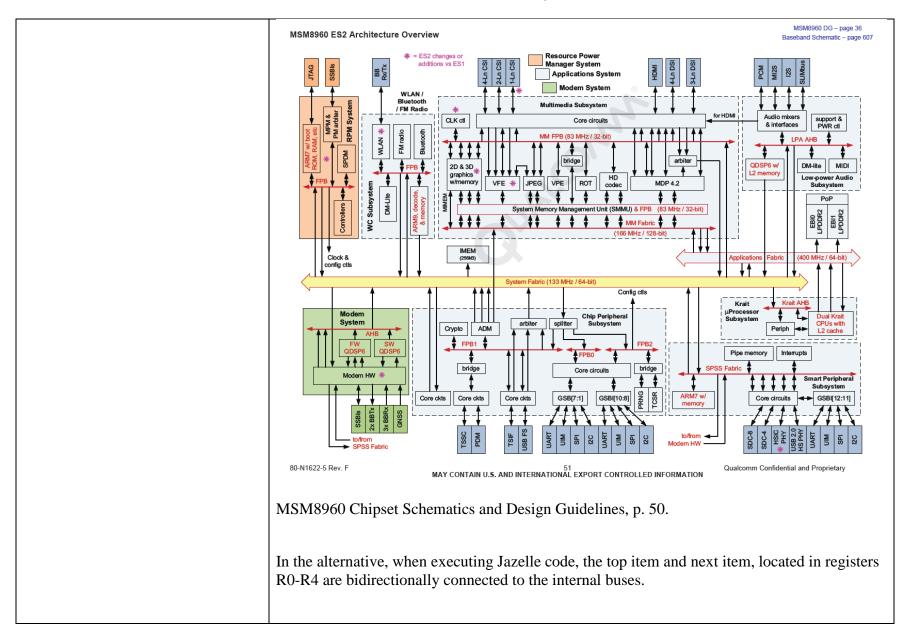

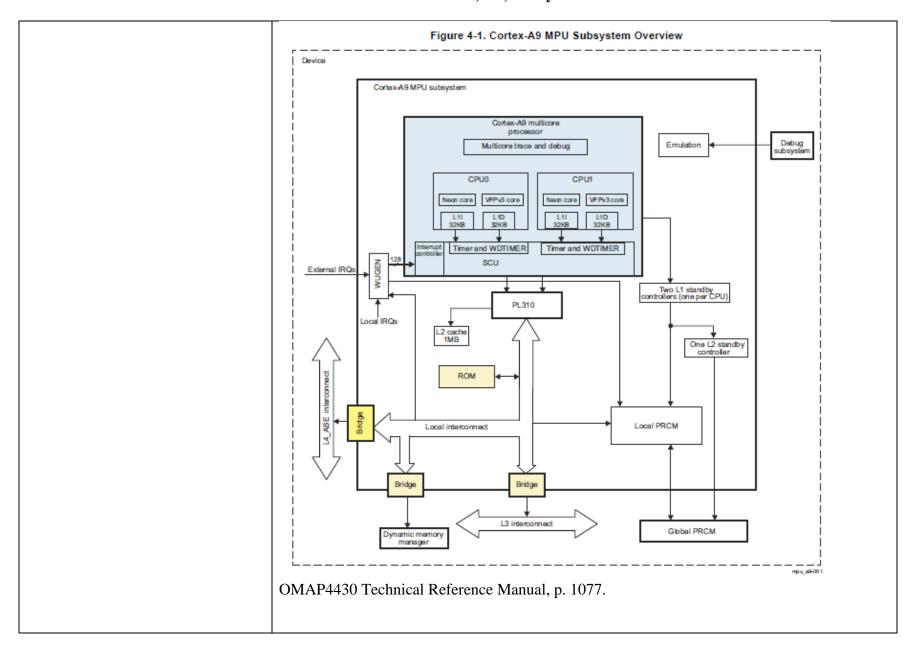

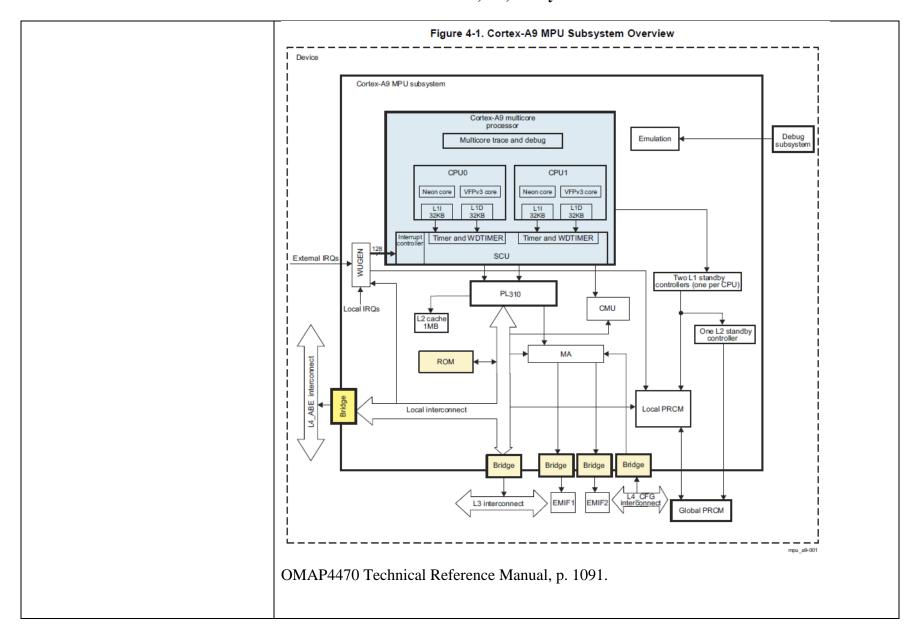

In the alternative, and to the extent the Court permits Plaintiffs to serve supplemental infringement contentions, LG requests that the supplemental Infringement Contentions: (a) be limited to the accused LG products that were previously identified in Table A.6 of Exhibit A to Plaintiffs' January 20, 2015 Infringement Contentions and that include one of the following processors: Qualcomm MSM8960, Qualcomm MSM8660, Qualcomm MSM8260, Qualcomm MSM7227, TI OMAP4430, TI OMAP4460, or TI OMAP4470; (b) identify specifically where each limitation of each asserted claim is found within each accused LG product, including, at a minimum, providing a separate claim chart for each of the above seven identified microprocessors; and (c) exclude all other products (identified in Table A.6 of Exhibit A or otherwise) from the scope of this case for all purposes.

### MEMORANDUM OF POINTS AND AUTHORITIES

#### I. INTRODUCTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

Plaintiffs' Disclosure of Asserted Claims and Infringement Contentions served on January 20, 2015 ("Infringement Contentions") should be stricken for failure to comply with the specificity requirement of Patent Local Rule 3-1 to identify where each element of each asserted claim is found in each accused instrumentality.

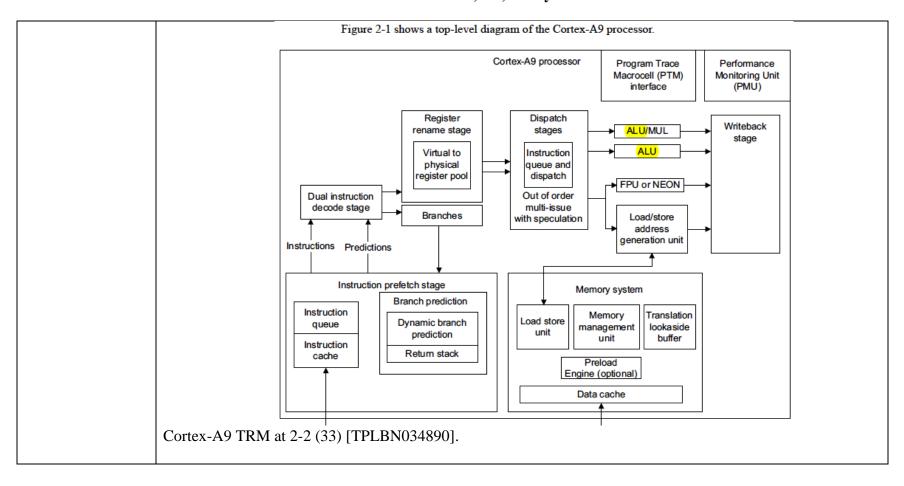

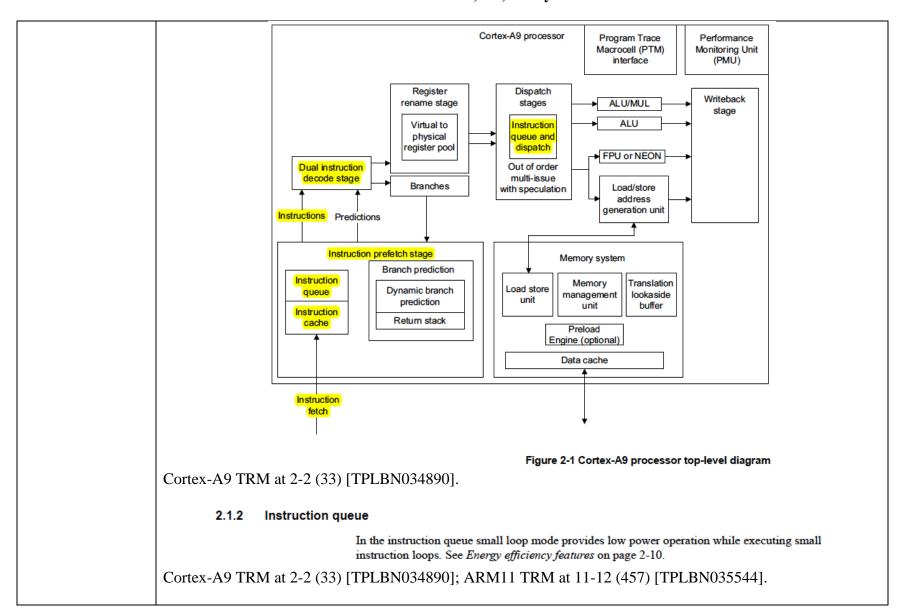

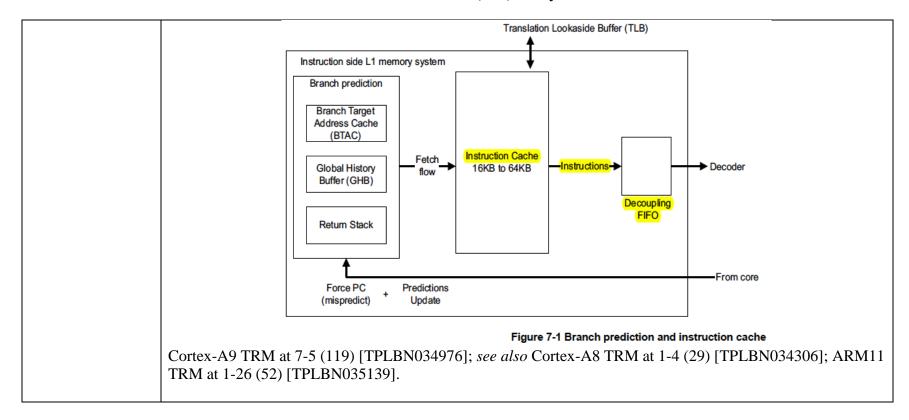

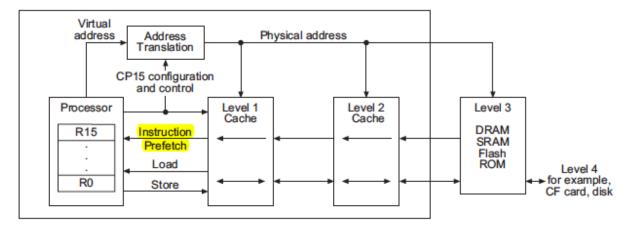

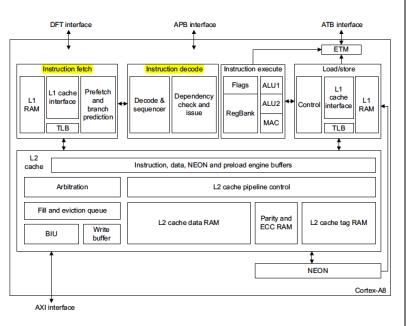

Plaintiffs' Infringement Contentions purport to accuse 437 LG products, including mobile phones, tablets, TVs, and Blu-ray players. But Plaintiffs' infringement charts barely mention only two of these products without charting either one through the claim elements of any single claim. Instead, the charts focus on accusing the microprocessors contained within the accused LG end products. Plaintiffs' list of the accused products and processors, produced as a separate attachment to the charts, lists a profusion of processors of different makes and models by more than half a dozen different manufacturers. For this indiscriminate list of processors, Plaintiffs produced only three charts, one for each asserted patent. Each chart lumps "each Accused Microprocessor in each Accused Product" together and purports to accuse them all at once without providing the requisite specific identification as to where each claim element is found in every individual accused processor. Although the charts reference seven specific processors and provide some evidentiary support as to those, the charts fail to identify any basis for why the rest of the processors can be accused along with these seven or be in any way represented by them. Indeed, the most Plaintiffs endeavored was to rely on impermissible conclusory assertions based on "information and belief." Such conclusory allegations do not approach the specificity requirement of Rule 3-1 and should be stricken.

The allegations with respect to the seven charted processors, although better supported, also fail to meet the specificity requirements. None of these processors are charted through an entire claim and also rely on conclusory allegations of "information and belief," unsupported understanding of one of ordinary skill in the art, and on generic descriptions of technology.

1

5

4

7 8

6

9 10

11 12

13

14

15

16

17 18

19

20

21

22

II. FACTUAL BACKGROUND

24

23

25

26

27

28

2012 and June 25, 2013 expirations of the '749 and '890 Patents. Because an infringement claim can only be asserted for the patent's term, contentions as to the products released after the expiration of the '749 and '890 Patents should be stricken.

Further, a number of the accused products were released after the respective August 8,

Finally, a large number of the accused products LG has never made, sold, used, or imported into the United States. Because the general rule under United States patent law is that no infringement occurs when a patented product is made and sold in a country other than the United States, all contentions as to such products should be stricken.

Therefore, LG respectfully requests that Plaintiffs' Infringement Contentions be stricken in their entirety. Alternatively, if this Court is inclined to grant Plaintiffs leave to supplement, LG requests that any supplementation be limited to the LG products already included on Plaintiffs' list of the accused products, sold in the U.S., and containing the seven charted processors.

Any broader supplementation would result in undue expansion of the case, substantially prejudice LG, and give Plaintiffs an unfair second bite at the apple. Plaintiffs produced their Infringement Contentions two and a half years after this case was filed (this case was stayed while the parties litigated one of the asserted patents—the '336 Patent—in a parallel ITC investigation). Fact discovery will close on September 8, 2015. LG already produced its invalidity contentions on April 21, 2015. Restarting and expanding the case three months before the end of fact discovery and after service of invalidity contentions based in part on Plaintiffs' infringement positions will significantly impair LG's ability to prepare its defenses. Accordingly, LG respectfully requests that any permitted supplementation be limited to the already identified LG products containing the seven charted processors.

#### A. Case History

Plaintiffs filed this case against LG on July 24, 2012, alleging infringement of three patents: U.S. Patent Nos. 5,809,336 ("the '336 Patent"), 5,440,749 ("the '749 Patent") and 5,530,890 ("the '890 Patent") (collectively the "Patents-in-Suit"). [Dkt. No. 1.] Concurrently,

Plaintiffs filed seven more cases ("the related cases") asserting the same patents against a total of eight groups of defendants.

The Patents-in-Suit are generally directed to processor design and operation. The LG accused products include mobile phones, tablets, TVs, and Blu-ray players.

On October 2, 2012, the Court stayed this case and the related cases pending the resolution of a pending U.S. International Trade Commission investigation filed by Plaintiffs against LG (and a number of other respondents) alleging infringement of the '336 Patent (Inv. No. 337-TA-853, the "853 Investigation"). [Dkt. No. 12.] The '749 and '890 Patents were not at issue in the 853 Investigation. On September 6, 2013, the Administrative Law Judge issued an Initial Determination in the 853 Investigation finding that LG's products did not infringe the '336 Patent. [Dkt. No. 20 at 5-6]. On February 19, 2014, the full Commission issued a notice affirming the ALJ's non-infringement findings and terminating the investigation. Plaintiffs did not appeal the Commission's final determination.

After the stay in the present case was lifted, on November 20, 2014, this Court issued a scheduling order setting the deadline for Plaintiffs' Rule 3-1 Infringement Contentions for January 20, 2015. [Dkt. No. 40.]

#### B. Deficiencies in Plaintiffs' Infringement Contentions

On January 20, 2015—nearly two and a half years after filing their Complaint—Plaintiffs served their Infringement Contentions. The Infringement Contentions purported to accuse 437 LG products—mobile phones, tablets, TVs and Blu-ray players—of infringing all of the asserted claims of each of the '336, '749 and '890 Patents. [May Decl., Exs. A-B, G-1, G-2, G-3.]

Plaintiffs' Infringement Contentions consist of:

- (1) a cover pleading that sets forth infringement allegations with respect to all eight related cases [May Decl., Ex. B];

- (2) "Exhibit A" to the cover pleading that purports to list all accused products of all defendants in the eight related cases, including LG [May Decl., Ex. A]; and

| 1  |  |

|----|--|

| 2  |  |

| 3  |  |

| 4  |  |

| 5  |  |

| 6  |  |

| 7  |  |

| 8  |  |

| 9  |  |

| 10 |  |

| 11 |  |

| 12 |  |

| 13 |  |

| 14 |  |

| 15 |  |

| 16 |  |

| 17 |  |

| 18 |  |

| 19 |  |

| 20 |  |

| 21 |  |

| 22 |  |

| 23 |  |

| 24 |  |

| 25 |  |

| 26 |  |

| 27 |  |

| 28 |  |

(3) three claim charts per case, one for each of the three Patents-in-Suit [May Decl., Exs. G-1, G-2, G-3].

#### 1. Cover Pleading

The cover pleading states that the three claim charts identify "where each element of each asserted claim [] may be found within LG's Accused Instrumentalities identified in Ex. A." [May Decl., Ex. B at 8.] The cover pleading also states that "[t]he list of accused instrumentalities in this action includes those listed in Ex. A, and all models thereof." [Id. at 5.]

#### 2. Exhibit A

Exhibit A to Plaintiffs' Infringement Contentions contains eight tables identifying the purportedly accused products of each defendant in the related cases. "Table A.6: LG" of Exhibit A lists the 437 purportedly accused LG products. [May Decl., Ex. A at 56-68.] Of these 437 products, 116 are not identified by name but by what appears to be a part or product number.

Table A.6 has columns for the following information for the products: including "Memory," "Processor," "CPU Core," and "Instruction Set(s)." [*Id.*] However, the table fails to identify this information for each product. For example, for 118 of the accused products, the "Processor" information is missing.

The table also fails to indicate which products are accused against which patent.

#### 3. Claim Charts

Exhibits G-1, G-2, and G-3 are each a claim chart for a Patent-in-Suit. Of the 437 purportedly accused products, these charts mention a total of two: LG Escape and LG Optimus 9. [May Decl., Ex. G-1 at 1, 19, G-3 at 1 (references to Escape); G-3 at 1 (reference to Optimus).] *The other 435 products are never named.* The two named products are only briefly mentioned in the beginning of a chart and not charted through each element of each asserted claim.

Instead, the charts focus on a handful of processors, referred to as "the Accused Microprocessors," contained within the accused end products. Each chart (using the '336 chart as an example), makes substantially the same statement in the preamble of the first asserted claim:

DEFENDANTS' MOTION TO STRIKE Case No. 3:12-cv-03880-VC

11

12

13 14

15

16 17

18

19 20

22

21

23

24

25

26

27

28

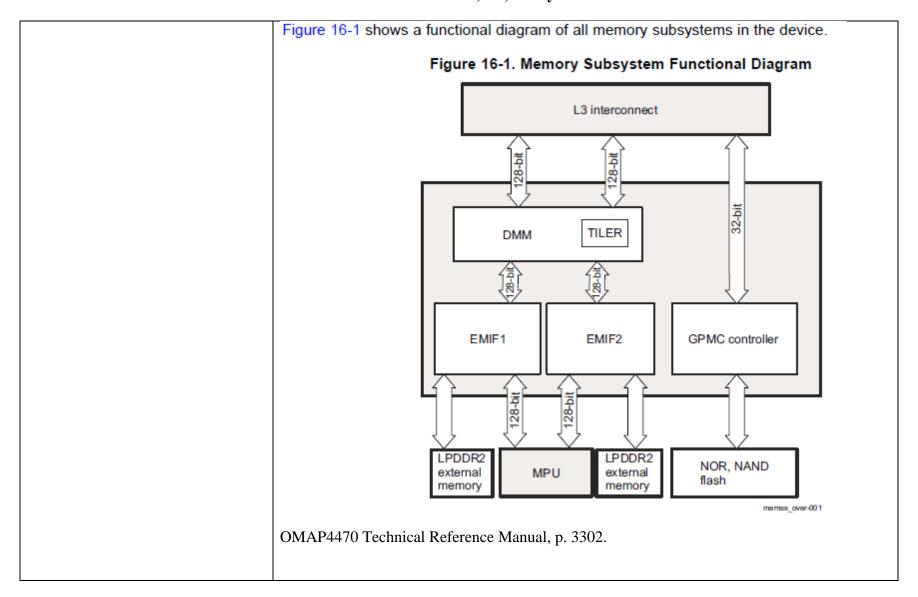

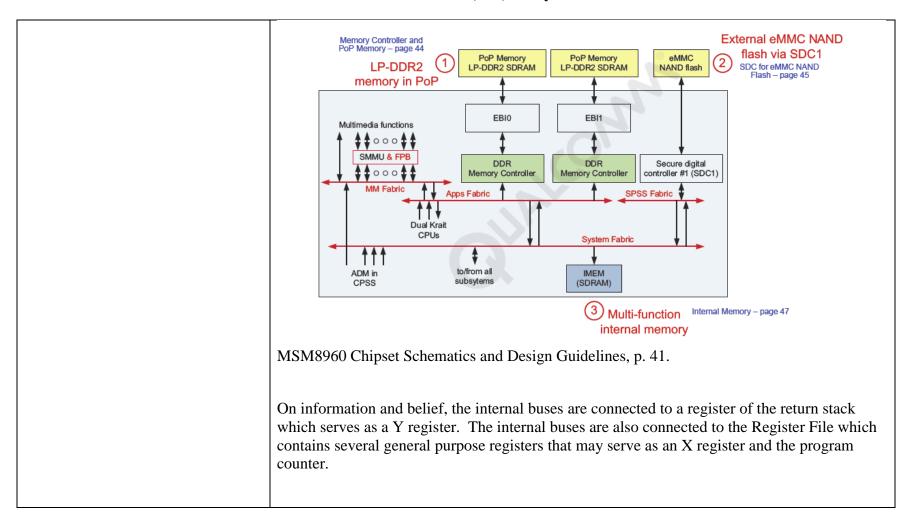

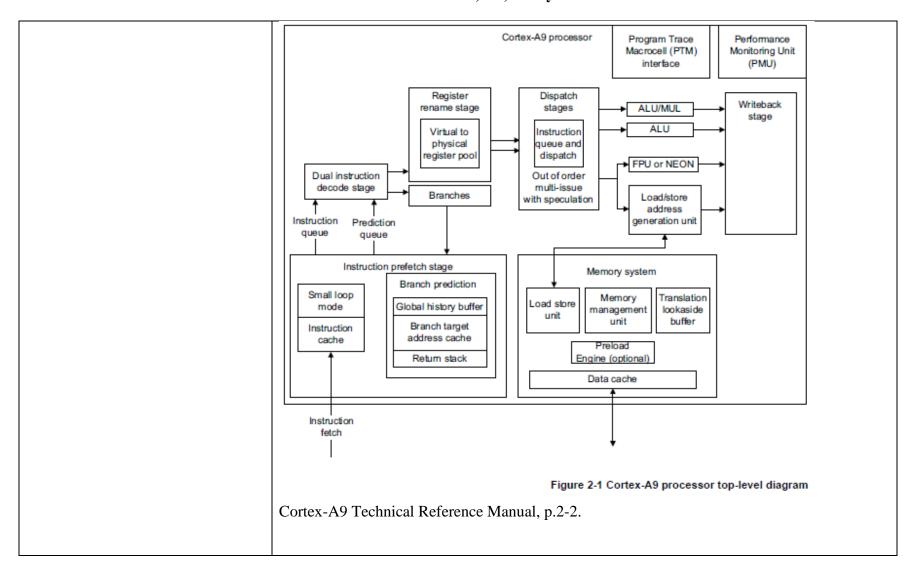

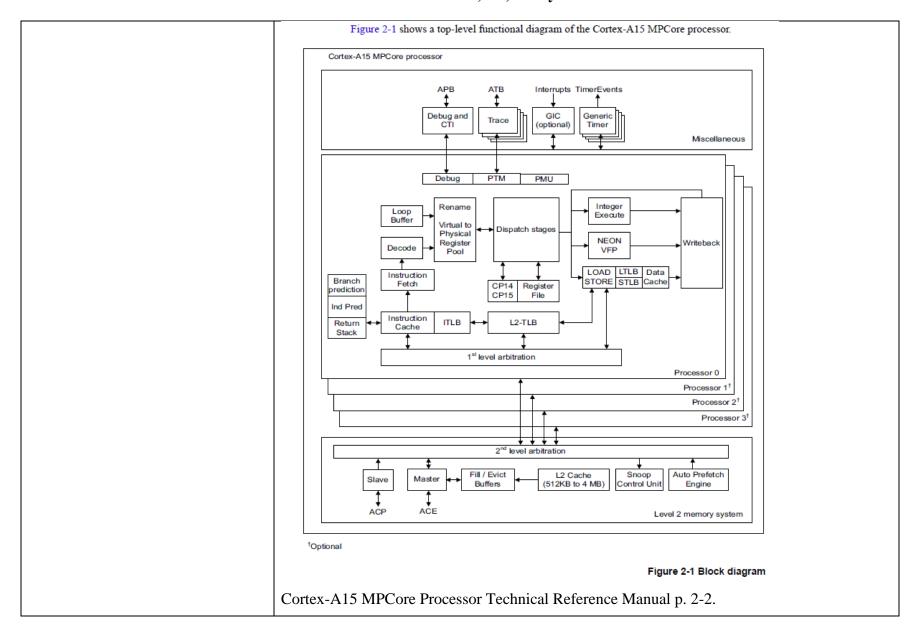

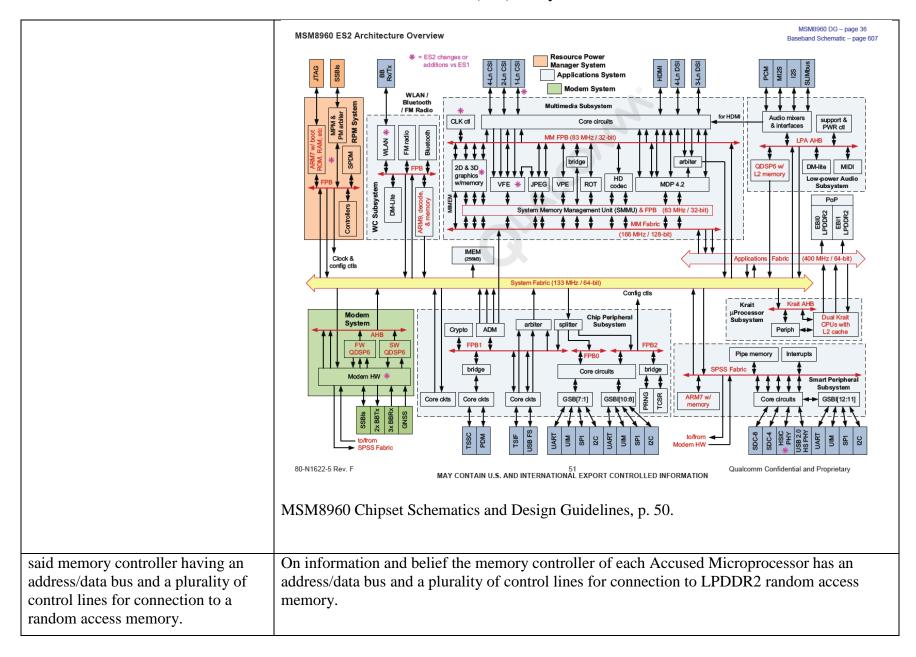

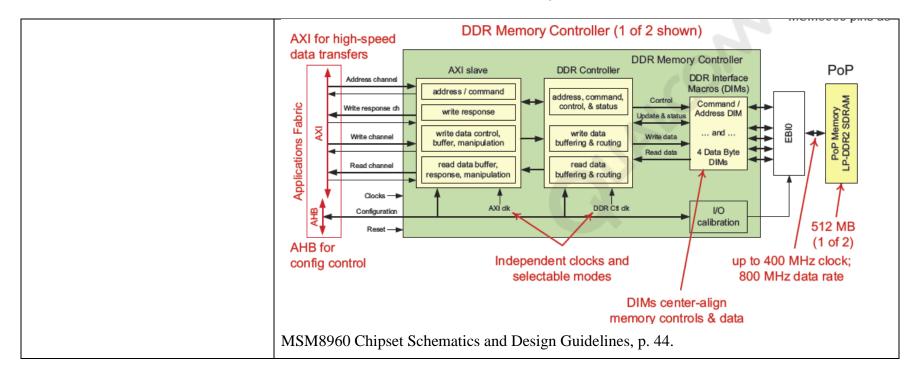

On information and belief, each Accused Product listed in the attached list of Accused Products (Ex. A.6), including phones and televisions, contains a microprocessor ("Accused Microprocessors"). http://www.phonescoop.com/; http://pdadb.net/; http://www.gsmarena.com/; see PDSLG000001-PDSLG000050; see also PDSND077821-PDSND078576 for datasheets identifying microprocessors. <sup>1</sup> For example, the Escape contains a Qualcomm MSM8960L. See Ex. A.6 for listings of microprocessors in the Accused Products with information obtained from http://www.phonescoop.com/: http://pdadb.net/; http://www.gsmarena.com/; see PDSLG000001-PDSLG000050; see also PDSND077821-PDSND078576 for datasheets identifying microprocessors."

[Id., G-1 at 1; see also G-2 at 1, G-3 at 1] (emphasis added).

The chart then broadly accuses "each Accused Microprocessor in each Accused Product" without citing any support or documents for such "each Microprocessor." Instead, the charts mainly refer to the processors in large groups organized not by any relevant functionality but by the manufacturer: for example, ARM, Qualcomm, or Texas Instruments ("TI").

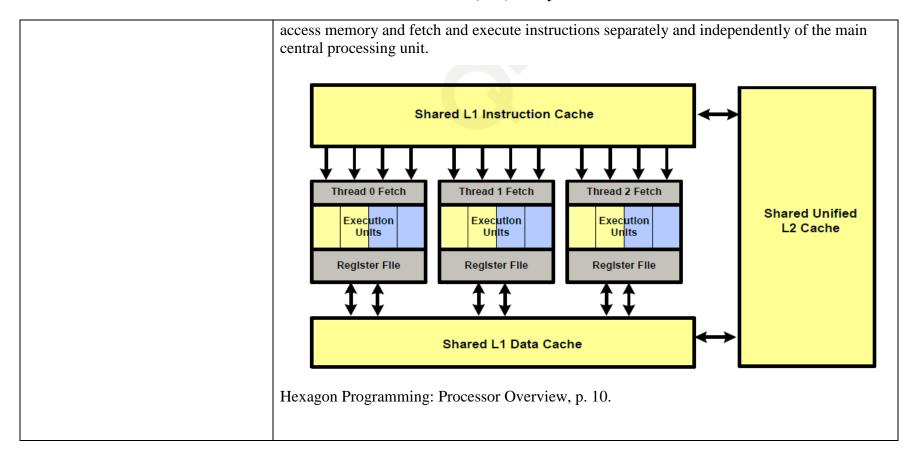

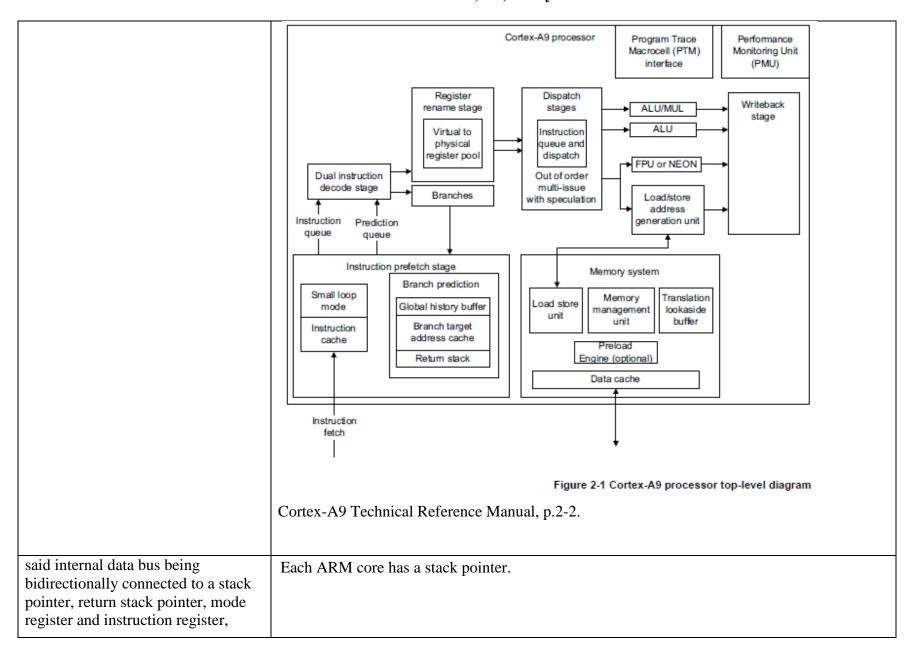

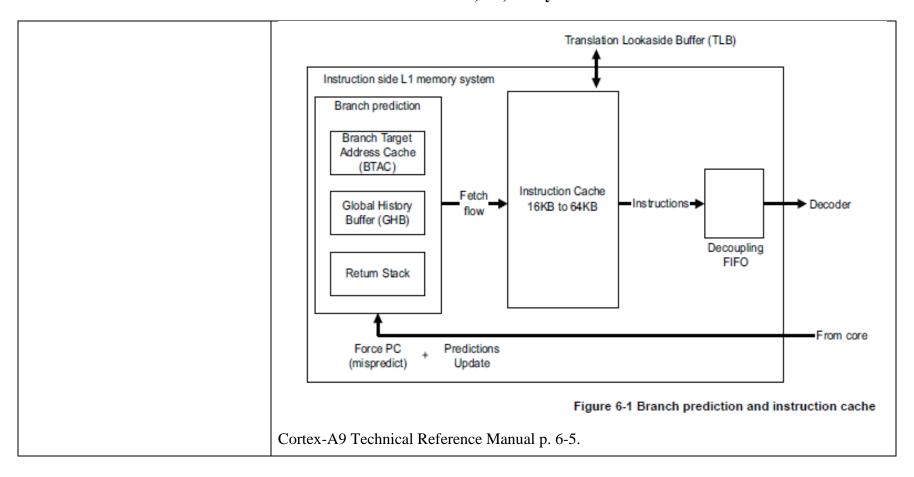

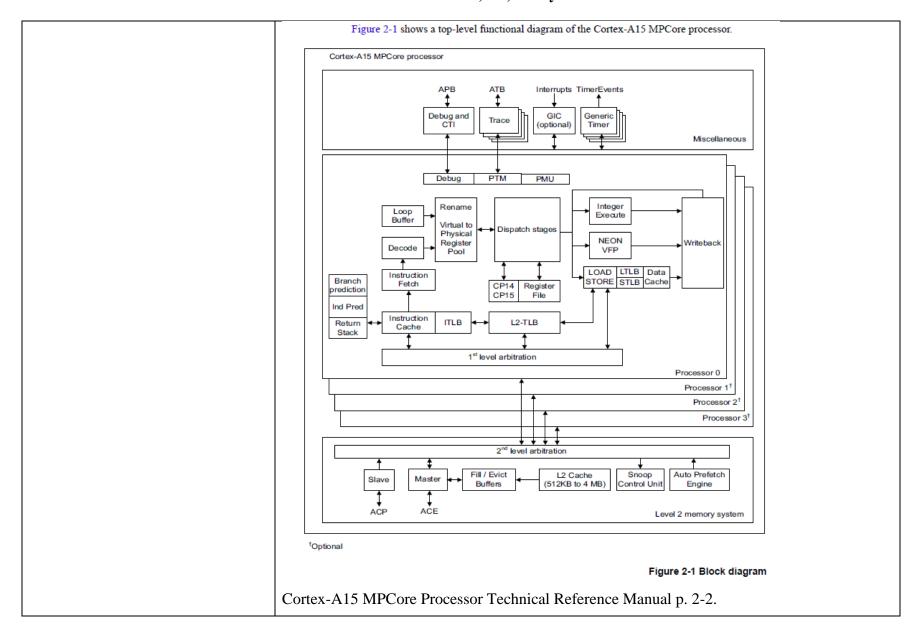

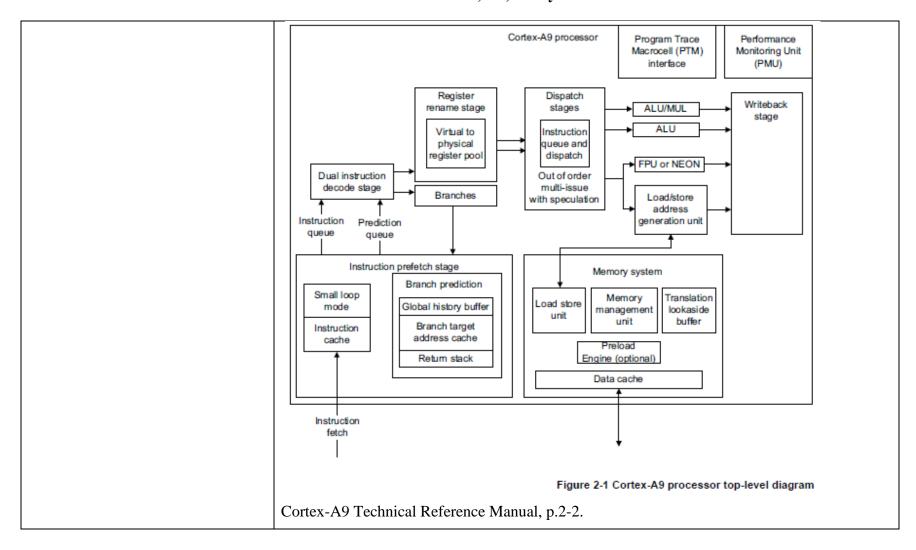

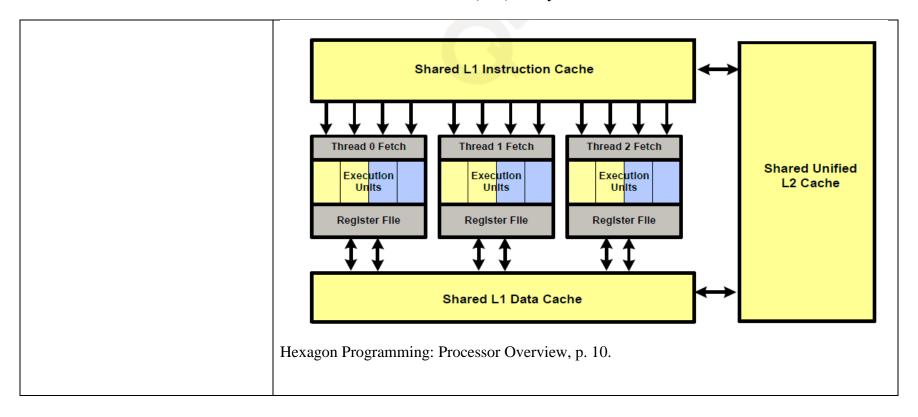

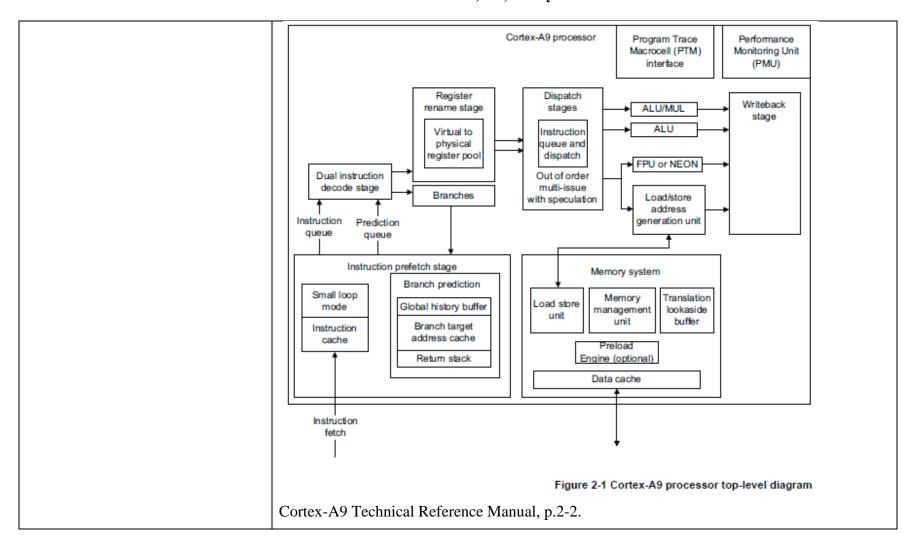

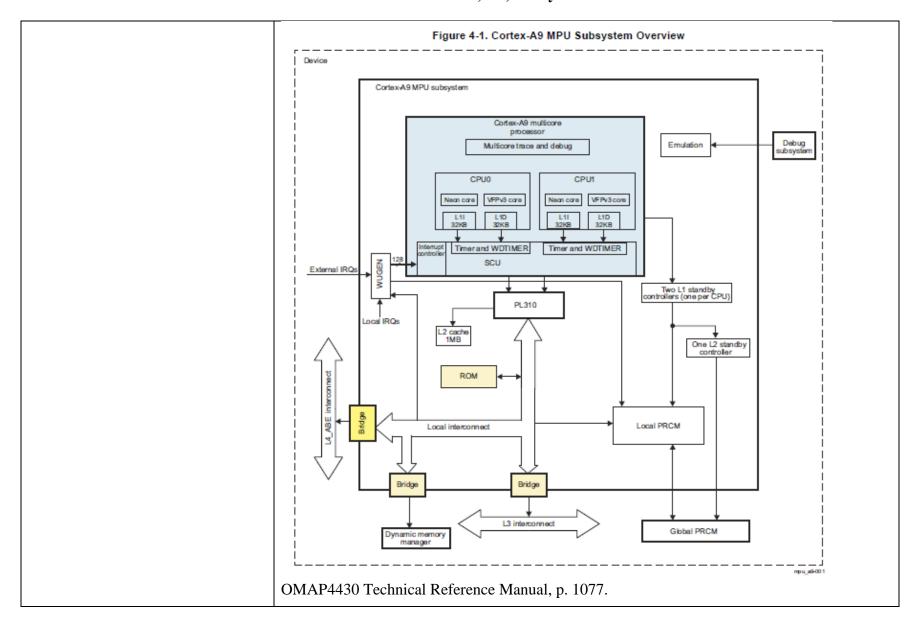

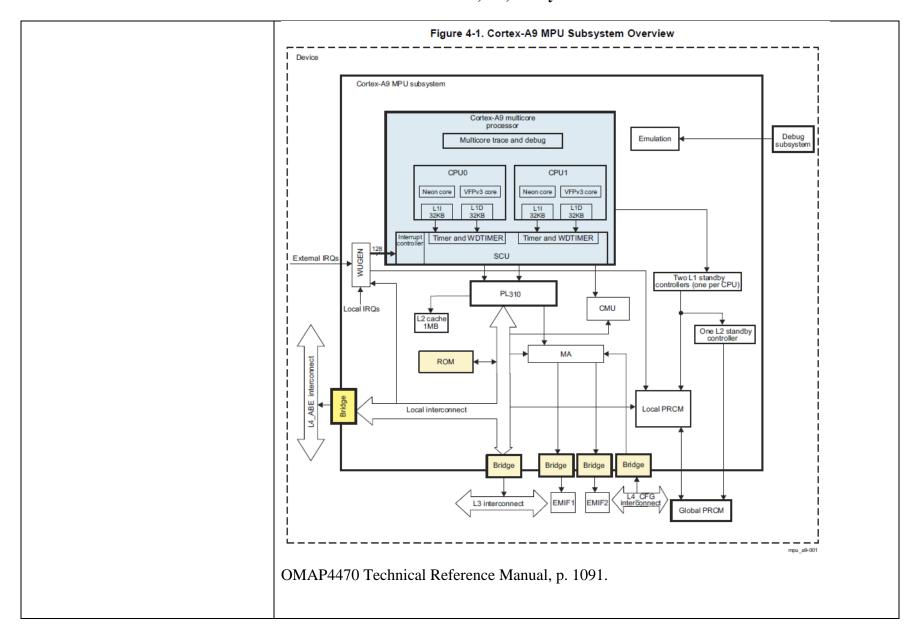

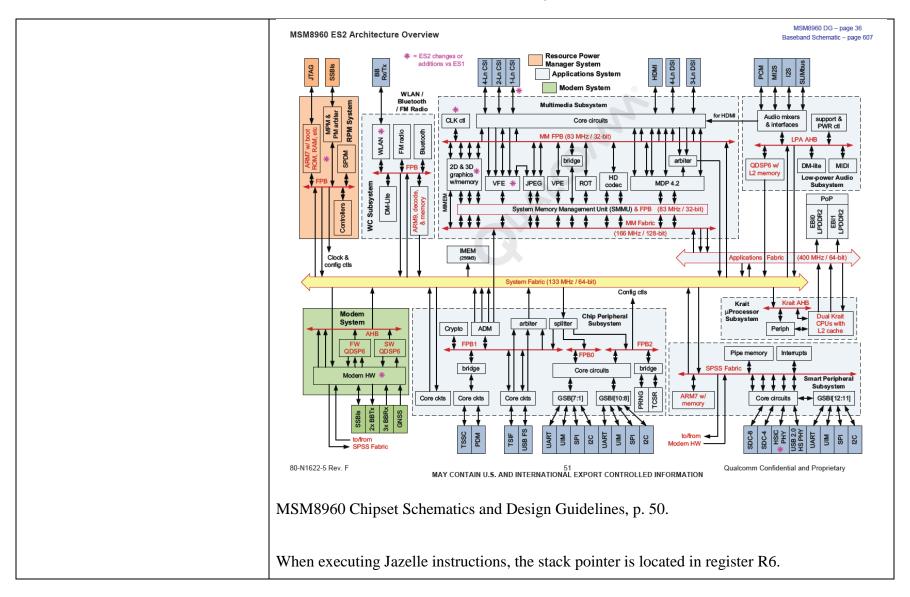

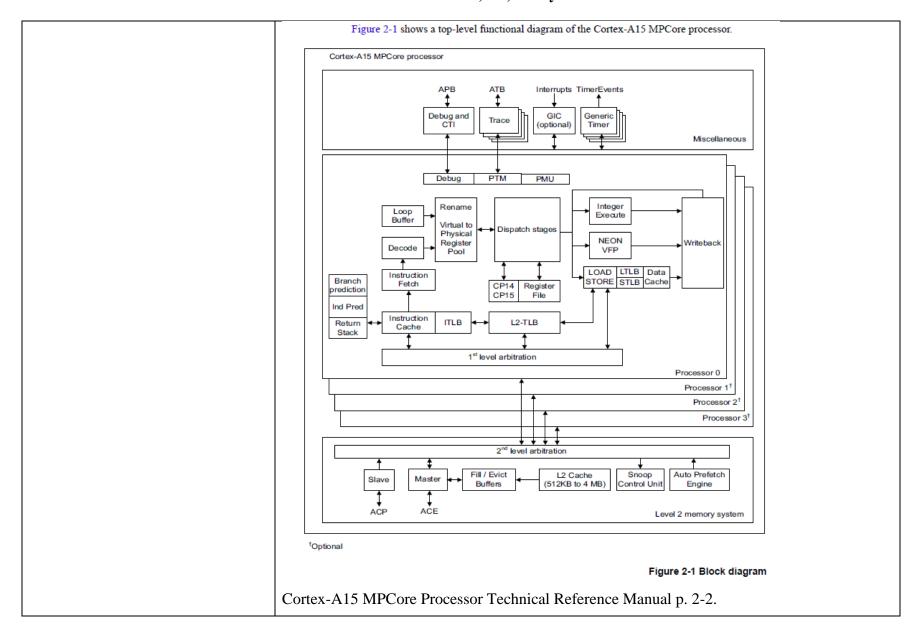

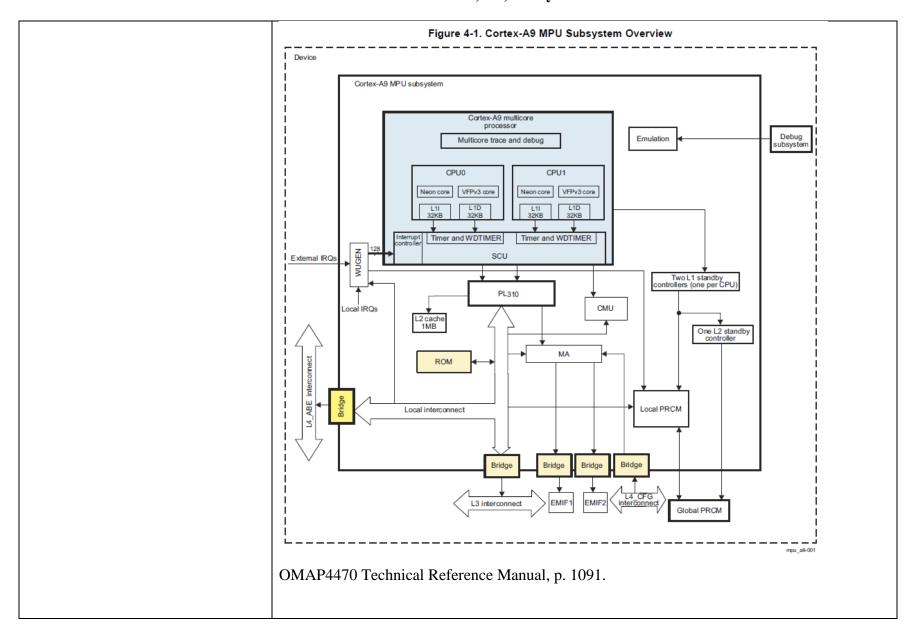

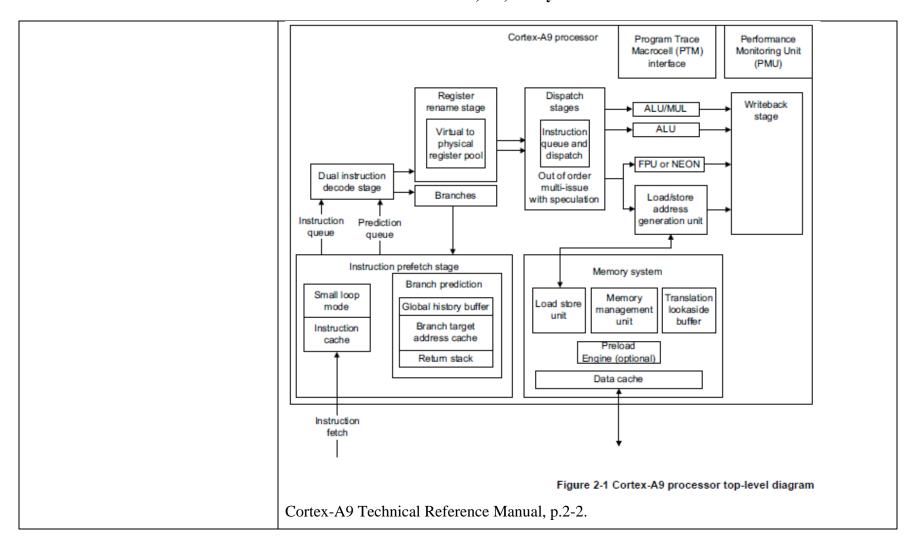

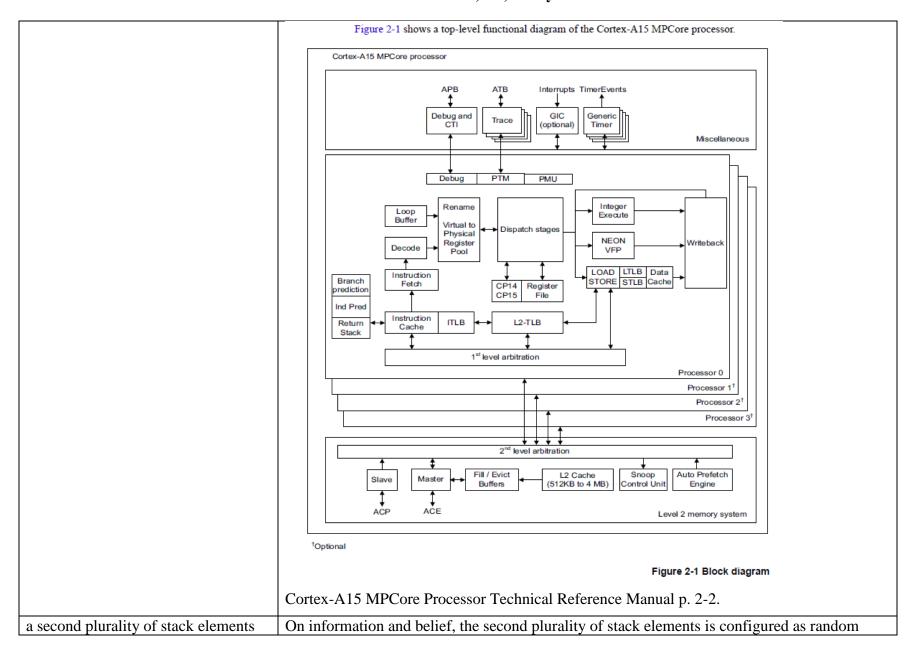

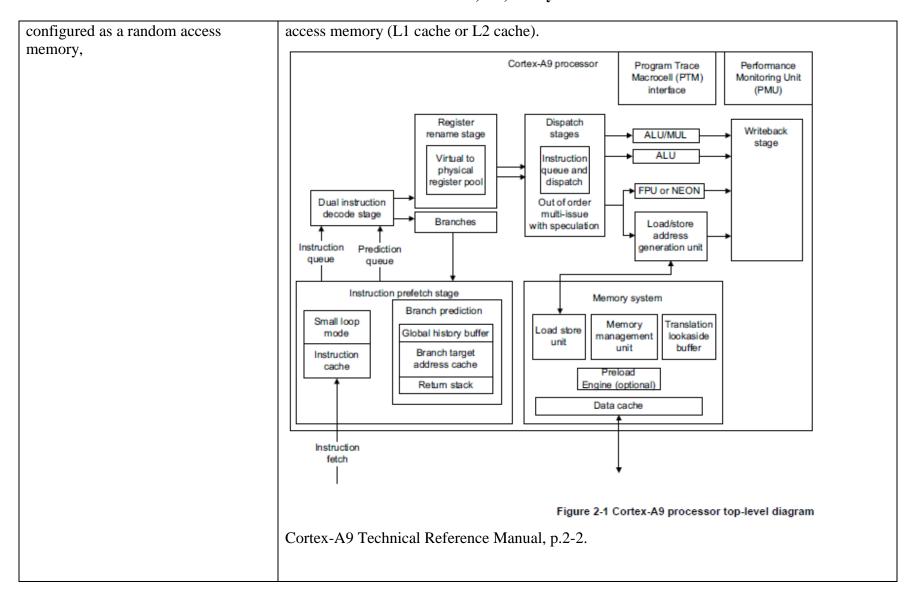

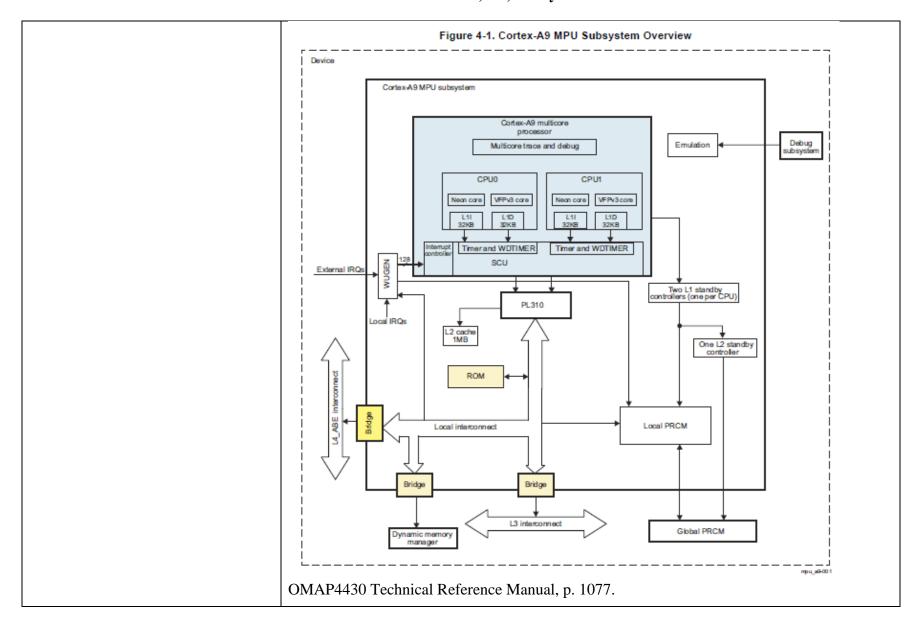

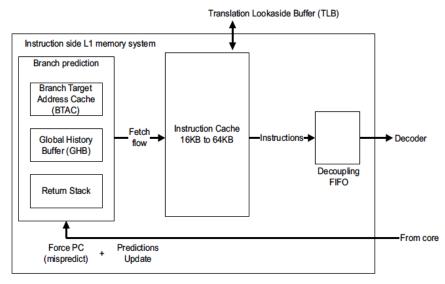

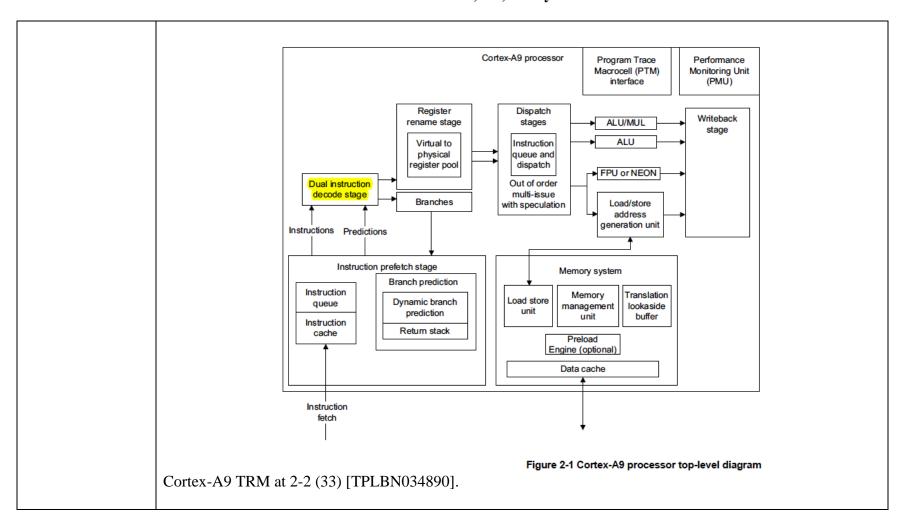

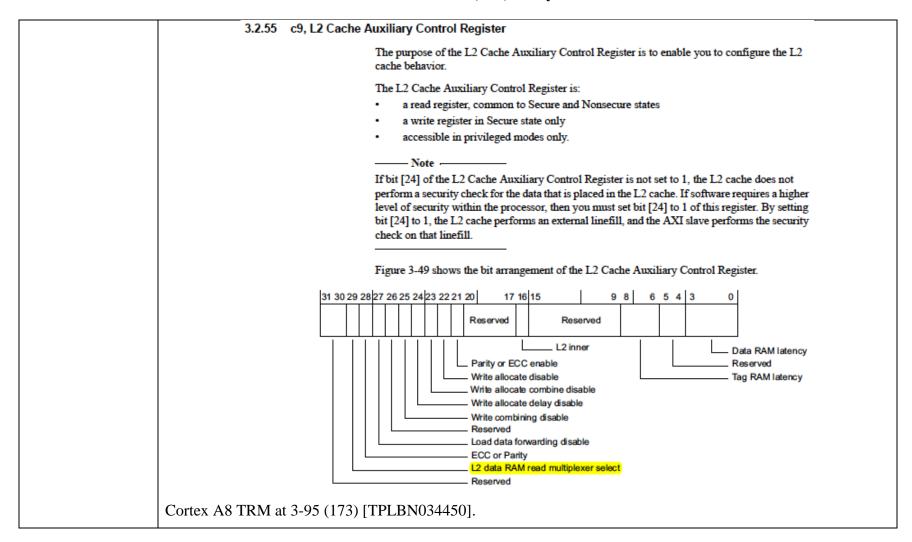

Taking one of those examples, the Infringement Contentions refer to ARM processors as a single undifferentiated group. ARM processors are a large family of processing cores developed over the last thirty years.<sup>2</sup> Even the subset of ARM processing cores allegedly found in the Accused Products contains several different design generations and different members within those generations. TPL does not provide a comparative analysis of any of the relevant characteristics of these different ARM processors. TPL applies the same undifferentiated treatment to TI processors and Qualcomm processors throughout its Infringement Contentions.<sup>3</sup>

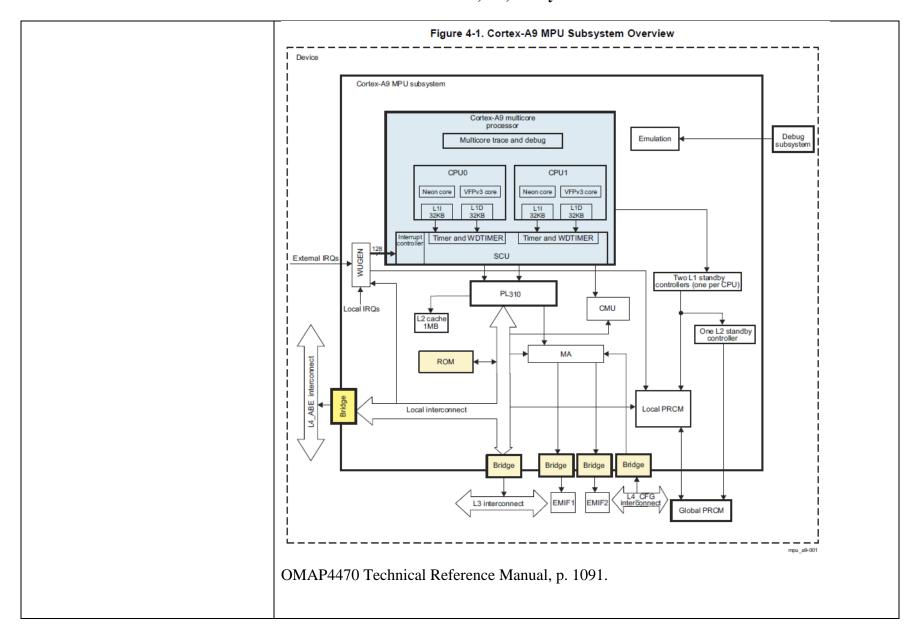

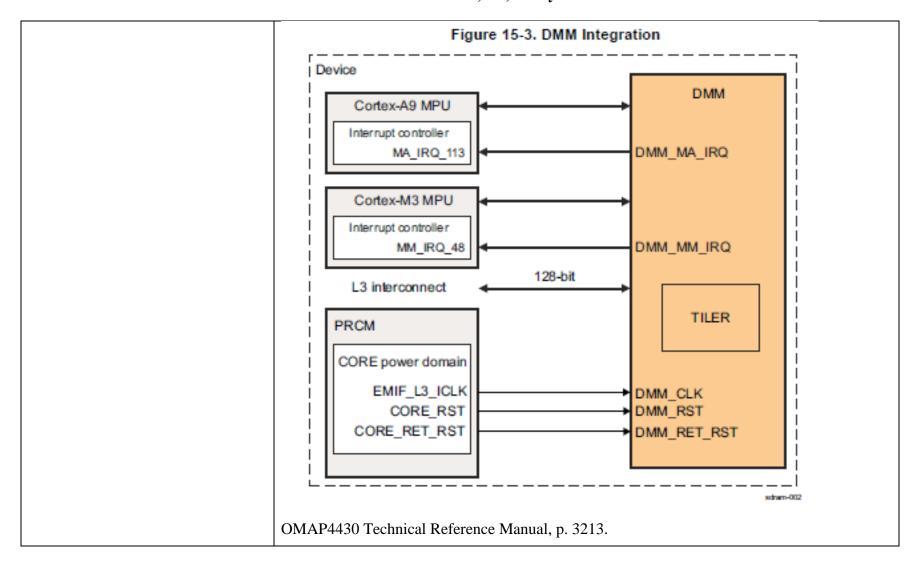

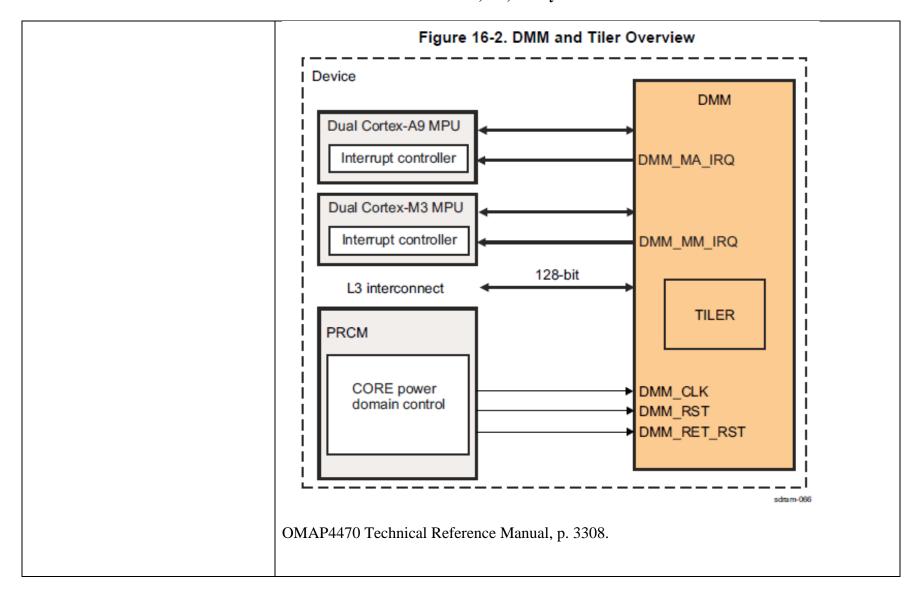

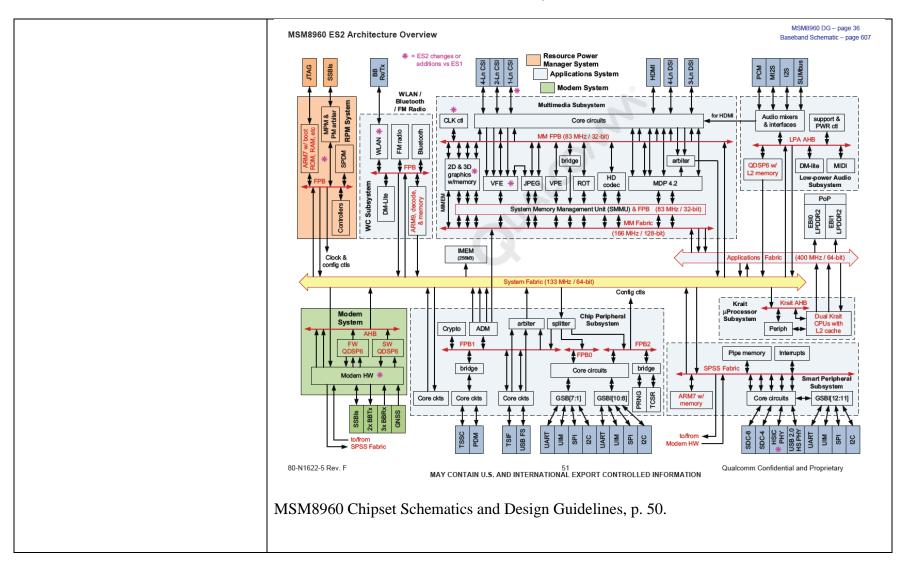

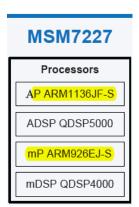

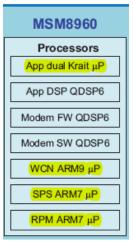

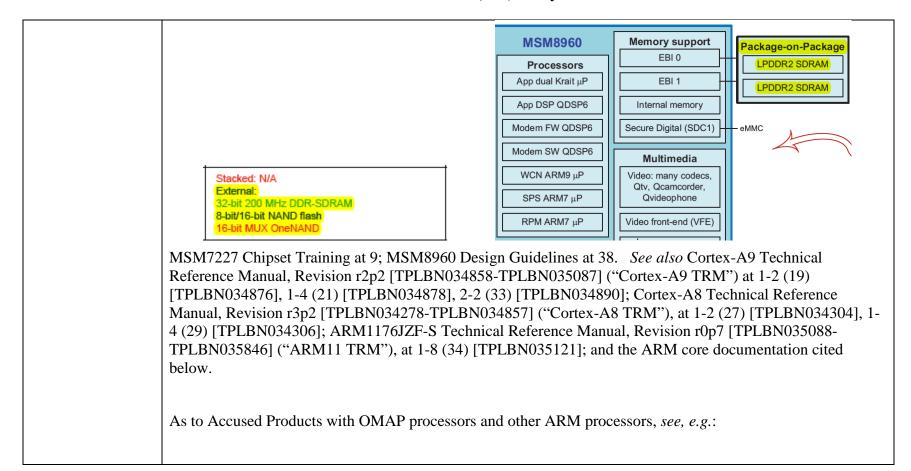

Specific processors are few and referenced only as examples. The charts name a total of seven specific processors used as examples for different claims:

- 1. Qualcomm MSM8960

- 2. Oualcomm MSM8660

- 3. Qualcomm MSM8260

See, e.g., May Decl., Exs. G-2 at 1, 5-6, 10-11, 16, 20-22, 27, 63, 67-68, 72, 78, 82-84, 89, 94-95, 115 ('890 elements 1.b, 1.c, 1.d, 1.e, 1.f, 1.g, 1.h, 1.i, 11.b, 11.c, 11.d, 11.e, 11.f, 11.g, 11.h, 11.i, 11.j and 13.b); and G-3 at 1-2, 4-8, 10-11, 15-16, 24, 46-47, 54-55, 71-72, 74, 89, ('749 elements 1 (preamble), 1.a, 1.b, 1.c, 1.d, 1.e, 1.f, 1.g, 1.i, 1.k, and 9.d). For those claim charts without element labels, the elements are referred to in alphabetical order, starting with "X.a" for the preamble.

<sup>&</sup>lt;sup>2</sup> See generally http://www.arm.com/about/company-profile/milestones.php.

<sup>&</sup>lt;sup>3</sup> See, e.g., May Decl., Exs. G-1 at 12-15, 20, 22 ('336 elements 6.d and 9.b); G-2 at 51, 117 ('890 elements 7.b and 17.b); and G-3 at 2-11, 15-16, 24, 45-47, 54, 70 ('749 elements 1.a, 1.b, 1.c, 1.d, 1.e, 1.f, 1.g, and 1.i).

- 4. Qualcomm MSM7227

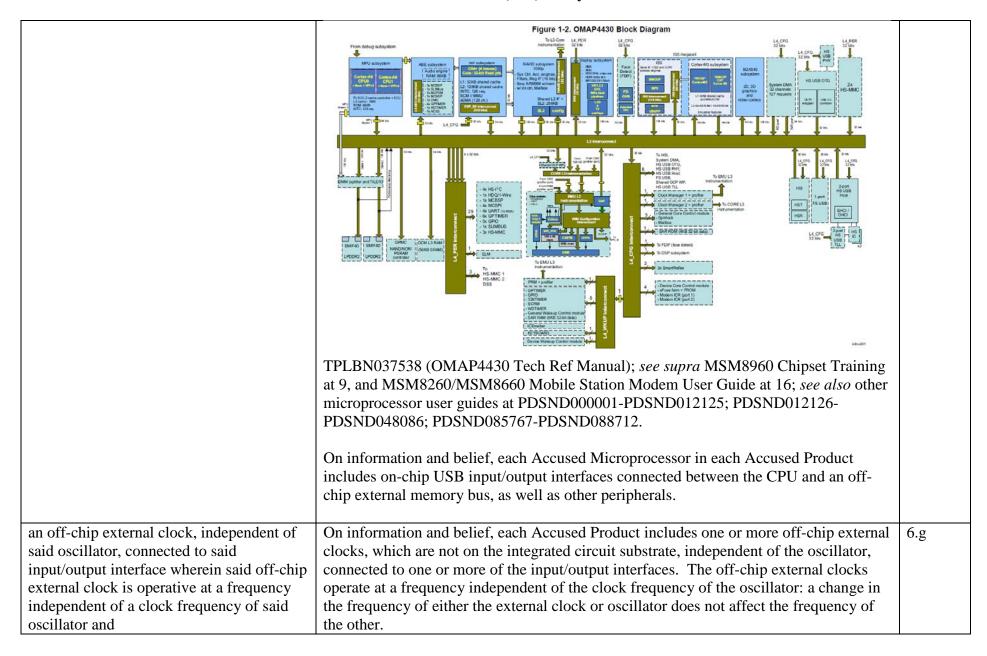

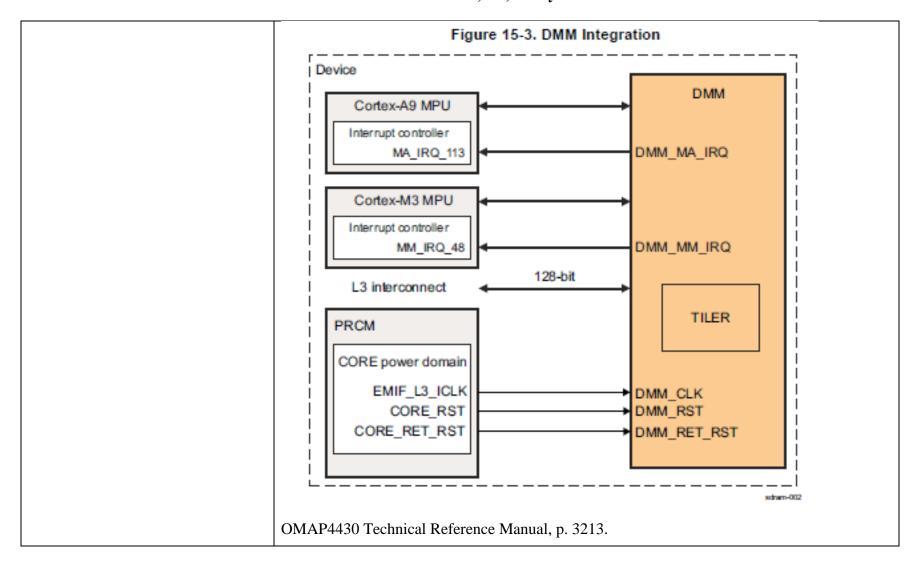

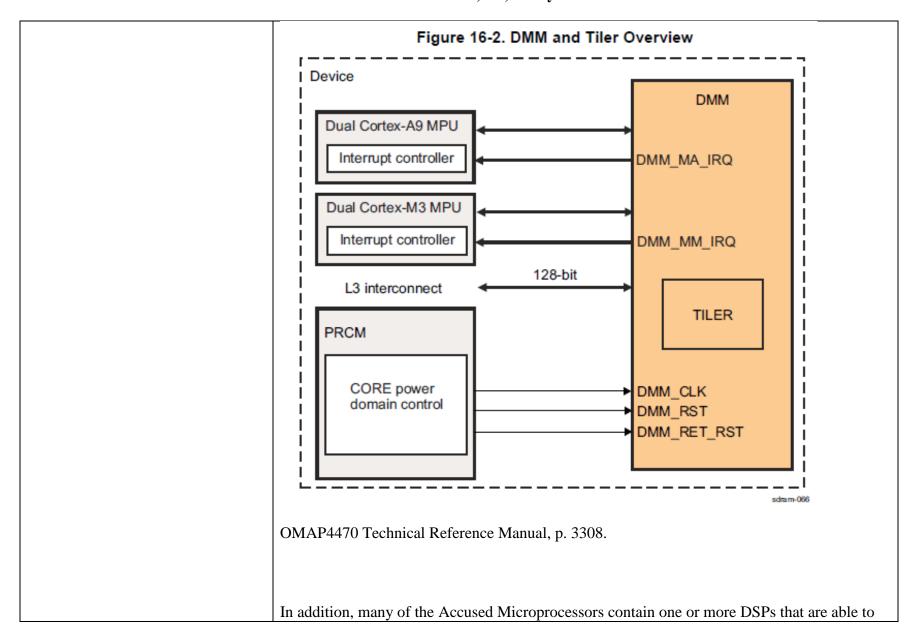

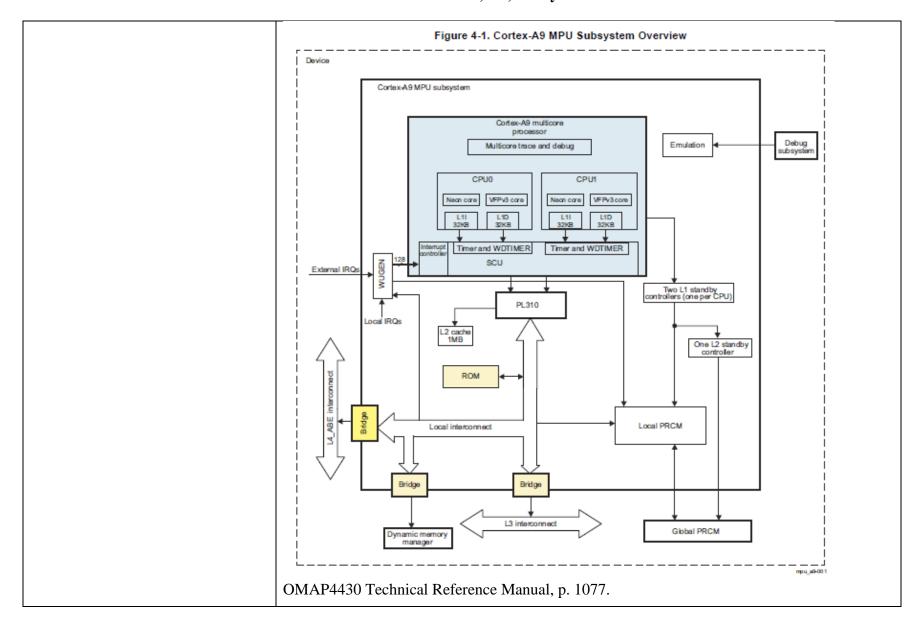

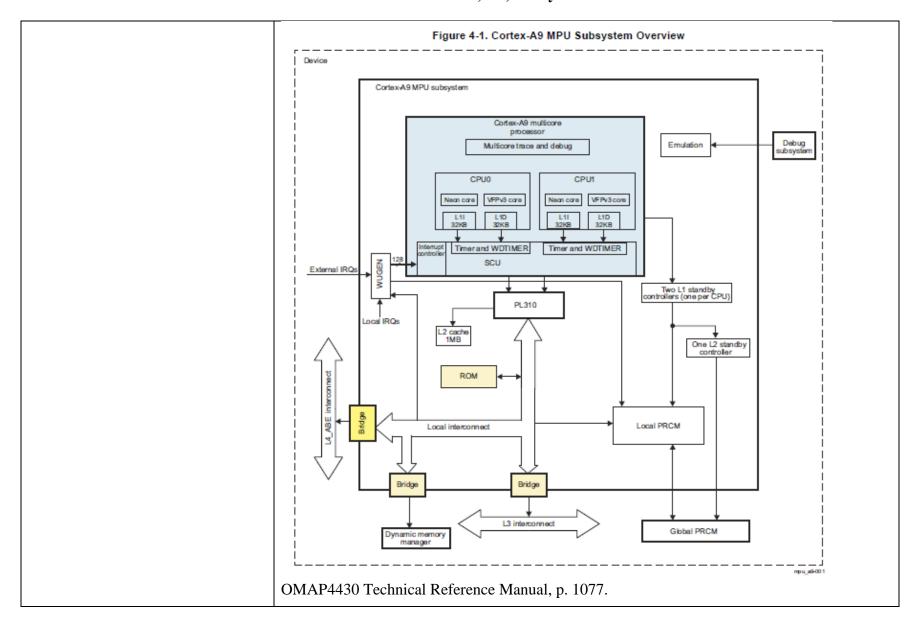

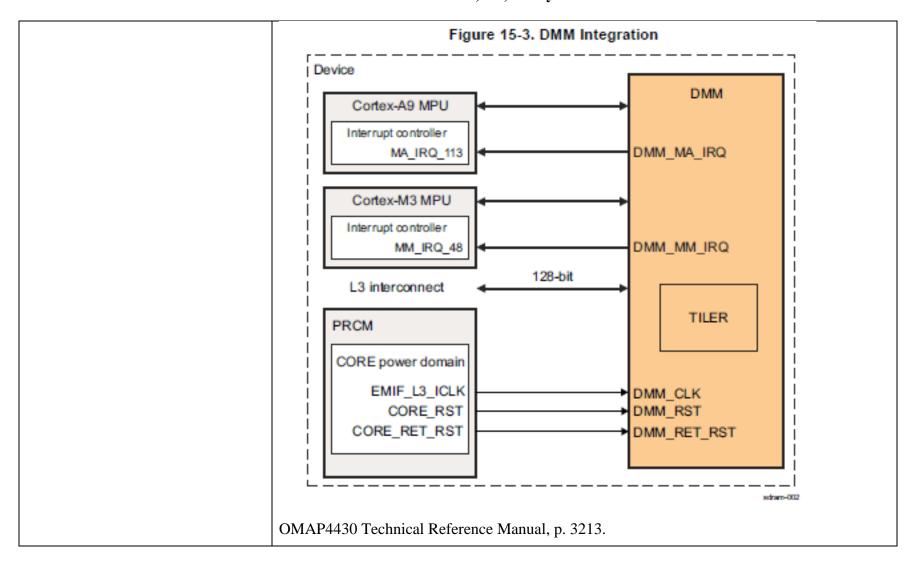

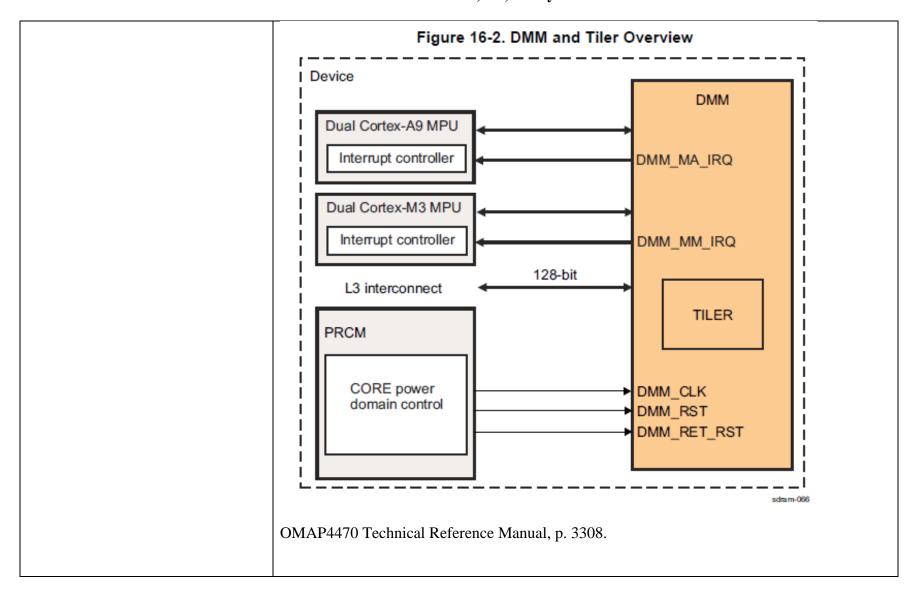

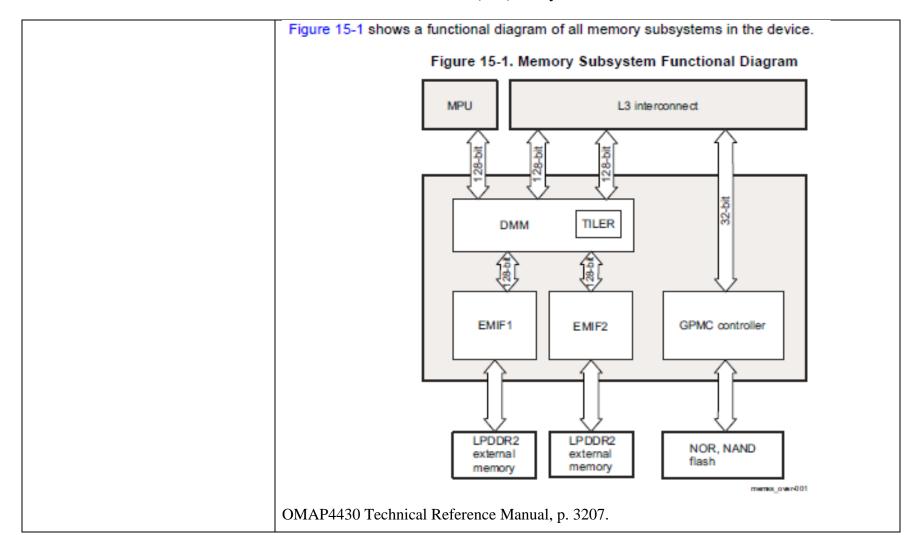

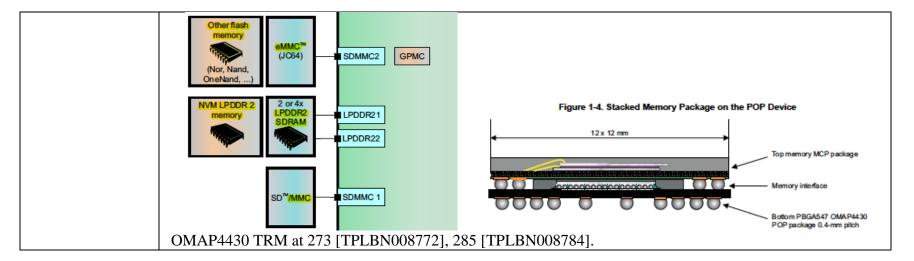

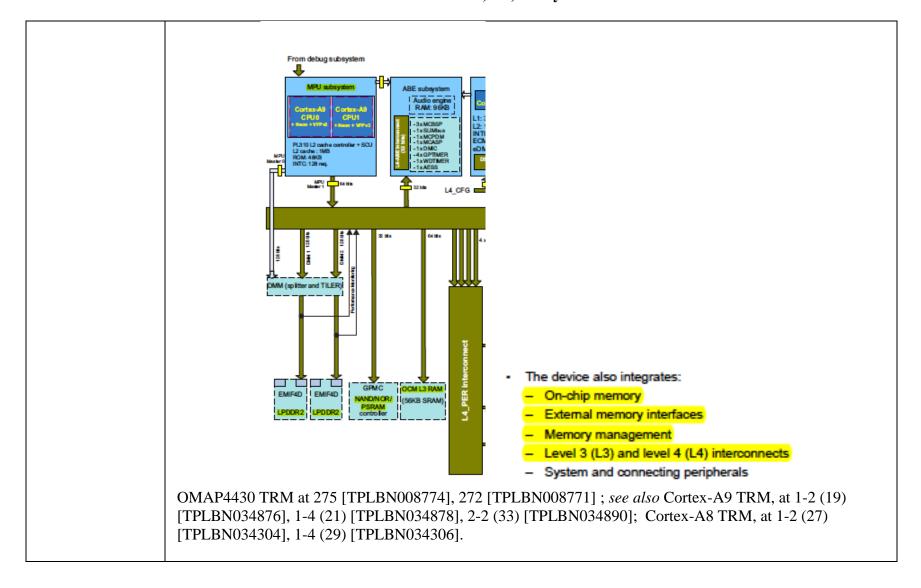

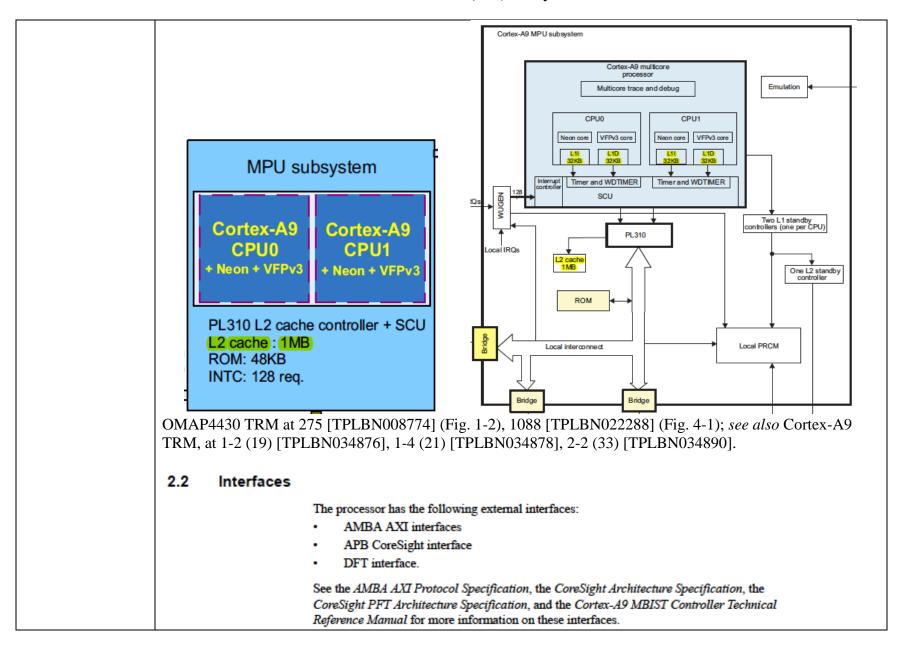

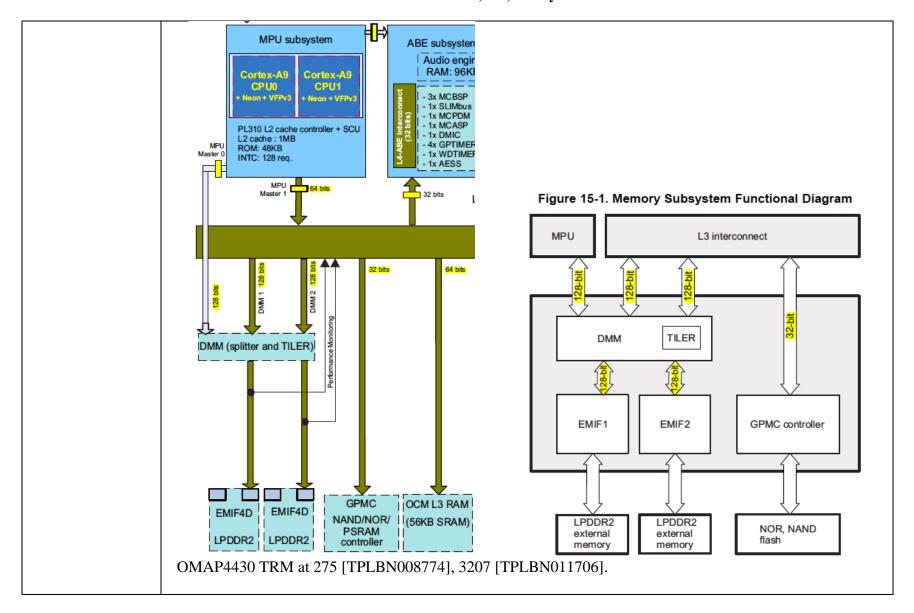

- 5. TI OMAP4430

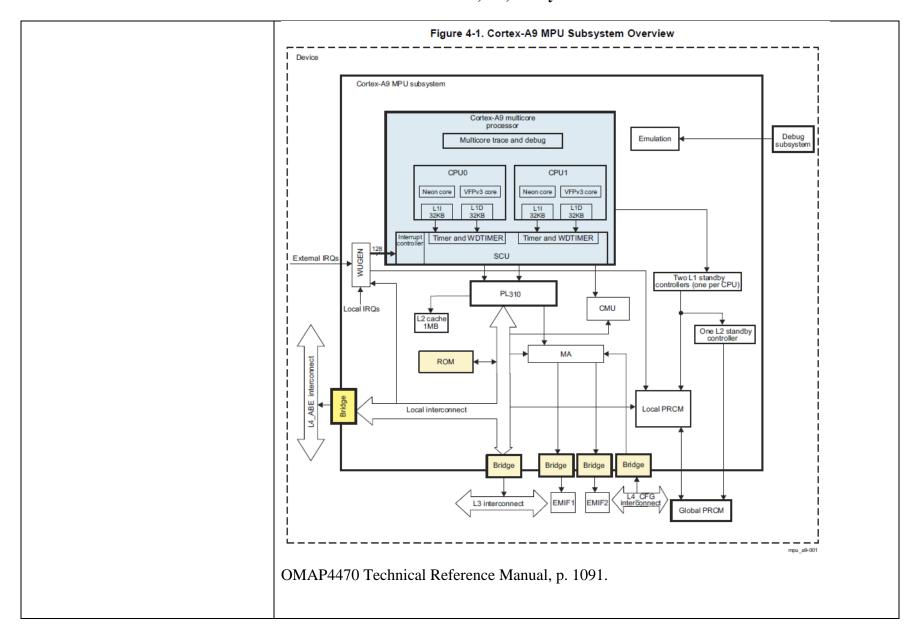

- 6. TI OMAP4460

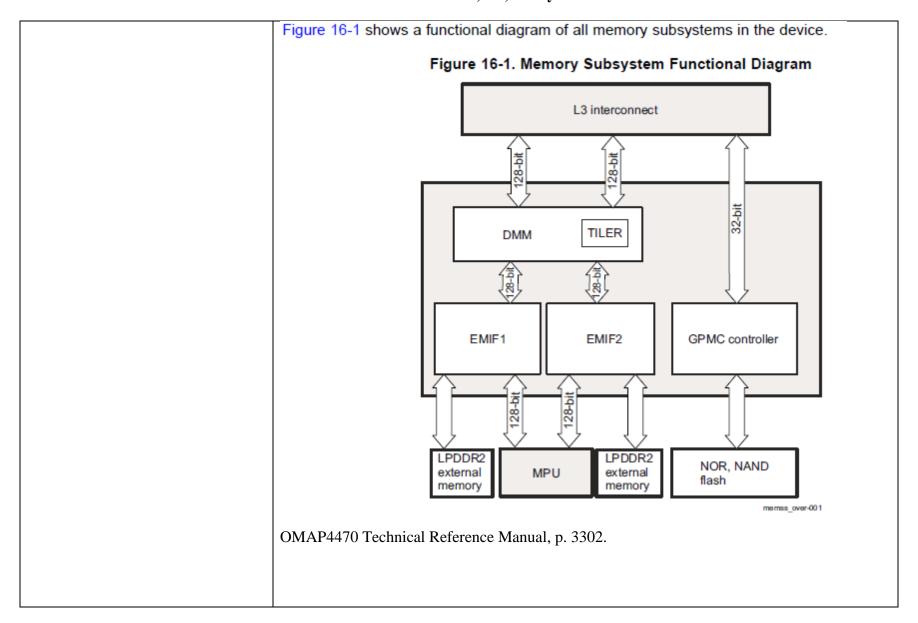

- 7. TI OMAP4470

The rest of the purportedly accused processors listed in Exhibit A *are never mentioned* in the charts and there is no evidence in support of any claims against them.

The charts do not provide supporting evidence for a large number of the allegations and thus even the seven specifically mentioned processors are not charted through every element of each claim with consistent evidentiary support. Many of the allegations are made "on information and belief." For certain claim elements, TPL simply states that such elements are present without providing any supporting evidence or by merely stating that the microprocessor has the recited claim language. TPL also contends that certain claim elements are present based on the understanding of one of ordinary skill in the art. For yet other elements, TPL cites to generic descriptions of technology in public articles and Wikipedia instead of identifying where the element is in the actual accused product or processor. This lack of support could not have resulted from lack of available information regarding the design and operation of the accused functionality, because Plaintiffs admit that they had public technical information available at the time they prepared the Contentions. [May Decl., Ex. D (Pls.' Ltr. at 2 ("For example, PDS provided numerous citations to public ARM documents to support its contentions.").]

<sup>&</sup>lt;sup>4</sup> See, e.g., May Decl., Exs. G-1 at 1, 4-5, 17-20, 23 ('336 elements 6.a, 6.b, 6.c, 6.f, 6.g and 9.b); G-2 at 1, 11, 20, 23-24, 27, 32, 35, 41-43, 47, 50, 53-54, 56, 59-60, 63, 65, 67-68, 72-73, 82, 85-86, 89, 95, 98, 104-106, 109, 112, 115, 117, 119-120, 122-123, 126-127 ('890 elements 1.a, 1.b, 1.c, 1.f, 1.g, 1.i, 1.j, 1.k, 1.l, 1.m, 1.n, 1.o, 7.b, 9.b, 9.c, 9.d, 9.e, 11.a, 11.b, 11.c, 11.d, 11.e, 11.f, 11.g, 11.i, 11.k, 11.l, 11.m, 11.n, 11.o, 11.p, 12.b, 13.b, 17.b, 19.b, 19.c, 19.d, and 9.e); and G-3 at 1, 3, 8, 15, 24, 45, 54, 63, 65, 70, 74, 84, 88-89, 92, 96, 99, 104, 106 ('749 elements 1 (preamble), 1.a, 1.b, 1.c, 1.d, 1.e, 1.f, 1.g, 1.h, 1.i, 1.j, 1.k, 1.l, 9.d, 9.e, 43 (preamble), 43.a, 43.b and 59 (preamble)).

<sup>25 | 5</sup> See, e.g., May Decl., Exs. G-1 at 19 ('336 element 6.h); G-2 at 53, 72-73 ('890 elements 7.b and 11.f)

<sup>&</sup>lt;sup>6</sup> See, e.g., May Decl., Exs. G-1 at 16-17 ('336 elements 6.d and 6.e), 18-19 (6.g); G-2 at 112 ('890 element 12.b).

<sup>&</sup>lt;sup>7</sup> See, e.g., Infr. Cont., Ex. G-1 at 10-11, 16-20 ('336 elements 6.d, 6.e, 6.g and 9.b); G-2 at 1, 5, 50, 67, 113, 117 ('890 elements 1.b, 1.c, 7.b, 11.c, 12.b and 17.b)

| 1 |  |

|---|--|

| 2 |  |

| 3 |  |

| 4 |  |

| 5 |  |

Finally, although the charts purport to make the infringement allegations on a representative basis, this is based solely on "information and belief." Each chart contains a footnote stating: "This chart provides some examples of such operation that, *on information and belief, are representative* of the operation of the processors in each of the Accused Products." [May Decl., Exs. G-1, G-2, G-3 at 1, respectively] (emphasis added). But nowhere do the Infringement Contentions attempt to show how the rest of the accused processors are similar to the seven representative processors used as examples.

#### C. The Parties' Meet-and-Confer Process

On February 27, 2015, LG sent Plaintiffs a letter regarding the deficiencies in their Infringement Contentions and requesting to meet and confer. [May Decl., Ex. C.] On March 18, 2015, Plaintiffs responded by letter attempting to defend the adequacy of their contentions. [*Id.*, Ex. D.]

On June 8, 2015, in response to Plaintiffs' question regarding the scope of financial information LG would produce for the accused products, LG informed Plaintiffs it would produce financial information for the accused U.S. products that contain the seven processors charted in Plaintiffs' Infringement Contentions. On June 15, 2015, the parties had a call regarding these issues, deficiencies in Plaintiffs' Infringement Contentions, and LG's prospective motion to strike. [May Decl. ¶ 10.] Because the parties were unable to resolve the dispute, LG informed Plaintiffs it will file the present motion. [*Id.*]

A motion to strike on similar grounds was filed on June 9, 2015, in related case *Technology Properties Limited LLC, et al. v. Samsung Electronics Co., LTD.*, Case No. 3:12-cv-03877-VC (PSG) and is currently set for hearing on August 11. For judicial efficiency purposes, LG noticed the hearing on its motion for the same date and time.

<sup>&</sup>lt;sup>8</sup> See, e.g., May Decl., Exs. G-1 at 1, 4-5, 17-19 ('336 elements 6.a, 6.b, 6.c, 6.f, 6.g and 6.h); Exs. G-2 at 1, 50, 63, 78, 112 ('890 elements 1.a, 1.b, 7.b, 11.a, 11.b, 11.g and 12.b); and G-3 at 1-2, 99 ('749 elements 1 (preamble), 1.a, 43 (preamble), 43.a). For most claim elements, TPL simply does not address whether or why the specifically cited microprocessors in its infringement charts should be considered "representative" of the operation and/or implementation of other microprocessors incorporated in LG's hundreds of accused products.

#### III. LEGAL STANDARD

Patent Local Rule 3-1(c) requires a patentee to provide "[a] chart identifying *specifically* where *each limitation of each asserted claim* is found within *each Accused Instrumentality*." Patent L.R. 3-1(c) (emphasis added); *see Silicon Labs., Inc. v. Cresta Tech. Corp.*, No. 5:14-cv-03227-PSG, 2015 WL 846679, at \*1 (N.D. Cal. Feb. 25, 2015); *Shared Memory Graphics LLC v. Apple, Inc.*, 812 F. Supp. 2d 1022, 1024 (N.D. Cal. 2010); *Bender v. Freescale Semiconductor, Inc.*, No. C 09–1156 PHJ (MEJ), 2010 WL 1689465, at \*3 (N.D. Cal. Apr. 26, 2010).

"[T]he degree of specificity under Local Rule 3-1 must be sufficient to provide reasonable notice to the defendant why the plaintiff believes it has a reasonable chance of proving infringement." *Shared Memory Graphics LLC v. Apple, Inc.*, 812 F. Supp. 2d 1022, 1025 (N.D. Cal. 2010) (citing *View Eng'g Inc. v. Robotic Vision Sys., Inc.*, 208 F.3d 981, 986 (Fed. Cir. 2000)). This requires that a party "map specific elements of Defendants' alleged infringing products onto Plaintiff's claim construction." *Id.*

This rule was designed to "make the parties more efficient, to streamline the litigation process, and to articulate with specificity the claims and theory of a plaintiff's infringement claims." *InterTrust Techs. Corp. v. Microsoft Corp.*, No. C 01-1640-SBA, 2003 WL 23120174, at \*2 (N.D. Cal. Dec. 1, 2003). A plaintiff violates this rule where it fails to "provide reasonable notice to the defendant why the plaintiff believes it has a 'reasonable chance of proving infringement." *Shared Memory Graphics*, 812 F.Supp.2d at 1025 (quoting *View Eng'g, Inc. v. Robotic Vision Sys., Inc.*, 208 F.3d 981, 986 (Fed. Cir. 2000)).

#### IV. ARGUMENT

A. Plaintiffs' Contentions with Respect to All Products that Do Not Contain the Seven Charted Processors Should Be Stricken for Lack of Any Evidentiary Support

Plaintiffs' Infringement Contentions fail to meet Patent L.R. 3-1(c) requirement to identify "specifically where each limitation of each asserted claim is found within *each* Accused Instrumentality." Patent L.R. 3-1(c) (emphasis added); *see also Silicon Labs.*, 2015 WL 846679, at \*1; *Bender*, 2010 WL 1689465, at \*3.

2

3

4

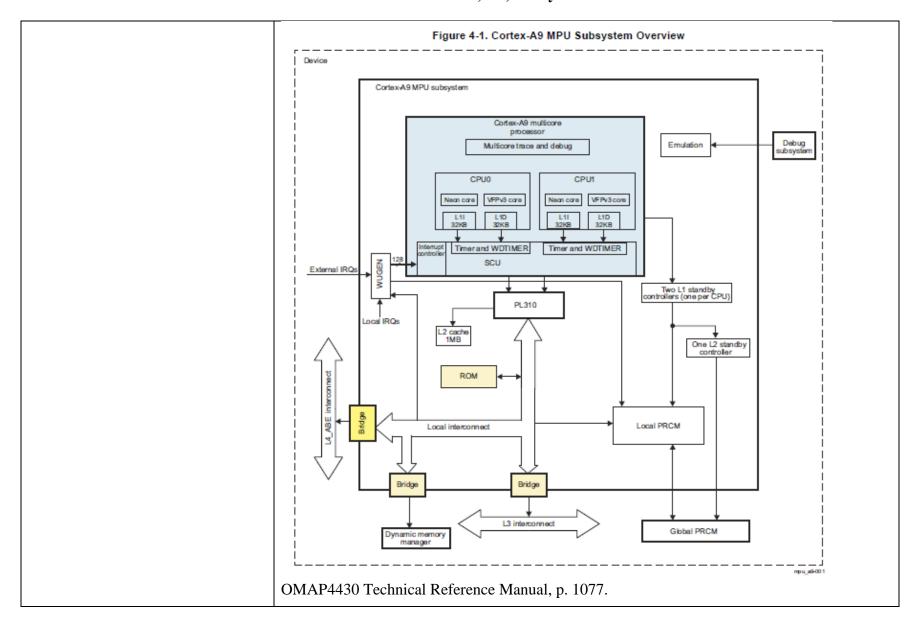

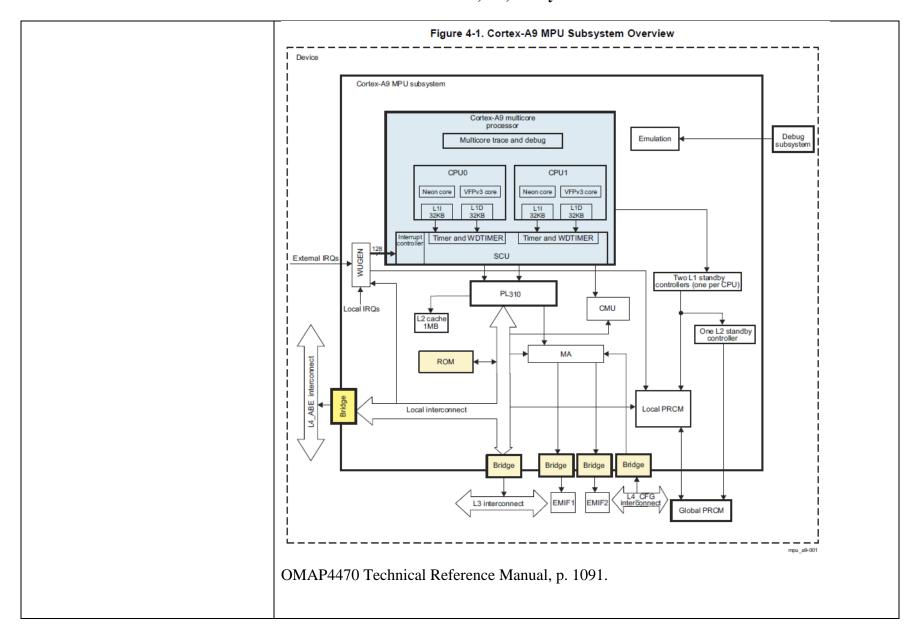

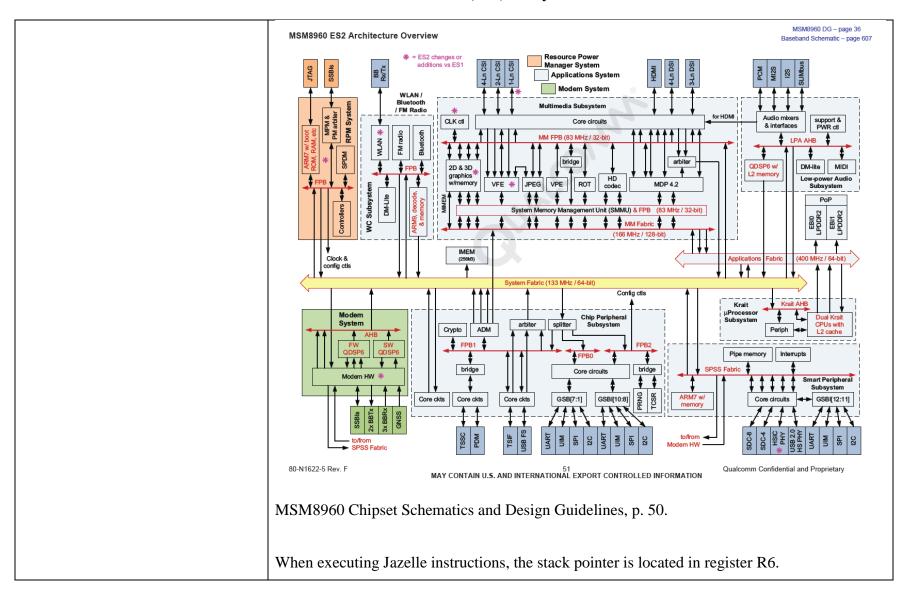

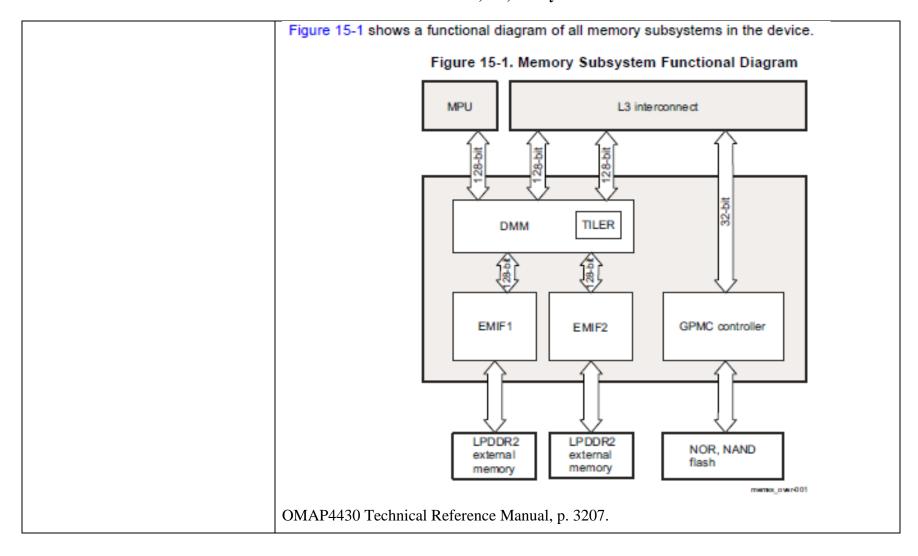

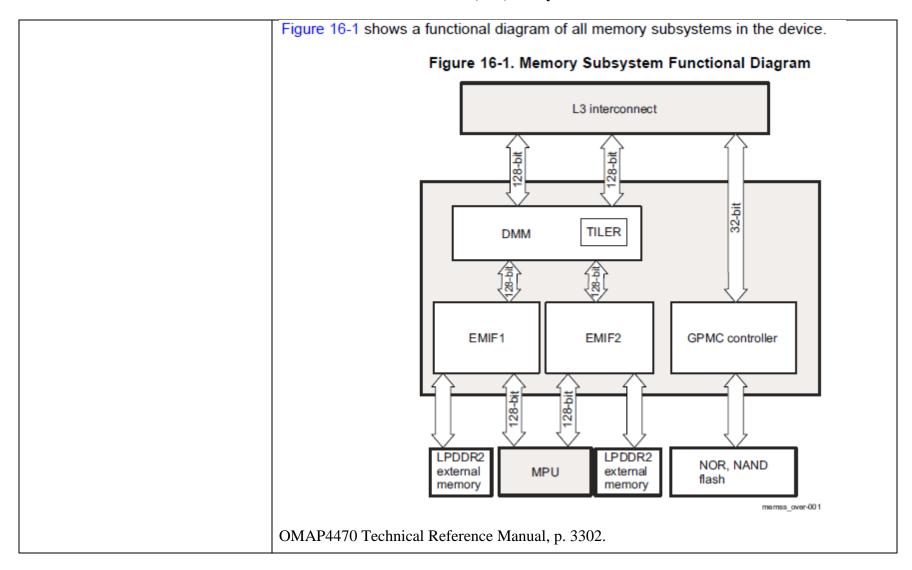

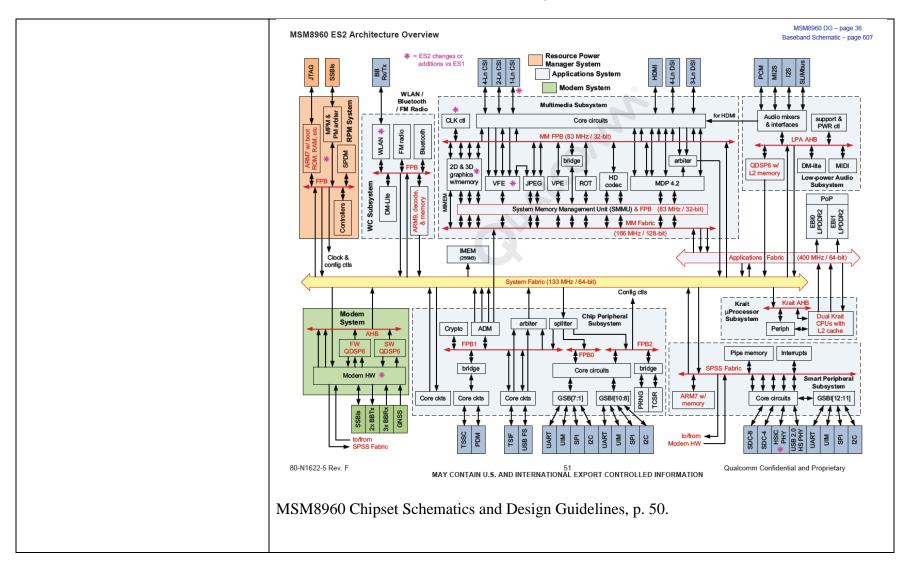

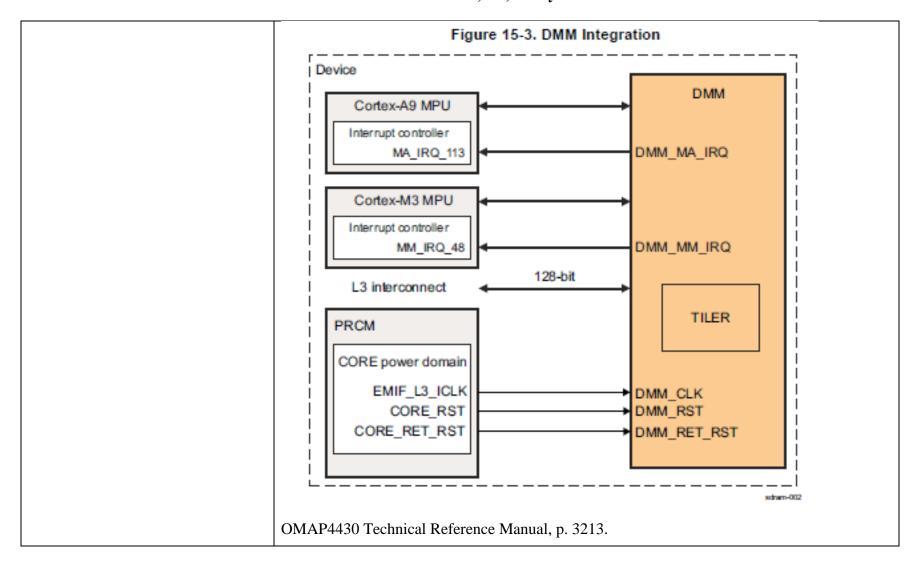

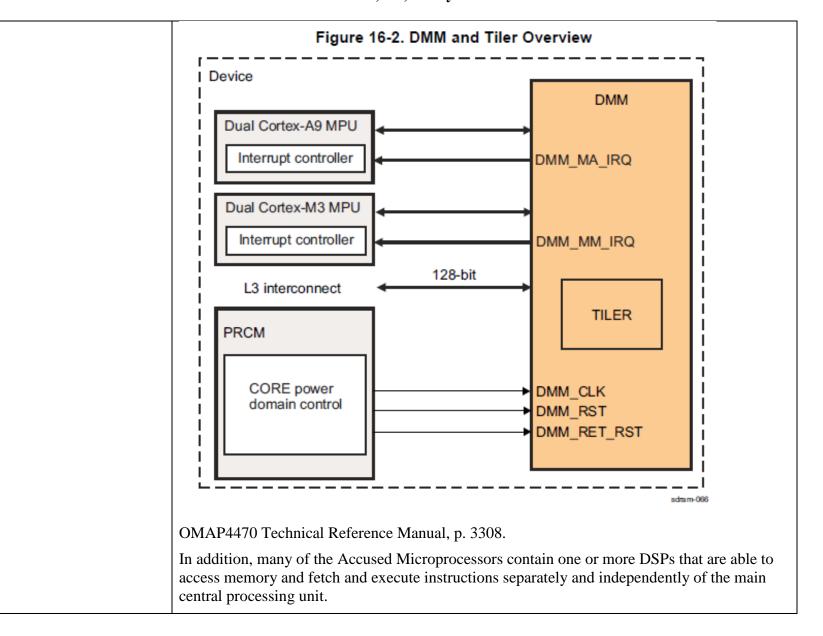

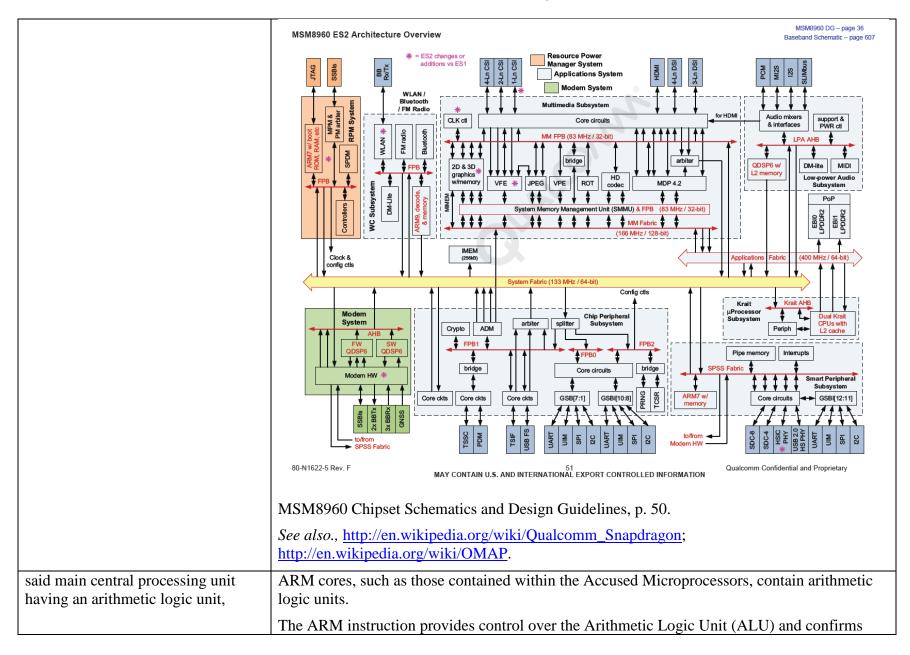

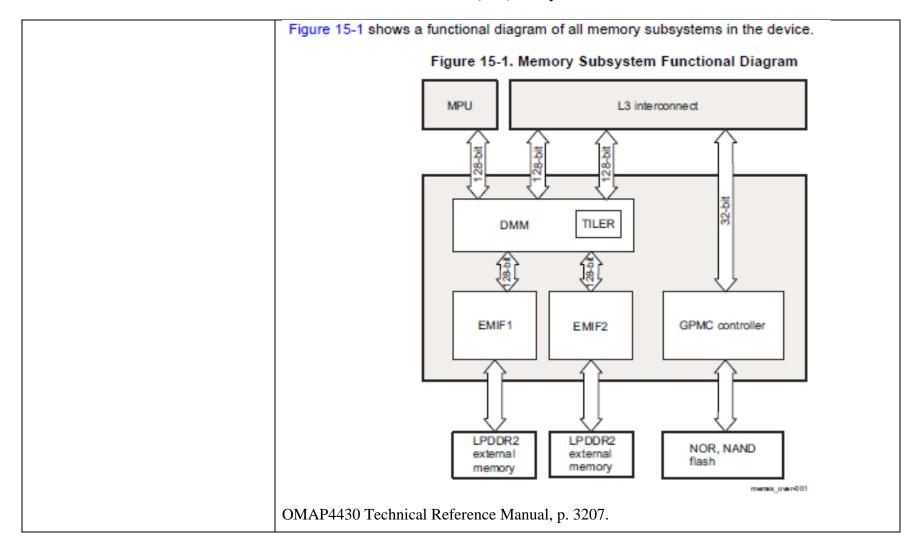

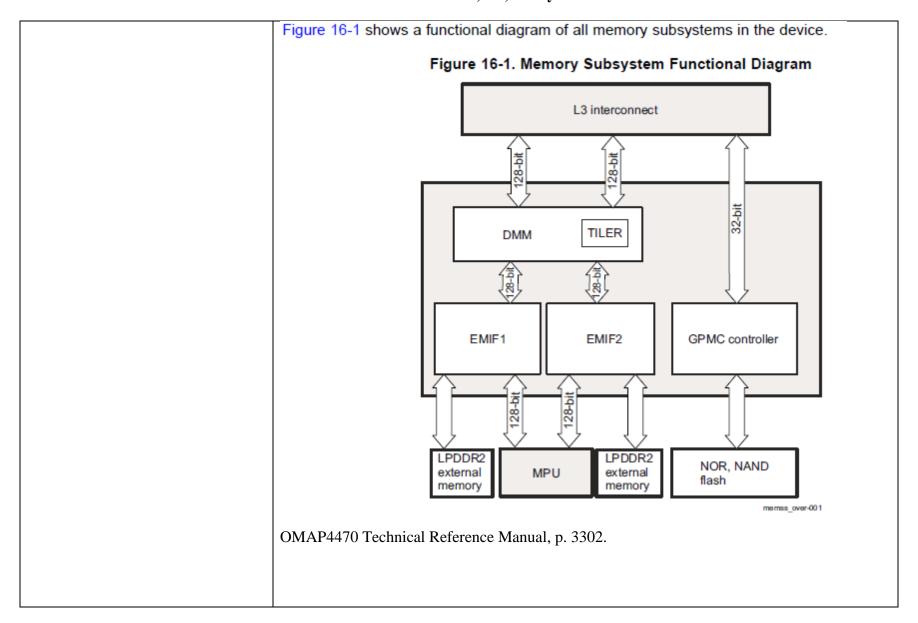

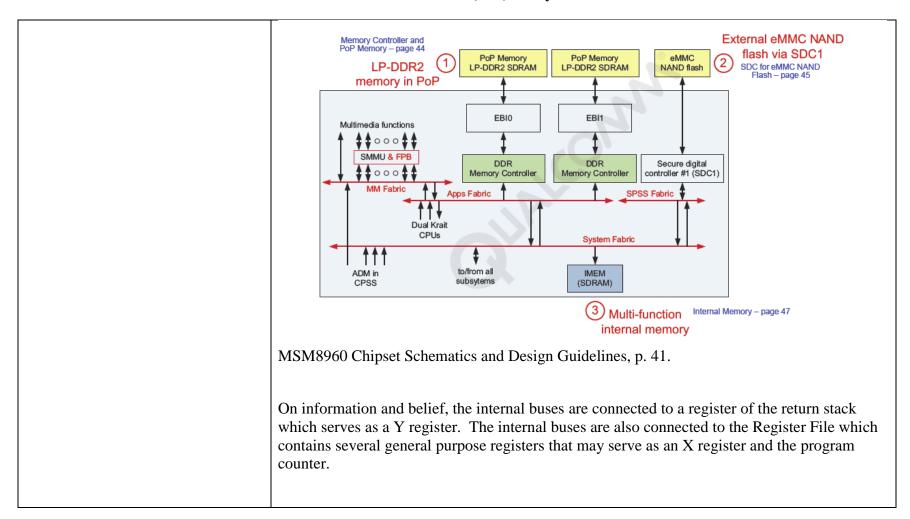

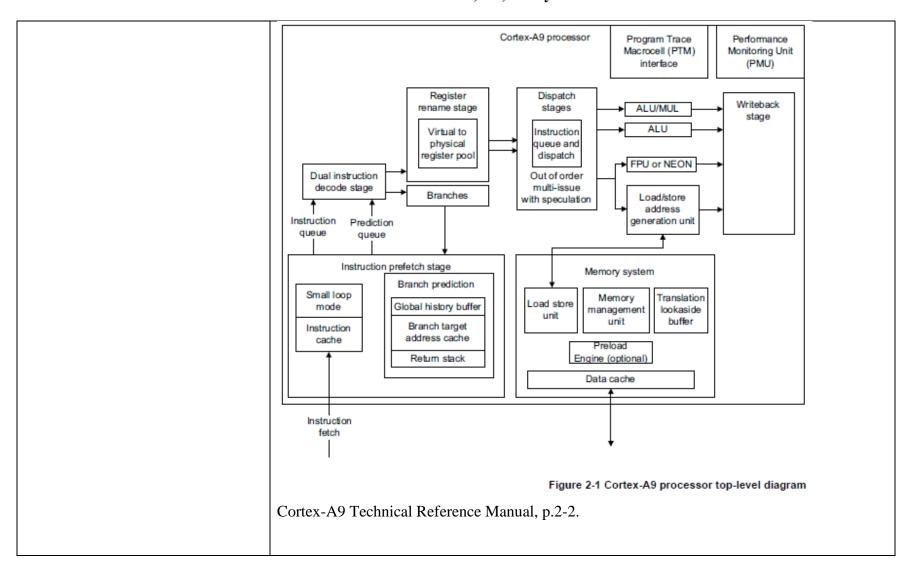

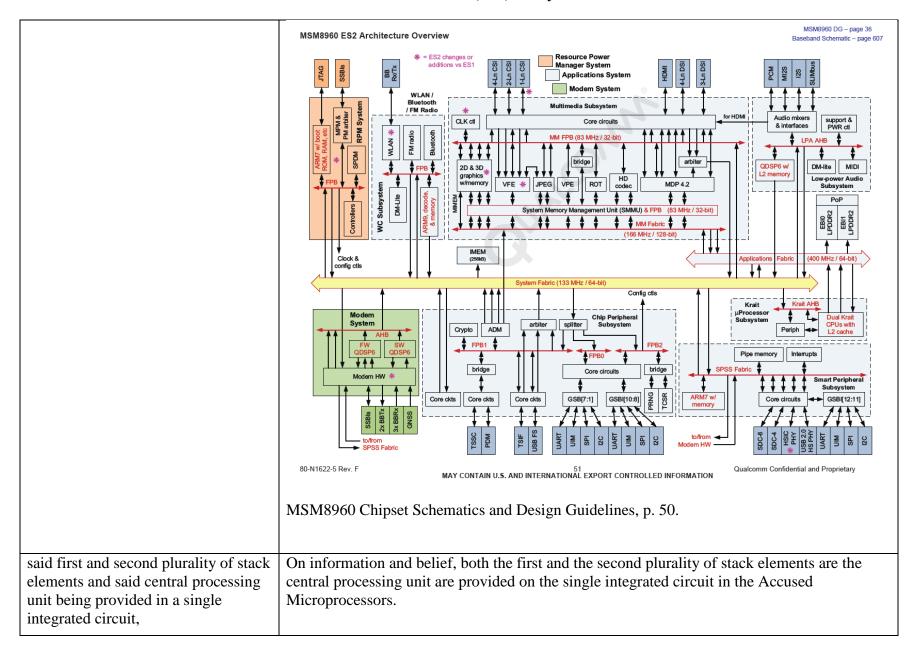

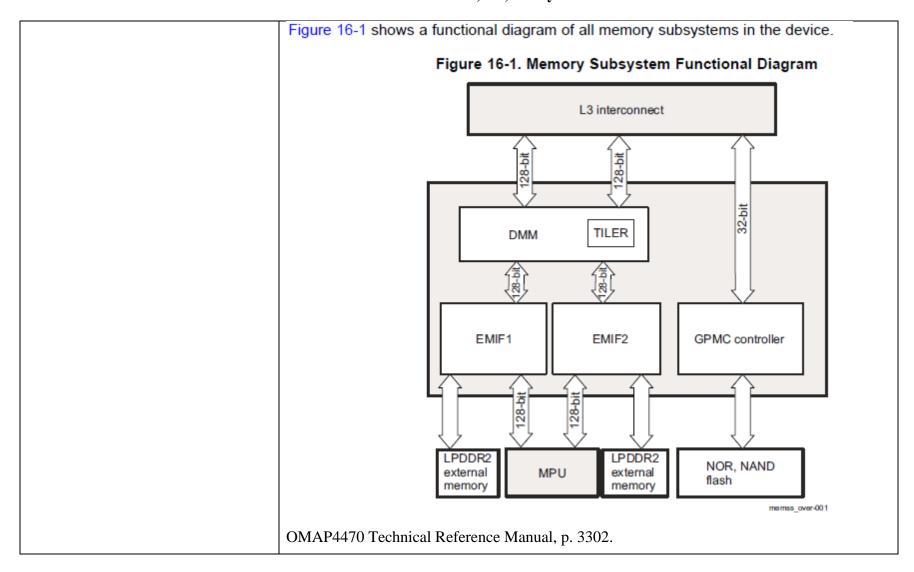

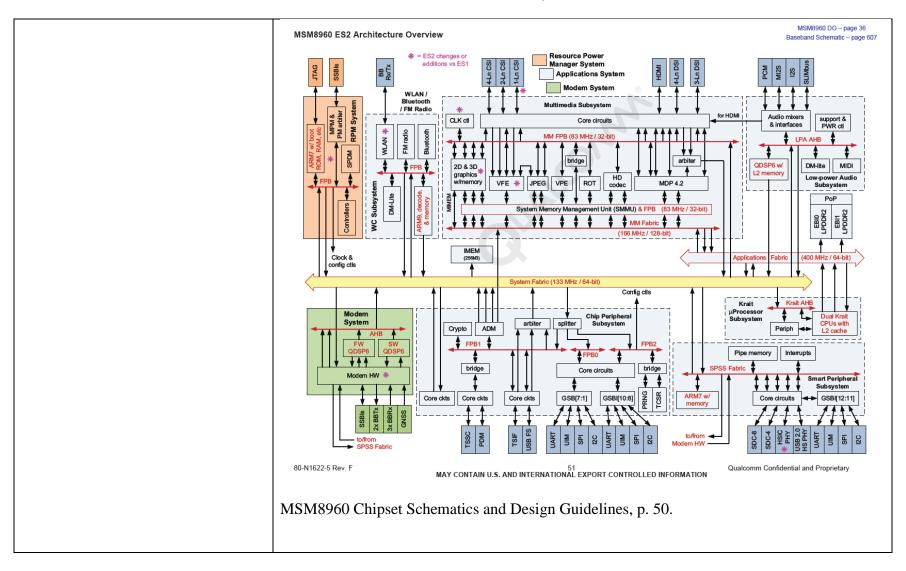

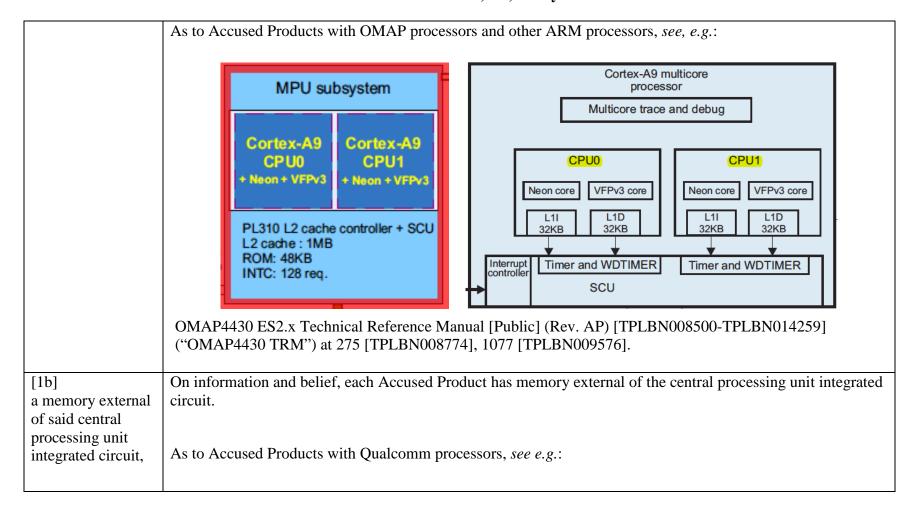

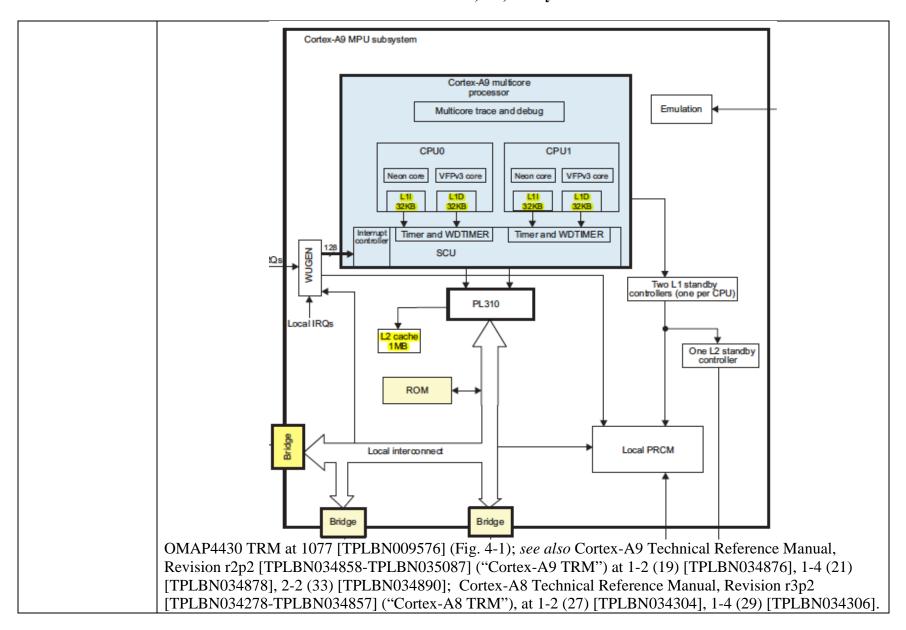

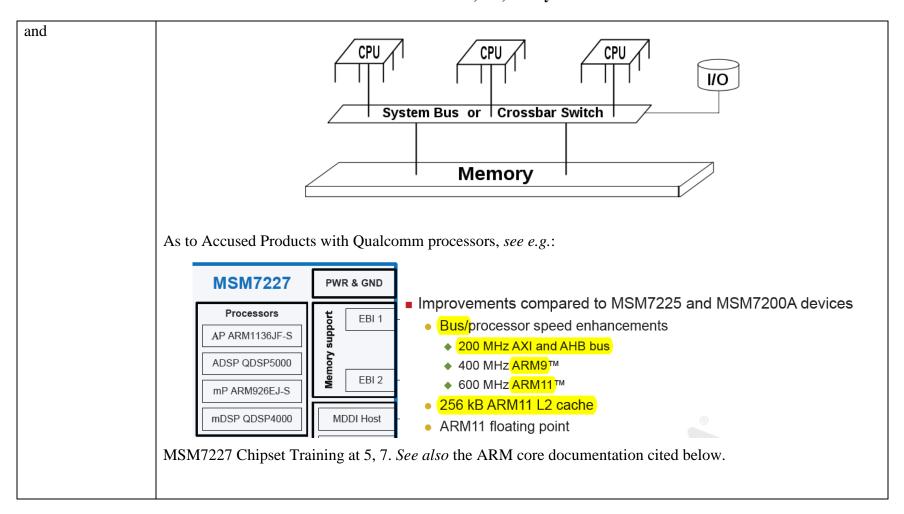

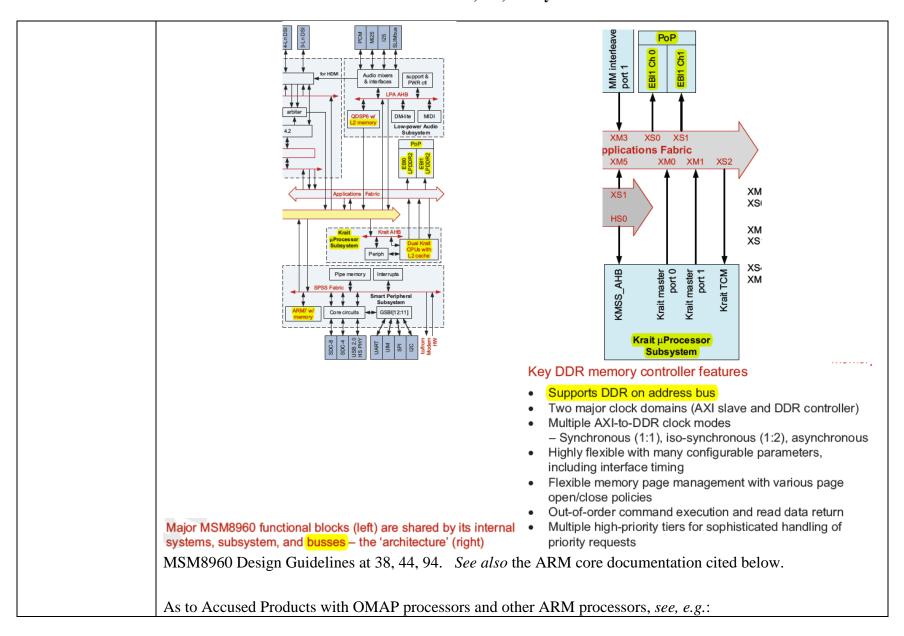

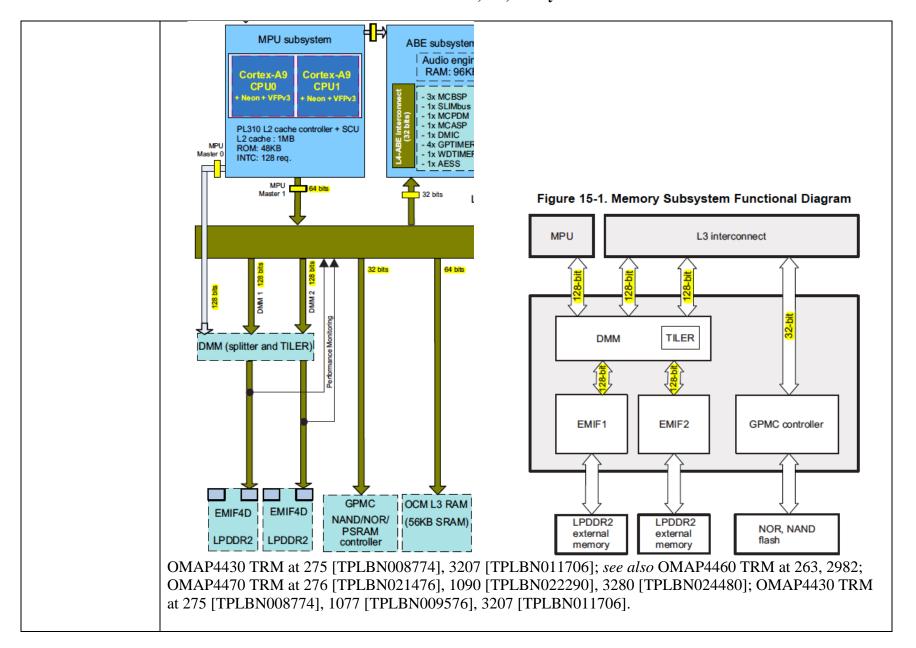

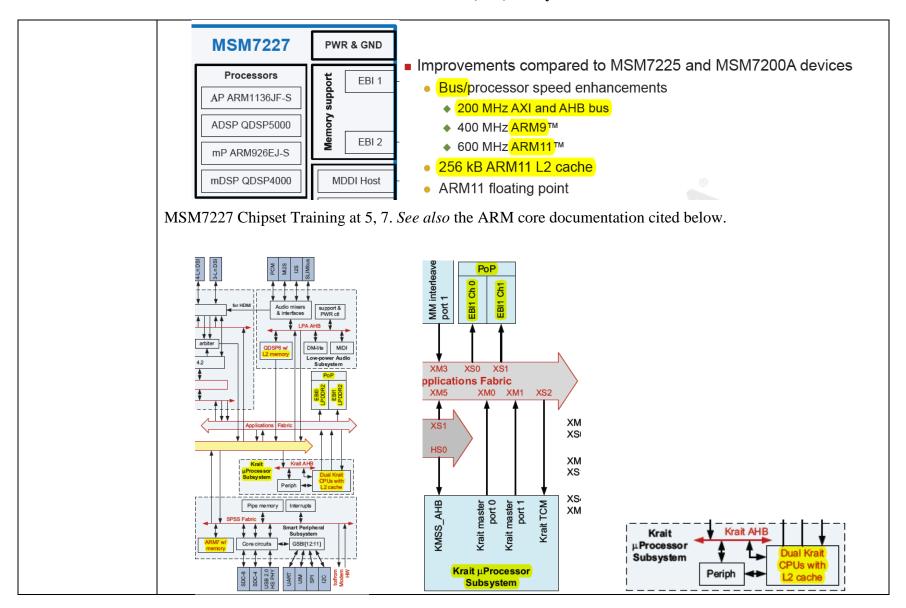

At most, Plaintiffs provided such identification to the seven processors specifically named in the charts: Qualcomm MSM8960, Qualcomm MSM8660, Qualcomm MSM8260, Qualcomm MSM7227, TI OMAP4430, TI OMAP4460, and TI OMAP4470, and end products containing those processors. Accordingly, the bare allegations as to "each Accused Microprocessor in each Accused Product" beyond the seven charted processors should be stricken.

1. Allegations as to "Each Accused Microprocessor" Based on "Information and Belief," Knowledge of One Skilled in the Art or Generic Information Fail to Meet Rule 3-1

The Infringement Contentions as to "each Accused Microprocessor in each Accused Product" are vague, conclusory and fail to meet the specificity requirements of Patent L.R. 3-1. "Vague contentions and conclusory statements invite Defendants and the Court to merely assume the presence of" an element and "fall short of the specificity required by Local Rule 3-1." *Shared Memory Graphics*, 812 F.Supp.2d at 1026. The "[p]laintiff may not craft its infringement contentions without *specifically identifying what in the device satisfies the limitation.*" *Infineon Techs. v. Volterra Semiconductor*, No. 11-cv-6239-MMC, 2012 U.S. Dist. LEXIS 146499, at \*4 (N.D. Cal. Oct. 9, 2012) (emphasis in original).

First, although the charts purport to accuse "each Accused Microprocessor in each Accused Product" as to every element of every claim, these blanket allegations are made largely "on information and belief." As this Court previously found, "simply alleging 'on information and belief' and representing 'vague, conclusory, and confusing statements' does not satisfy the requirement that the identifications be 'as specific as possible." *Solannex, Inc. v. MiaSole, Inc.*, 2013 WL 1701062, at \*3 (N.D. Cal. April 18, 2013) (citing *Theranos, Inc. v. Fuisz Pharma LLC*, 11–CV–05236–YGR, 2012 WL 6000798, at \*3 (N.D. Cal. Nov. 30, 2012)); *see also CSR Tech*.

<sup>&</sup>lt;sup>9</sup> See, e.g., May Decl., Exs. G-1 at 1, 4-5, 17-20, 23 ('336 elements 6.a, 6.b, 6.c, 6.f, 6.g and 9.b); G-2 at 1, 11, 20, 23-24, 27, 32, 35, 41-43, 47, 50, 53-54, 56, 59-60, 63, 65, 67-68, 72-73, 82, 85-86, 89, 95, 98, 104-106, 109, 112, 115, 117, 119-120, 122-123, 126-127 ('890 elements 1.a, 1.b, 1.c, 1.f, 1.g, 1.i, 1.j, 1.k, 1.l, 1.m, 1.n, 1.o, 7.b, 9.b, 9.c, 9.d, 9.e, 11.a, 11.b, 11.c, 11.d, 11.e, 11.f, 11.g, 11.i, 11.k, 11.l, 11.m, 11.n, 11.o, 11.p, 12.b, 13.b, 17.b, 19.b, 19.c, 19.d, and 9.e); and G-3 at 1, 3, 8, 15, 24, 45, 54, 63, 65, 70, 74, 84, 88-89, 92, 96, 99, 104, 106 ('749 elements 1 (preamble), 1.a, 1.b, 1.c, 1.d, 1.e, 1.f, 1.g, 1.h, 1.i, 1.j, 1.k, 1.l, 9.d, 9.e, 43 (preamble), 43.a, 43.b and 59 (preamble)).

1

3 4

> 5 6

8

9

7

10

11 12

13 14

15 16

17

18 19

20 21

22

23

24

25

26 27

28

Inc. v. Freescale Semiconductor, No. C-12-02619 RS (JSC), 2013 WL 503077, at \*7-8 (N.D. Cal. Feb. 8, 2013). Therefore reliance on "information and belief" is impermissible and fails to comply with Rule 3-1.

Second, to the extent the contentions rely on knowledge of a person of ordinary skill in the art, <sup>10</sup> a bare assertion that a person of ordinary skill in the art could locate the element in the accused instrumentality does not comply with Rule 3-1. See, e.g., Bender, 2010 WL 1689465, at \*4 ("[m]erely alluding to the fact that any electrical engineer would understand the infringement contentions is not sufficient."). The bald assertions in Plaintiffs' Infringement Contentions that certain claim elements are present based on the understanding of one of ordinary skill in the art are not substantiated by any other evidence and do not rise above an arbitrary unsupported conclusion. Thus they cannot serve as support of Plaintiffs' allegations.

Third, the Contentions attempt to rely on generic articles and Wikipedia for conclusory statements about general technology. 11 Plaintiffs' generic descriptions of technology lack the specific identification of each element of an asserted claim in each accused instrumentality and cannot meet the specificity requirement of Rule 3-1.

Plaintiffs' failure to provide sufficient support is inexcusable given the admittedly available public materials regarding the design of the accused microprocessors. [May Decl., Ex. D at 2, Ex. E.]

#### 2. Allegations based on "Representative" Products Fail to Meet Rule 3-1

Nor can the contentions as to "each Accused Microprocessor" survive based on the seven named processors being "representative" of the rest. First, none of the seven "representative" processors are charted through every element of every claim and can "represent" the rest of the products as to each asserted claim. Second, as this Court has previously explained, in order to rely on a claim that one accused product is representative of another for purposes of Rule 3-1(c), a patentee must do more than state as much—it must show how. Silicon Labs., 2015 WL 846679, at

<sup>&</sup>lt;sup>10</sup> See, e.g., May Decl., Exs. G-1 at 10-11, 16-17 ('336 elements 6.d and 6.e), 18-19 (6.g); G-2 at 112 ('890 element 12.b).

<sup>&</sup>lt;sup>1</sup> [May Decl., Ex. G-1 at 10-11, 16-20 ('336 elements 6.d, 6.e, 6.g and 9.b); Ex. G-2 at 1, 5, 50, 67, 113, 117 ('890 elements 1.b, 1.c, 7.b, 11.c, 12.b and 17.b)).]

#### Case3:12-cv-03880-VC Document97 Filed06/29/15 Page16 of 20

| *1 (finding that where the claim required "a single integrated circuit," the charted product did not       |

|------------------------------------------------------------------------------------------------------------|

| appear representative because it consisted of a single die in a package and the non-charted                |

| "represented" product consisted of two dies which would correspond to two circuits). Rule 3-1              |

| "requires Plaintiff to articulate how the accused products share the same, or substantially the same,      |

| infringing [qualities] with any other product or with the 'representative' product[]." <i>Id</i> . (citing |

| Bender, 2010 WL 1689465, at *3); see also Ameranth, Inc. v. Pizza Hut, Inc., Nos. 12-cv-00729 et           |

| al., 2013 WL 3894880, at *7 (S.D. Cal. July 26, 2013) ("While [the plaintiff] says it identified the       |

| accused versions temporally, by their functional aspects or by their version names or numbers, it          |

| must at least state how the accused previous versions are the same or reasonably similar to the            |

| charted version, or else provide a separate chart for each version.").                                     |

Here, Plaintiffs have failed to provide any evidence showing how the seven charted processors "share the same, or substantially the same, infringing [qualities]" with "each Accused Microprocessor" with respect to each element of each asserted claim. In fact, Plaintiffs' charts openly acknowledge that their allegations regarding "representative" products are speculative and based solely on "information and belief": "[t]his chart provides some examples of such operation that, *on information and belief, are representative* of the operation of the processors in each of the Accused Products." [May Decl., Exs. G-1, G-2, G-3 at 1, respectively] (emphasis added).

For 118 of the 437 accused products, plaintiffs fail to even identify the corresponding processors and it is impossible to tell what features are being "represented." [May Decl., Ex. A at 56-58.] The identified processors and cores include dozens of different makes and models, including made by Qualcomm, TI, ARM, NVidia, LG, and MediaTek. Some of them, for example NVidia and MediaTek, are not mentioned in the charts at all. The others, for example, the subset of ARM processing cores, contain several different design generations and different members within those generations.

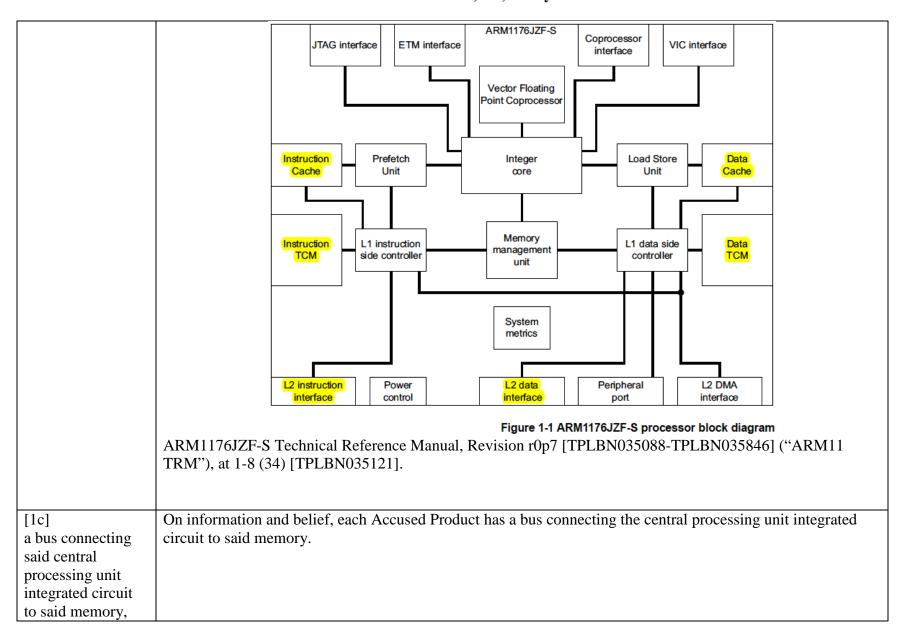

By way of example only, Plaintiffs' Infringement Contentions fail to establish a reasonable chance of success in proving infringement of claim 1 of the '890 Patent by any product including only an ARM1176 Processor. Like in *Silicon Labs*, the "representative" and "represented"

products have "different structures that are material to the infringement of at least one of the asserted claims" and therefore Plaintiffs' contentions based on a representative basis fail. *Silicon Labs.*, 2015 WL 846679, at \*1.

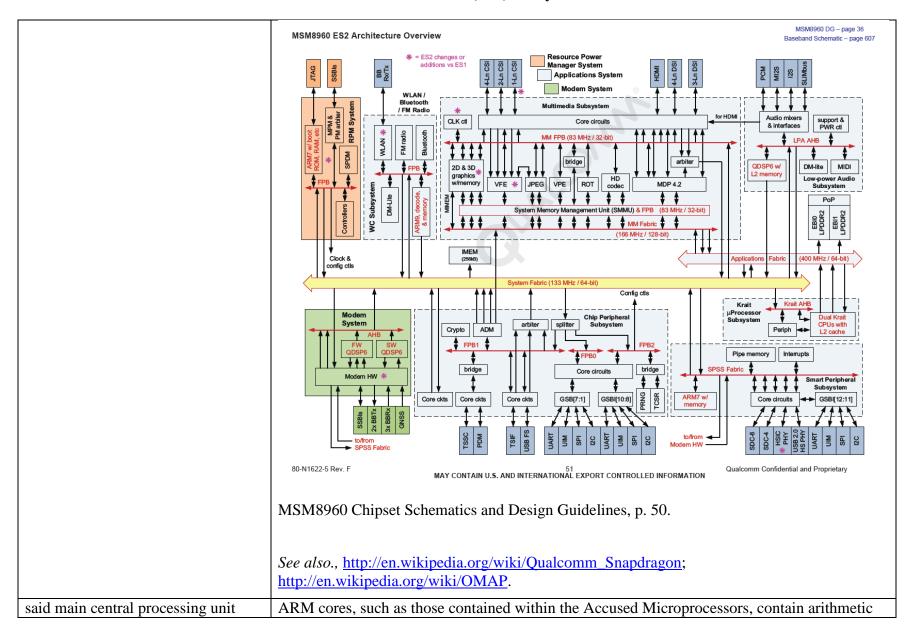

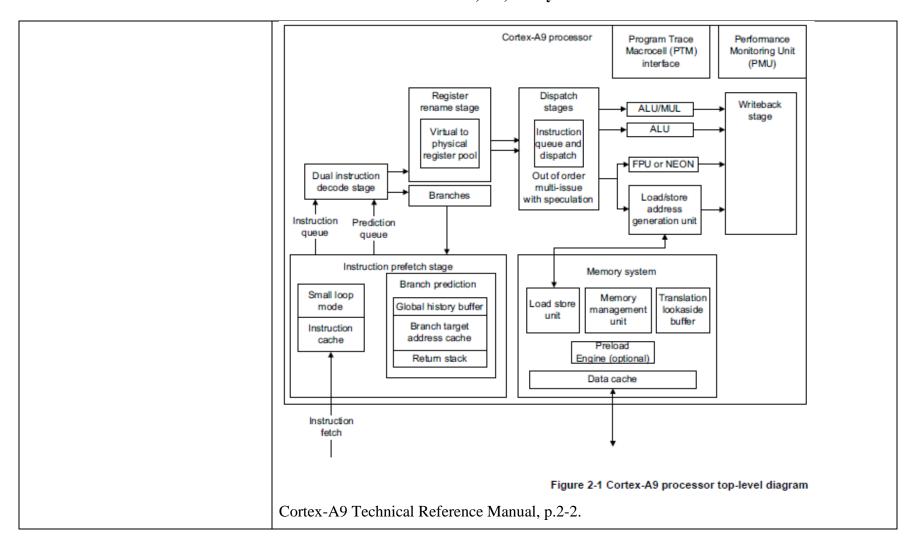

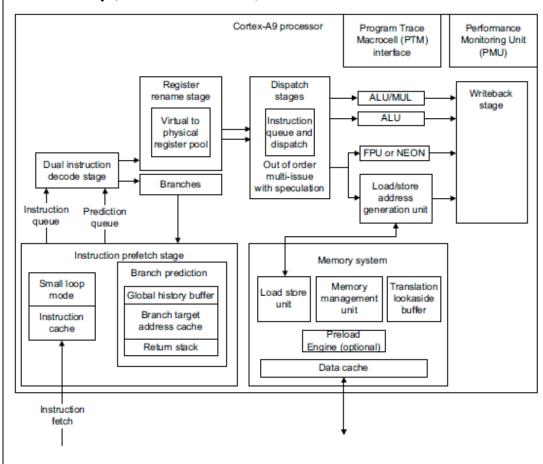

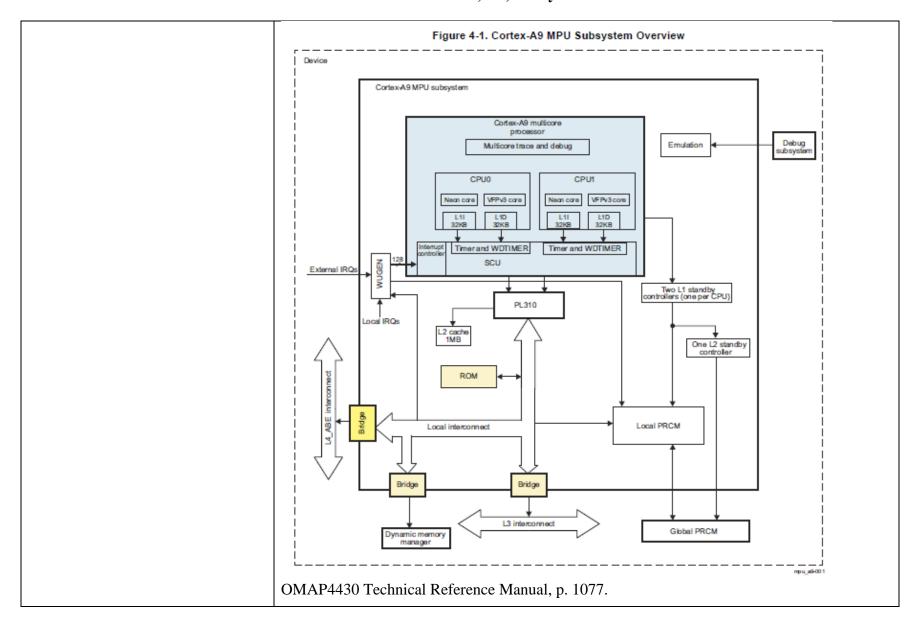

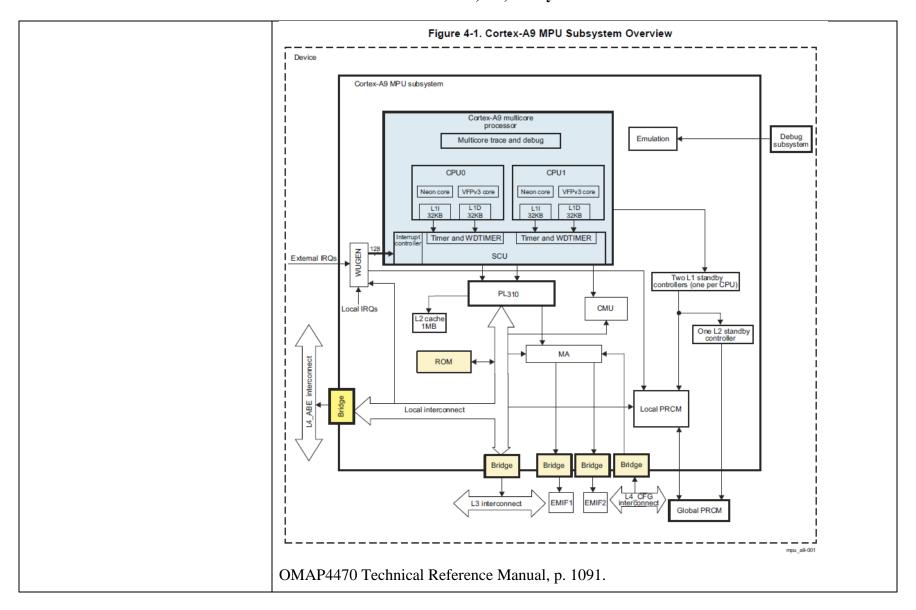

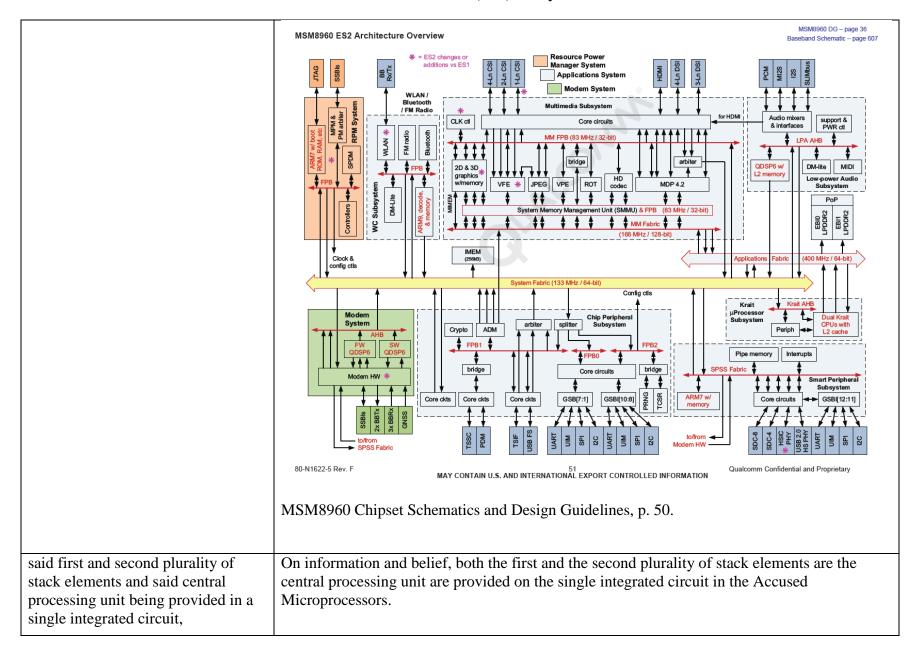

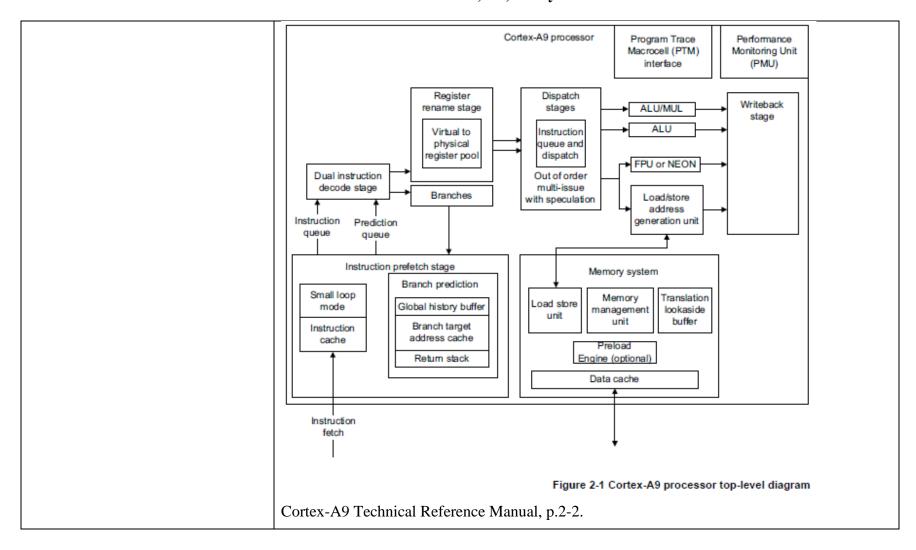

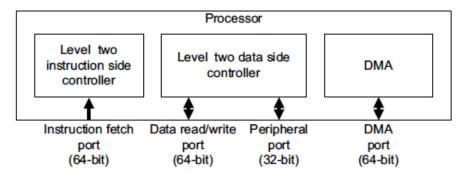

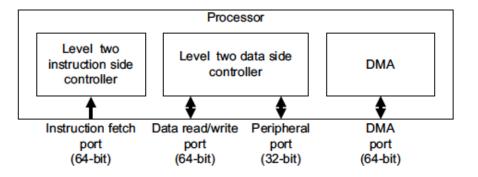

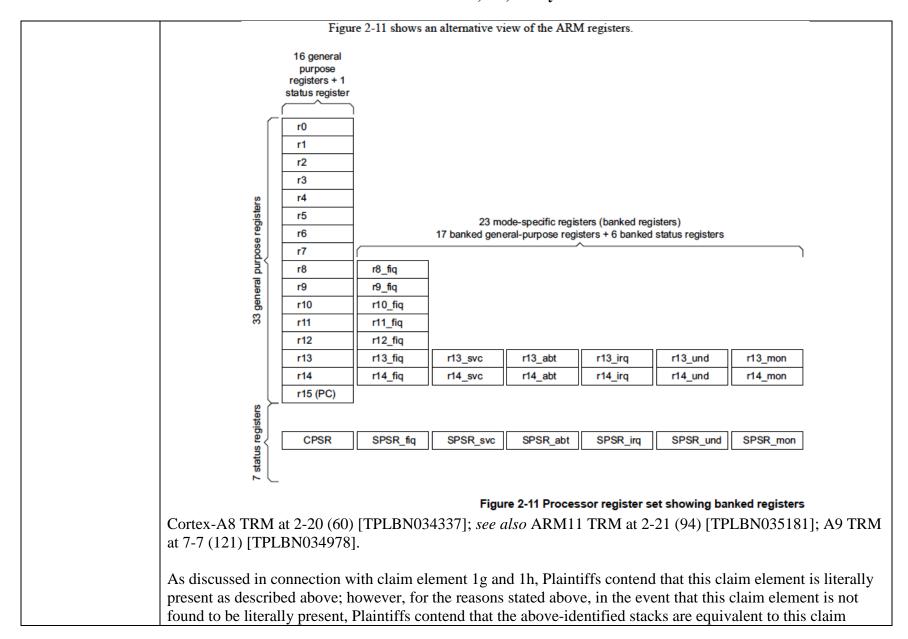

Claim 1 of the '890 Patent requires both a "main central processing unit" and "a separate direct memory access central processing unit in a single integrated circuit . . ." May Decl., Ex. 4 (Exhibit G-2 at 1). Plaintiffs allege that the first central processing unit ("CPU") limitation is satisfied by the presence of a "first ARM core," and the second, separate CPU limitation is satisfied because "many of the Accused Microprocessors are multicore processors that contain more than one ARM core." *Id.* However, even publicly available documents (of the type already cited by Plaintiffs in their contentions) show that many of the allegedly "represented" processors in Table A.6 have only one core. For example, as shown below, the specifications available on ARM's website show that the ARM1136 Processor has only one core.

| ARM1136               |                       |  |

|-----------------------|-----------------------|--|

| Architecture          | ARMv6                 |  |

| Dhrystone Performance | 1.25 DMIPS/MHz        |  |

| Multicore             | No - Single core only |  |

[See May Decl., Ex. E; http://www.arm.com/products/processors/classic/arm11/arm1136.php.] Thus by itself, the ARM1136 Processor cannot infringe.

#### B. Infringement Charts as to Seven Named Processors Are Deficient

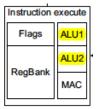

Despite providing specific processor names and some cites to guides, the infringement contentions based on the seven named processors also fail to meet the requirements of Rule 3-1.

Plaintiffs fail to chart a single microprocessor against every limitation of any one asserted claim, which alone makes the Contentions deficient under Rule 3-1. For example, for certain elements, Plaintiffs rely, instead of showing where the element is in the accused processor, on "information and belief" [see, e.g., May Decl., Ex. G-1 at 15-16, 18-19], knowledge of a person of ordinary skill in the art [id., G-1 at 11, 16], or generic evidence [id., G-1 at 15, 19]. Therefore

these charts violate Rule 3-1 for the same reasons as the allegations regarding "each Accused

| _ |  |

|---|--|

| 2 |  |

| _ |  |

1

Microprocessor" stated above.

3

4

5 6

7

9

8

10 11

12

13 14

15

16

17

18 19

20

21

22 23

24

25

26

27

28

C. Infringement Contentions based on the '890 and '749 Patents as to the Accused Products that Were Released after the Expiration of These Patents **Should Be Stricken**

A claim of patent infringement can be asserted only for the term of the patent. See 35 U.S.C. § 271(a) ("whoever without authority makes, uses, offers to sell, or sells any patented invention, within the United States or imports into the United States any patented invention during the term of the patent therefor, infringes the patent'') (emphasis added).

The '749 Patent expired on August 8, 2012, and the '890 Patent expired on June 25, 2013. [35 U.S.C. § 154(c); Dkt. No. 1, Exs. A, B.] Plaintiffs accused the same products as to all three patents. A number of the accused LG products were first released after the expiration of the '749 Patent and after the expiration of the '890 Patent. [See May Decl., Ex. C at 2.] Therefore Plaintiffs' Infringement Contentions based on the '749 and '890 Patents should be stricken as to the products released after the expiration of these patents.

#### D. Infringement Contentions as to the Accused Products that LG Has Never Made, Used, Imported, Sold, or Offered for Sale in the United States Should Be Stricken

Direct infringement liability is "limited to infringing activities that occur within the United States." MEMC Elec. Materials, Inc. v. Mitsubishi Materials Silicon Corp., 420 F.3d 1369, 1375 (Fed. Cir. 2005); see also 35 U.S.C. § 271(a) ("A person who, without a license, "makes, uses, offers to sell, or sells any patented invention within the United States or imports into the United States" is liable for direct patent infringement."). There can be no induced or contributory infringement without direct infringement. MEMC Elec. Materials, 420 F.3d at 1378; Fujitsu Ltd. v. Netgear Inc., 620 F.3d 1321, 1326 (Fed. Cir. 2010). Therefore the "general rule under United States patent law is that no infringement occurs when a patented product is made and sold in another country." Microsoft Corp. v. AT & T Corp., 550 U.S. 437, 441 (2007). There is a "strong policy against extraterritorial liability" in the patent law. See Halo Elecs., Inc. v. Pulse Elecs., Inc., 769 F.3d 1371, 1378 (Fed. Cir. 2014).

| 1 |  |

|---|--|

| 2 |  |

| 3 |  |

| 4 |  |

| 5 |  |

| 6 |  |

| 7 |  |

At least 208 of the 437 accused LG products in Plaintiffs' Exhibit A LG has not made, sold, offered for sale, or imported into the United States. [May Decl., Ex. F.] Therefore LG cannot be liable for infringement based on these products. Plaintiffs' Infringement Contentions as to these products should be stricken.

#### E. If the Court Permits Plaintiffs to Supplement Their Contentions, Any Amendment Should Be Limited to Products with the Seven Charted Processors

As demonstrated above, Plaintiffs' infringement Contentions are deficient and should be stricken in their entirety. But in the event the Court permits Plaintiffs to cure the deficiencies in their Infringement Contentions and supplement with additional support, such amendment should avoid expanding the case beyond the seven charted processors because it would substantially prejudice LG.

The purpose of Rule 3-1 is to "require parties to crystallize their theories of the case early in the litigation and to adhere to those theories once they have been disclosed." *Digital Reg of Texas, LLC v. Adobe Sys., Inc.*, No. 12-CV-01971-CW (KAW), 2013 U.S. Dist. LEXIS 93814, at \*9 (N.D. Cal. July 3, 2013) (quoting *InterTrust Techs. Corp. v. Microsoft Corp.*, No. 01-1640 SBA, 2003 U.S. Dist. LEXIS 22736, at \*1 (N.D. Cal. Dec. 1, 2003)).

The patent local rules were adopted by this district in order to give claim charts more "bite." The rules are designed to require parties to crystallize their theories of the case early in the litigation and to adhere to those theories once they have been disclosed.... Unlike the liberal policy for amending pleadings, the philosophy behind amending claim charts is decidedly conservative, and designed to prevent the "shifting sands" approach to claim construction.

Atmel Corp. v. Information Storage Devices, Inc., 1998 WL 775115 at \*2 (N.D. Cal. Nov. 5, 1998).

Expanding this case beyond the seven charted processors at this late point in the schedule would prejudice LG's ability to prepare its defenses. This case was filed on July 24, 2012. Fact discovery is set to close on September 8, 2015—less than three months away. All defendants in the related cases, including LG, already produced their invalidity contentions on April 21, 2015 in reliance, in part, on their understanding of Plaintiffs' infringement contentions.

Permitting Plaintiffs to expand the case would also give Plaintiffs an unfair second bite at the apple. Plaintiffs produced their Infringement Contentions on January 20, 2015—two and half years after they filed this case and also after they litigated the ITC investigation on the '336 Patent on some of the same products. Plaintiffs have had years, based on extensive publicly available information, to investigate their claims and prepare properly supported contentions, and are not entitled to restart the case less than three months before fact discovery cut-off.

#### V. **CONCLUSION**

Based on the above, LG respectfully requests that its motion be granted and Plaintiffs' Infringement Contentions be stricken in their entirety. In the alternative, to the extent the Court grants Plaintiffs leave to serve supplemental contentions, LG requests an order compelling supplemental contentions that:

- (a) are limited to the accused LG products that were previously identified in Table A.6 of Exhibit A to Plaintiffs' January 20, 2015 contentions, that include one of the following processors: Qualcomm MSM8960, Qualcomm MSM8660, Qualcomm MSM8260, Qualcomm MSM7227, TI OMAP4430, TI OMAP4460, and TI OMAP4470; were not released after the expiration of the corresponding Patent-in-Suit; and are not on the list of LG products that have not been sold in the U.S.;

- (b) comply with Patent Local Rule 3-1 by identifying specifically where each limitation of each asserted claim is found within each accused LG product, including, at a minimum, providing a separate claim chart for each of the above seven accused microprocessors; and

- (c) exclude all other products (identified in Table A.6 of Exhibit A or otherwise) from the scope of this case for all purposes.

Dated: June 29, 2015 FISH & RICHARDSON P.C.

> By: /s/ Olga I. May Olga I. May

Attorneys for Defendants LG ELECTRONICS, INC. and LG ELECTRONICS U.S.A., INC.

25

26

| 1 2 | Michael J. McKeon ( <i>Pro Hac Vice</i> ), <u>mckeon@fr.c</u><br>Christian A. Chu (SBN 218336), <u>chu@fr.com</u><br>Richard A. Sterba ( <i>Pro Hac Vice</i> ), sterba@fr.com | <u>com</u>                                                    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 3   | FISH & RICHARDSON P.C.<br>1425 K Street, NW, Suite 1100                                                                                                                       |                                                               |

| 4   | Washington, DC 20005<br>Telephone: (202) 783-5070<br>Facsimile: (202) 783-2331                                                                                                |                                                               |

| 5   |                                                                                                                                                                               |                                                               |

| 6   | Wasif Qureshi ( <i>Pro Hac Vice</i> to be filed), <u>qureshi</u> FISH & RICHARDSON P.C.                                                                                       | <u>a)tr.com</u>                                               |

| 7   | 1221 McKinney Street, Suite 2800<br>Houston, TX 77010                                                                                                                         |                                                               |

| 8   | Telephone: (713) 654-5300<br>Facsimile: (713) 652-0109                                                                                                                        |                                                               |

| 9   | Olga I. May (SBN 232012), omay@fr.com<br>FISH & RICHARDSON P.C.                                                                                                               |                                                               |

| 10  | 12390 El Camino Real<br>San Diego, CA 92130                                                                                                                                   |                                                               |

| 11  | Telephone: (858) 678-4745<br>Facsimile: (858) 678-5099                                                                                                                        |                                                               |

| 12  | Attorneys for Defendants                                                                                                                                                      |                                                               |

| 13  | LG ELECTRONICS, INC. and LG ELECTRONIC                                                                                                                                        | CS U.S.A., INC.                                               |

| 14  | UNITED STATES I                                                                                                                                                               |                                                               |

| 15  | NORTHERN DISTRIC<br>SAN JOSE                                                                                                                                                  |                                                               |

| 16  | TECHNOLOGY PROPERTIES LIMITED LLC,                                                                                                                                            | Case No. 3:12-cy-03880-VC                                     |

| 17  | PHOENIX DIGITAL SOLUTIONS LLC, and PATRIOT SCIENTIFIC CORPORATION,                                                                                                            | EXHIBITS G-1 TO G-3 TO THE                                    |

| 18  | Plaintiffs,                                                                                                                                                                   | DECLARATION OF OLGA I. MAY IN SUPPORT OF DEFENDANTS LG        |

| 19  | V.                                                                                                                                                                            | ELECTRONICS, INC. AND LG<br>ELECTRONICS U.S.A., INC.'S MOTION |

| 20  | LG ELECTRONICS, INC. AND LG                                                                                                                                                   | TO STRIKE INFRINGÉMENT<br>CONTENTIONS OR, ALTERNATIVELY,      |

| 21  | ELECTRONICS U.S.A., INC.,                                                                                                                                                     | COMPEL SUPPLEMENTAL INFRINGEMENT CONTENTIONS ON               |

| 22  | Defendants.                                                                                                                                                                   | CHARTED PROCESSORS                                            |

| 23  |                                                                                                                                                                               | DATE: June 30, 2015 (by order)<br>TIME: 10:00 AM              |

| 24  |                                                                                                                                                                               | PLACE: Courtroom 5                                            |

| 25  |                                                                                                                                                                               | JUDGE: Hon. Paul S. Grewal                                    |

| 26  |                                                                                                                                                                               |                                                               |

| 27  |                                                                                                                                                                               |                                                               |

|     | 1                                                                                                                                                                             |                                                               |

### **EXHIBIT G-1**

DECLARATION OF OLGA I. MAY IN SUPPORT OF

DEFENDANTS LG ELECTRONICS, INC. AND LG

ELECTRONICS U.S.A., INC.'S MOTION TO STRIKE

INFRINGEMENT CONTENTIONS OR, ALTERNATIVELY,

COMPEL SUPPLEMENTAL INFRINGEMENT

CONTENTIONS ON CHARTED PROCESSORS

#### Case3:12-cv-03880-VC Document97-2 Filed06/29/15 Page2 of 26

|                                                                                                                                                                                                             | Claim 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Claim<br>Element |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 6. A microprocessor system comprising:                                                                                                                                                                      | On information and belief, each Accused Product listed in the attached list of Accused Products (Ex. A.6), including phones and televisions, contains a <b>microprocessor</b> ("Accused Microprocessors"). For example, the Escape contains a Qualcomm MSM8960L. <i>See</i> Ex. A.6 for listings of microprocessors in the Accused Products with information obtained from <a href="http://www.phonescoop.com/">http://pdadb.net/</a> ; <a href="http://www.gsmarena.com/">http://www.gsmarena.com/</a> ; <a href="http://www.gsmarena.com/">see</a> PDSLG000001-PDSLG000050; <a href="http://www.gsmarena.com/">see also PDSND077821-PDSND078576</a> for datasheets identifying microprocessors. Each microprocessor is an electronic circuit that interprets and executes programmed instructions. | 6.a              |

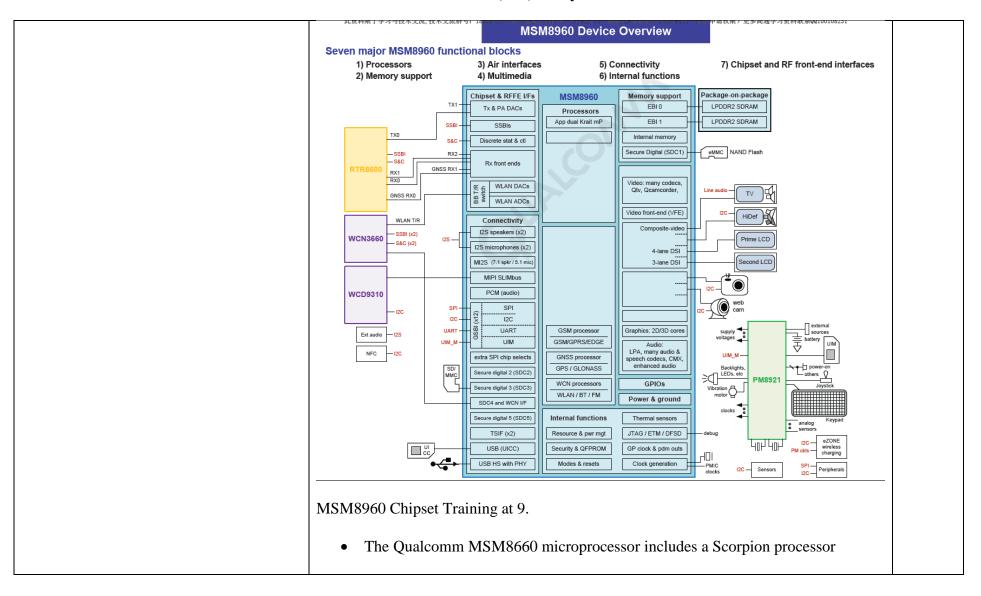

| a central processing unit disposed upon an integrated circuit substrate, said central processing unit operating at a processing frequency and being constructed of a first plurality of electronic devices; | On information and belief, each Accused Microprocessor in each Accused Product contains a <b>central processing unit</b> (CPU), which is an electronic circuit on an integrated circuit that controls the interpretation and execution of programmed instructions. <i>See</i> <a href="http://www.merriam-webster.com/dictionary/microprocessor">http://www.merriam-webster.com/dictionary/microprocessor</a> . Each CPU operates at a processing frequency. Each CPU and an entire oscillator are constructed on a single integrated circuit comprising semiconductor-based transistors, or electronic devices. An integrated circuit is a miniature circuit on a single semiconductor substrate.  For example:  • The Qualcomm MSM8960 microprocessor includes a Krait CPU.                        | 6.b              |

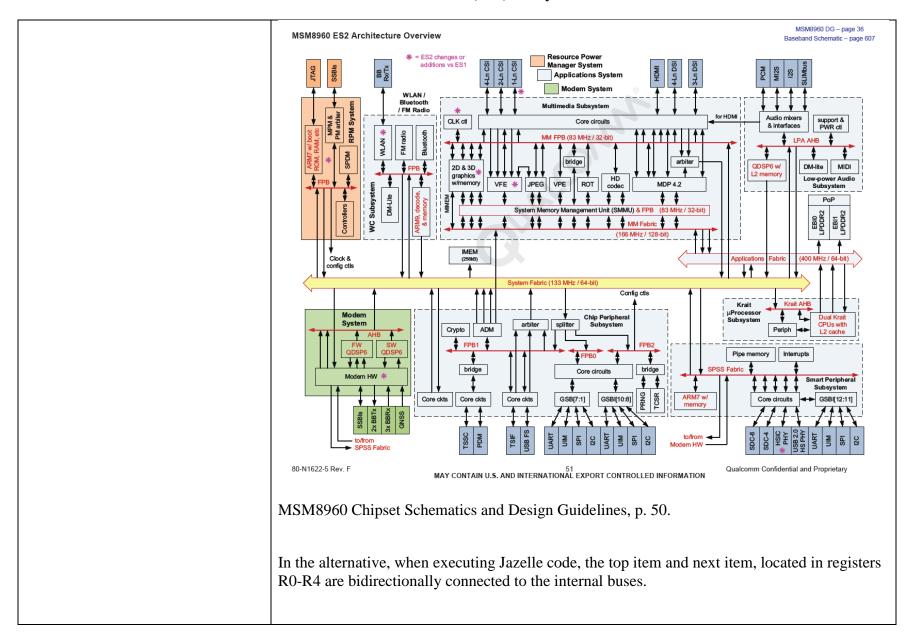

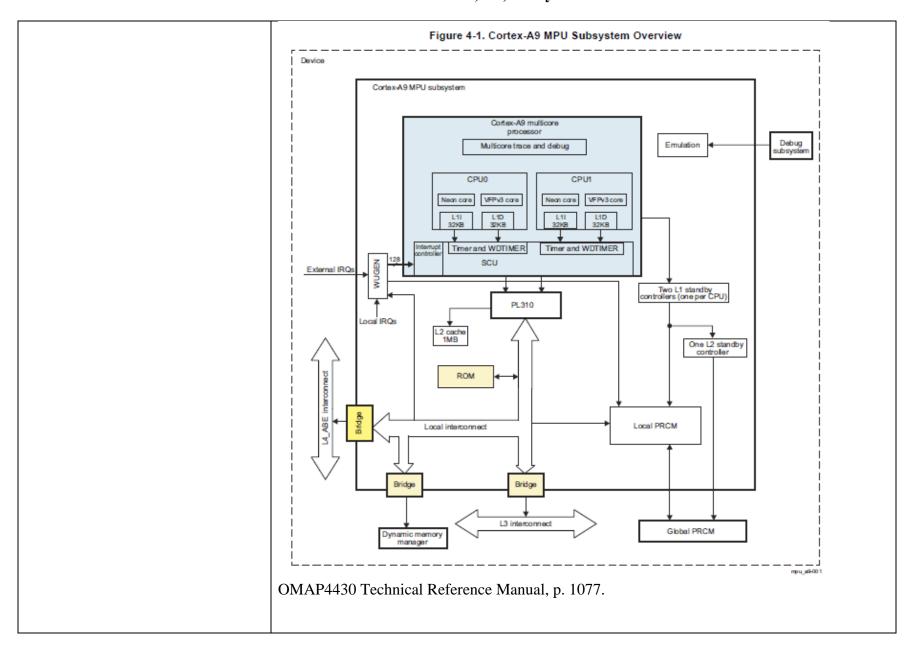

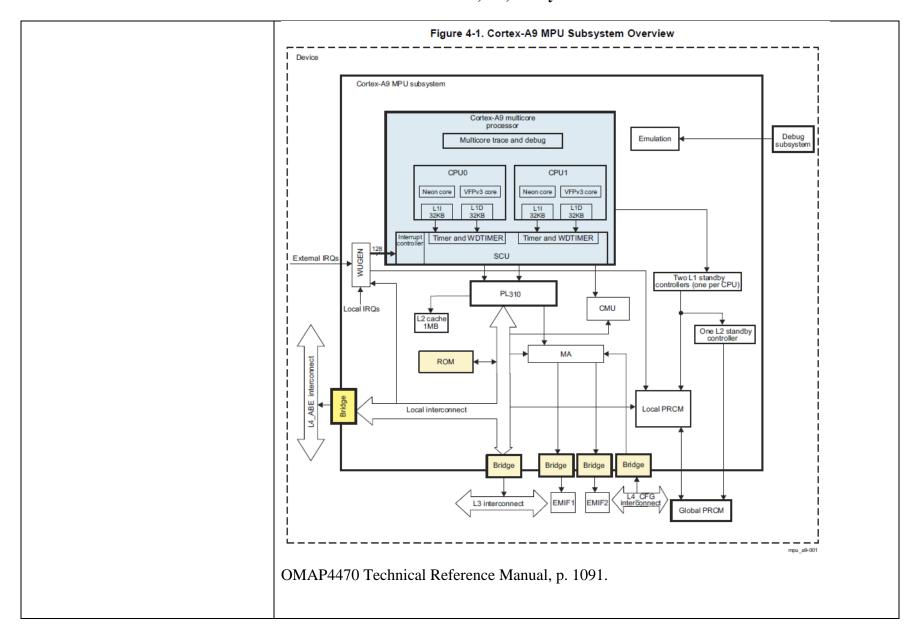

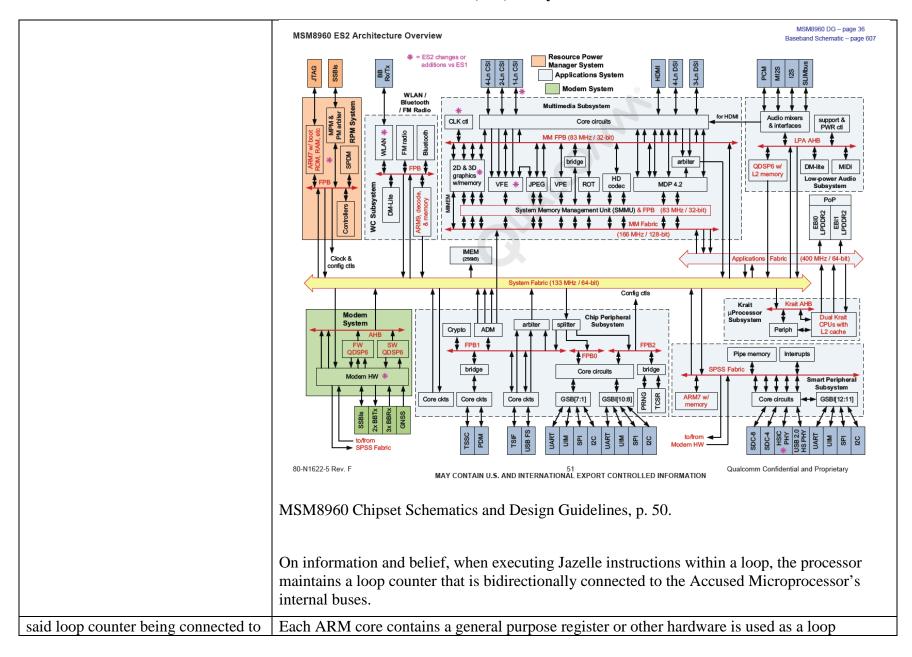

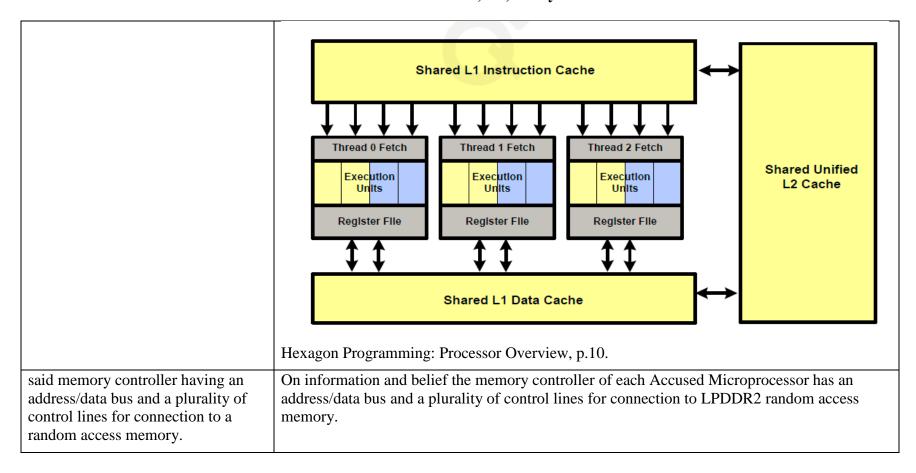

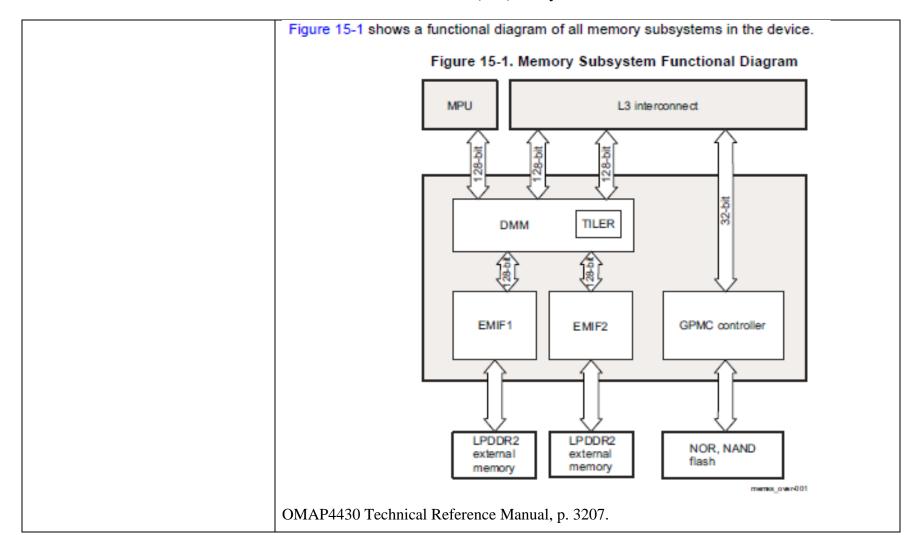

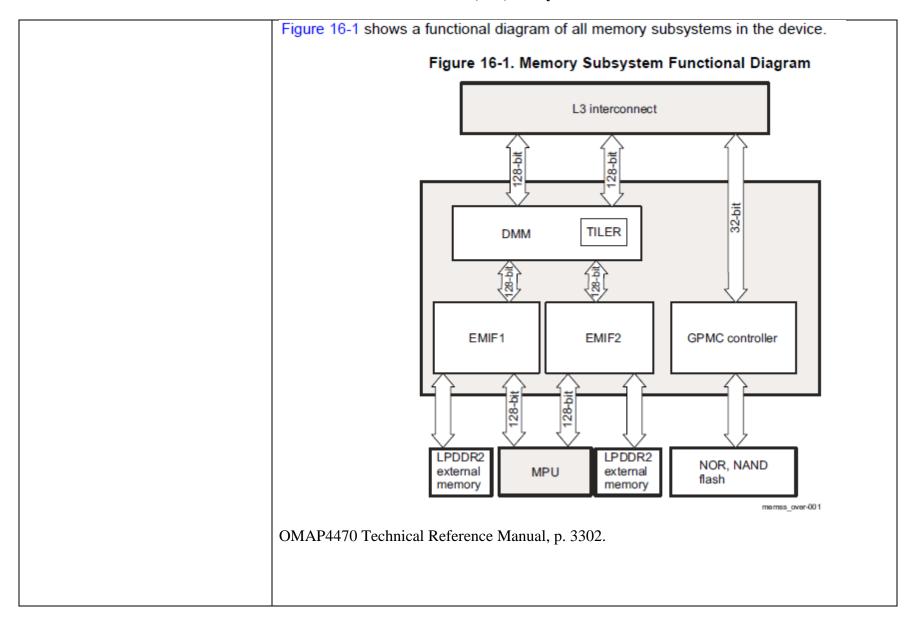

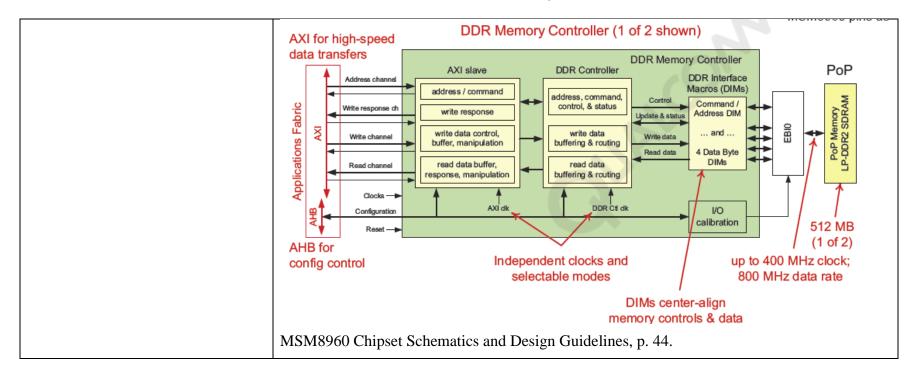

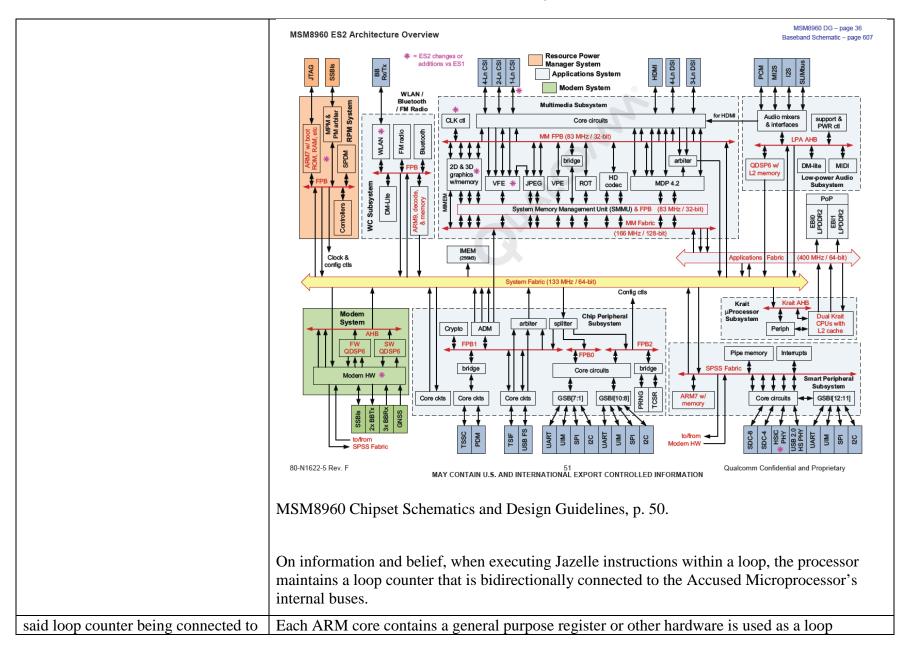

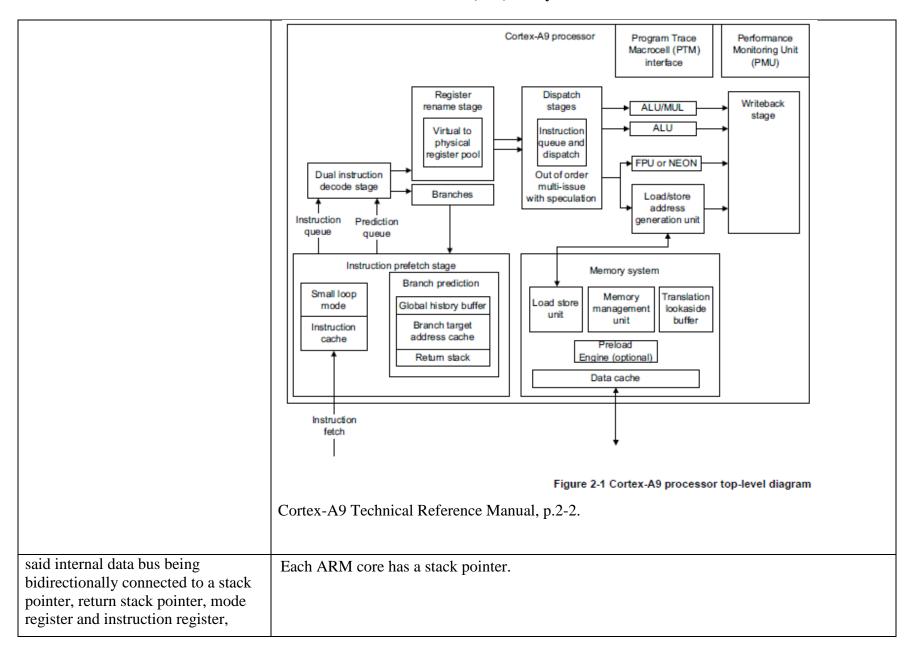

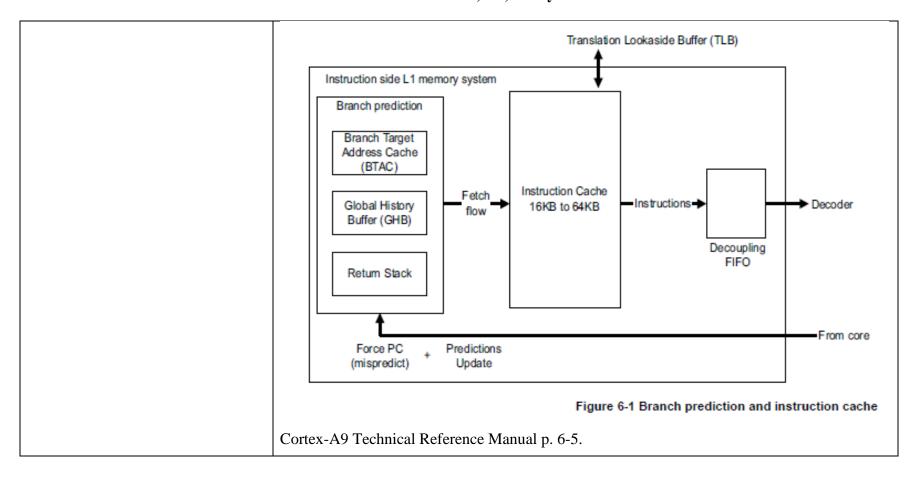

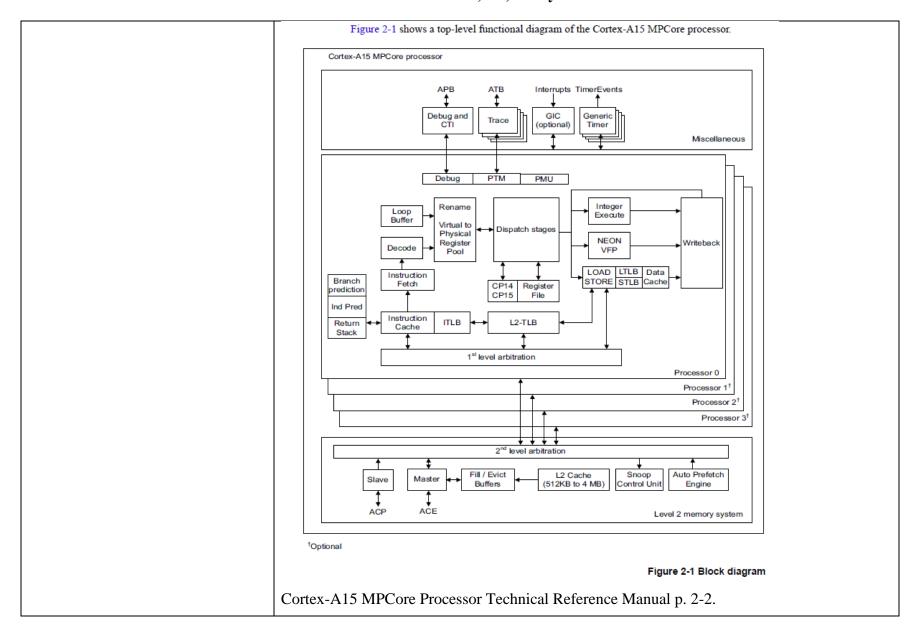

Infringement by the Accused Products is largely based on the operation of and implementation of the microprocessors they contain. This chart provides some examples of such operation that, on information and belief, are representative of the operation of the processors in each of the Accused Products. Discovery is in the early stages, and Plaintiffs anticipate receiving additional documents showing the exact operation of the processor in each of the Accused Products with respect to the accused functionality. But because many documents that Plaintiffs would rely on to establish infringement are confidential and have not yet been produced in this litigation, Plaintiffs anticipate receiving additional documents to confirm the operational principles shown in this chart from Defendants and/or third parties. Accordingly, Plaintiffs reserve the right to amend, supplement, or augment their claim charts, infringement contentions, or infringement theories based on documents and information later received through discovery.

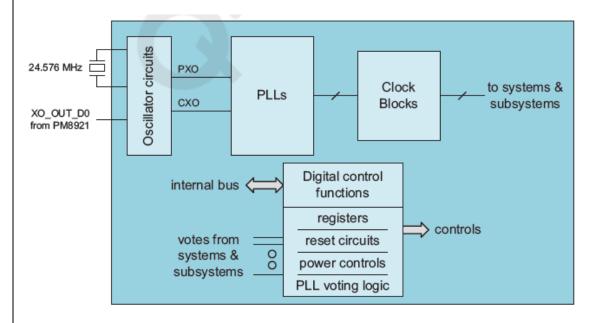

to said central processing unit, said oscillator clocking said central processing unit at a clock rate and being constructed of a second plurality of electronic devices,

the CPU, using PLL circuitry containing an **entire oscillator** disposed upon the integrated circuit substrate, connected to the CPU, and constructed of a second plurality of electronic devices. Each oscillator does not use any external clock to generate the signal used to clock the CPU.

#### For example:

• The MSM8960 clocks its CPU using PLL:

MSM8960 Chipset Schematics and Design Guidelines at 103-108.

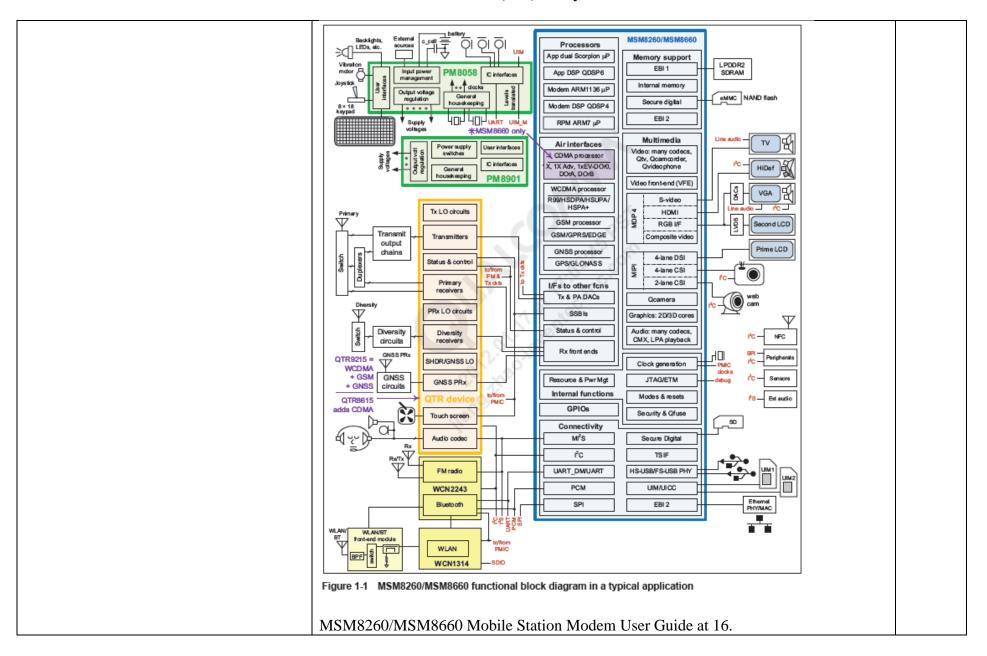

The MSM8660 clocks its CPU using PLL

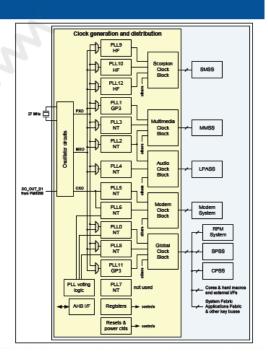

### Clock Generation and Distribution

- The on-chip PLLs (PLL0 through PLL12)

- PLL0 (reserved)

- PLL1 (multimedia PLL0)

- PLL2 (multimedia PLL1)

- PLL3 (multimedia PLL2)

- PLL4 (LPASS PLL)

- PLL5 (modem PLL0)

- PLL6 (modem PLL1)

- PLL7 (unused)

- PLL8 (peripheral PLL)

- PLL9 (SC1 PLL0)

- PLL10 (SC2 PLL1)

- PLL11 (EBI1 PLL)

- PLL12 (SC1/2 L2 PLL)

MSM8660 Mobile Station Modem Architecture and Features at 40; See also MSM8260/MSM8660 Mobile Station Modem User Guide at 72, 73 (Clock generation and distribution).

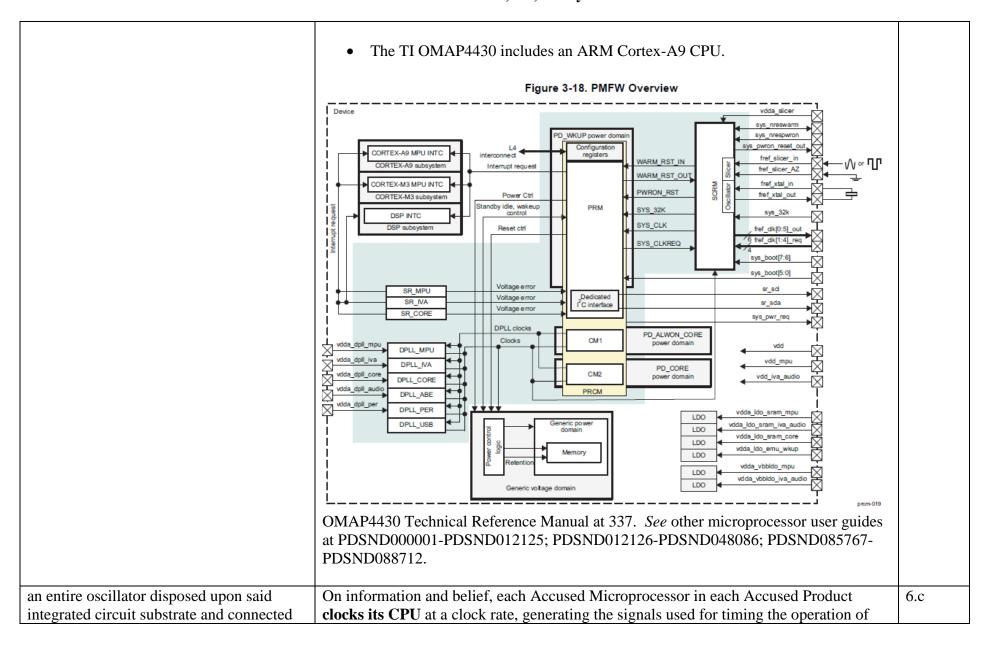

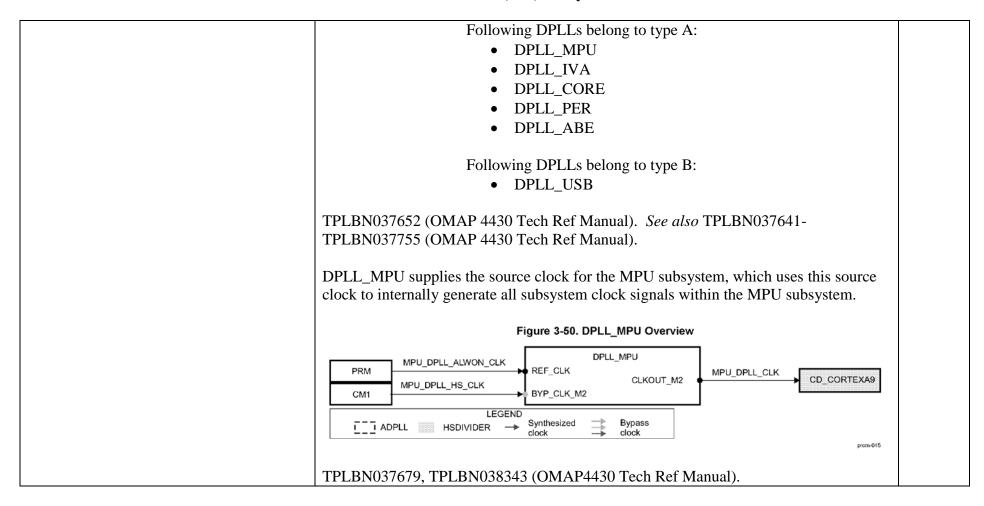

• The TI OMAP4430 clocks its CPU using PLL. The DPLL\_MPU generates a clock for the MPU subsystem.

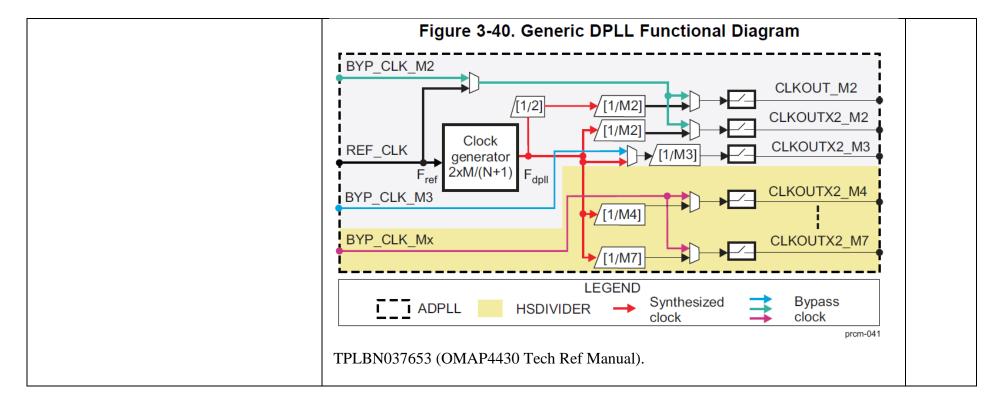

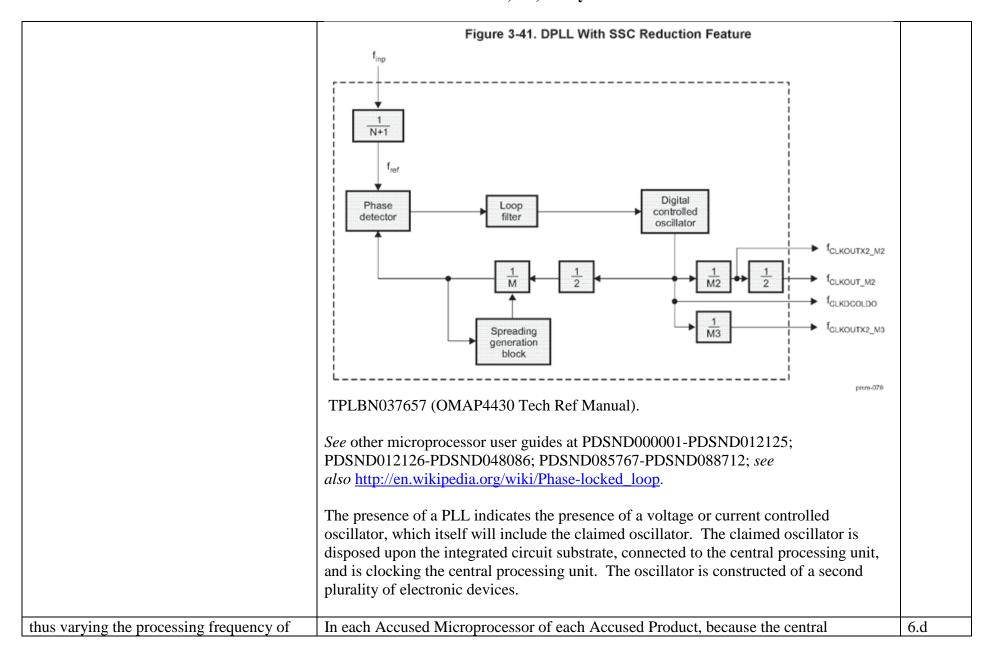

To generate high-frequency clocks, the device supports multiple on-chip DPLLs controlled directly by the PRCM module. They are of two types, identified as type A and type B DPLLs.

### Case3:12-cv-03880-VC Document97-2 Filed06/29/15 Page9 of 26

# EXHIBIT G-1 – CLAIM CHART FOR INFRINGEMENT OF U.S. PATENT NO. 5,809,336 By LG

| Clocks             |                            |                         |        |                                                                                        |  |

|--------------------|----------------------------|-------------------------|--------|----------------------------------------------------------------------------------------|--|

| Module<br>Instance | Destination Signal<br>Name | Source Signal<br>Name   | Source | Description                                                                            |  |

| CORTEXA9           | MPU_DPLL_CLK               | MPU_DPLL_CLK            | PRCM   | Interface and functional clock                                                         |  |

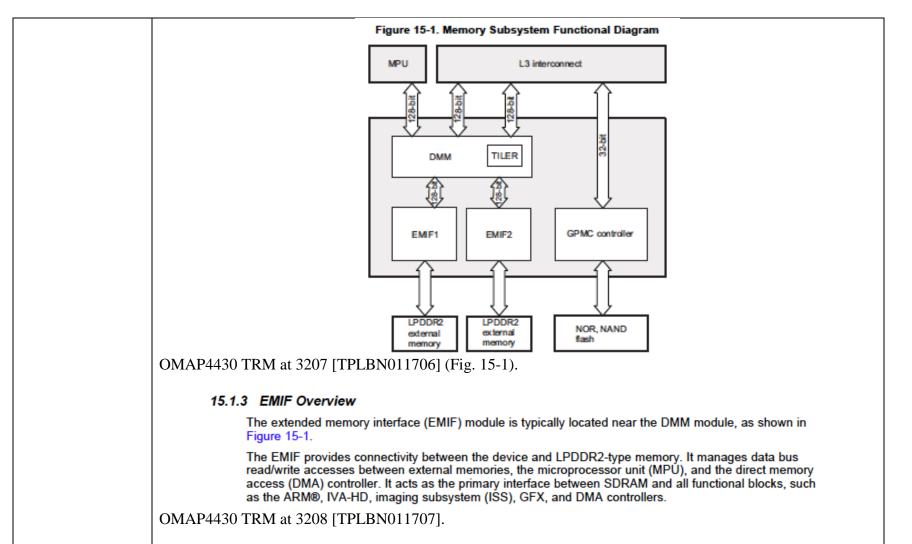

|                    |                            |                         | Resets |                                                                                        |  |