Nos. 2016-1306, -1307, -1309, -1310, -1311

## In the

# **United States Court of Appeals** for the Federal Circuit

TECHNOLOGY PROPERTIES LIMITED LLC, PHOENIX DIGITAL SOLUTIONS LLC, PATRIOT SCIENTIFIC CORPORATION,

Plaintiffs-Appellants,

v.

HUAWEI TECHNOLOGIES CO., LTD., FUTUREWEI TECHNOLOGIES, INC., HUAWEI DEVICE CO., LTD., HUAWEI DEVICE USA INC., HUAWEI TECHNOLOGIES USA INC., ZTE CORPORATION, ZTE USA, INC., SAMSUNG ELECTRONIC CO., LTD, SAMSUNG ELECTRONICS AMERICA, INC., LG ELECTRONICS, INC., LG ELECTRONICS U.S.A., INC., NINTENDO CO., LTD., NINTENDO OF AMERICA INC.,

Defendants-Appellees.

Appeal from the United District Court for the Northern District of California, Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, and 3:12-cv-03881-VC. The Honorable **Vince Chhabria**, Judge Presiding.

## **CORRECTED JOINT APPENDIX**

WILLIAM L. BRETSCHNEIDER SILICON VALLEY LAW GROUP 50 W. San Fernando Street Suite 750 San Jose, California 95113 (408) 573-5700

Counsel for Technology Properties Limited LLC BARRY J. BUMGARDNER NELSON BUMGARDNER, P.C. 3131 West 7th Street Suite 300 Fort Worth, Texas 76107 (817) 377-9111

Counsel for Phoenix Digital Solutions LLC

CHARLES T. HOGE KIRBY NOONAN LANCE & HOGE LLP 350 Tenth Avenue, Suite 1300 San Diego, California 92101 (619) 231-8666

Counsel for Patriot Scientific Corporation

#### (ADDITIONAL COUNSEL LISTED ON REVERSE SIDE)

TIMOTHY C. BICKHAM STEPTOE & JOHNSON, LLP 1330 Connecticut Avenue, NW Washington, DC 20036 (202) 429-5517 CHARLES M. MCMAHON HERSH H. MEHTA MCDERMOTT, WILL & EMERY LLP 227 West Monroe Street, 44th Floor Chicago, IL 60606 (312) 372-2000

Counsel for Defendants-Appellees Huawei Technologies Co., Ltd.; Futurewei Technologies, Inc.; Huawei Device Co., Ltd.; Huawei Device USA Inc.; Huawei Technologies USA Inc.

*Counsel for Defendants-Appellees ZTE Corporation; ZTE USA, Inc.*

MARK D. FOWLER AARON WAINSCOAT ERIK RYAN FUEHRER DLA PIPER US LLP 2000 University Avenue East Palo Alto, CA 94303-2248 (650) 833-2045 JAMES M. HEINTZ DLA PIPER US LLP One Fountain Square 11911 Freedom Drive Reston, VA 20190-5602 (703) 773-4000 STANLEY JOSEPH PANIKOWSKI III ROBERT CHEN WILLIAMS DLA PIPER LLP (US) Suite 1700 401 B Street San Diego, CA 92101 (619) 699-2643

Counsel for Defendants-Appellees Samsung Electronic Co., Ltd.; Samsung Electronics America, Inc.

CHRISTIAN A. CHU SCOTT A. ELENGOLD FISH & RICHARDSON, PC 1425 K Street, NW Washington, DC 20005 (202) 783-5070

Counsel for Defendants-Appellees LG Electronics, Inc.; LG Electronics U.S.A., Inc.

STEPHEN R. SMITH COOLEY LLP Suite 700 1299 Pennsylvania Avenue, NW Washington, DC 20004 (703) 456-8035 MATTHEW J. BRIGHAM COOLEY LLP Suite 400 3175 Hanover Street Palo Alto, CA 94304 (650) 843-5000

Counsel for Defendants-Appellees Nintendo Co., Ltd.; Nintendo of America, Inc.

# TABLE OF CONTENTS TOJOINT APPENDIX1

#### Appeal Nos. 2016-1306, -1307, -1309, -1310, -1311 **TECHNOLOGY PROPERTIES LIMITED LLC, ET AL. v.** HUAWEI TECHNOLOGIES CO., LTD., ET AL. Final Judgment (Dkt. No. 110) Appx1-Appx3 Order Adopting Magistrate Judge's Report and Appx4-Appx5 Recommendation (Dkt. No. 108) Claim Construction Report and Appx6-Appx17 Recommendation (Dkt. No. 98) U.S. Patent No. 5,809,336 Appx18-Appx70 Appx91-Appx92-22 Docket sheet in Technology Properties Ltd., et al. v. Huawei Technologies Co., Ltd., et al., Case No. 3:12-cv-03865-VC (PSG) Appx1459-1463; Patent Local Rule 4-3 Joint Claim Construction and Prehearing Statement, Exhibit A Appx1469 First Claim Construction Order, HTC Corp. v. Appx1563-Appx1566; Technology Properties Ltd., et al., 3:08- cv-882 Appx 1588 (Dkt. No. 364 at 13-16) (N.D. Cal., June 12, 2012) (the "Ware Markman Order") Claim Construction Order, HTC (Dkt. No. 509) Appx1606-Appx1623 (N.D. Cal., August 21, 2013) (the "HTC Grewal Markman Order") Order No. 31, Construing the Terms of the Appx1661-Appx1743 Asserted Claims of the Patent at Issue, ITC Investigation No. 337-TA-853 (April 18, 2013)

(the "ITC Markman Order")

<sup>&</sup>lt;sup>1</sup> To avoid overburdening the Court, and by stipulation of the parties, the following bulk page ranges cited in Plaintiffs-Appellants' Opening Brief have been omitted from the Joint Appendix, and can be furnished to the Court upon request:

Appx3258-3495 Appx3504-3520 Appx3550-4337

Point citations within these ranges are included.

| Plaintiffs' Motion for Summary Judgment of            | Appx1745-1770         |

|-------------------------------------------------------|-----------------------|

| Non-Infringement, <i>HTC</i> (Dkt. No. 457) (July     | прря (45 1770         |

| 16, 2013)                                             |                       |

| Summary Judgment Order, <i>HTC</i> (Dkt. No. 585)     | Appx1772-Appx1794     |

| (September 17, 2013)                                  | rippar / 2 rippar / ) |

| HTC Emergency Motion, <i>HTC</i> (Dkt. No. 590)       | Appx1796-Appx1798     |

| (September 18, 2013)                                  |                       |

| Defendants' Opposition to Emergency Motion            | Appx1800-Appx1806     |

| for Addendum to Jury Instructions, <i>HTC</i> (Dkt.   |                       |

| No. 596) (September 18, 2013)                         |                       |

| Emergency Motion Order, <i>HTC</i> (Dkt. No. 607)     | Appx1808-Appx1809     |

| (September 20, 2013)                                  | rippillooo rippilloos |

| Order Denying Plaintiffs' Renewed Motion for          | Appx1811-Appx1825     |

| Entry of Judgment as a Matter of Law, <i>HTC</i>      | - PP PP               |

| (Dkt. No. 707) (January 21, 2014)                     |                       |

| Defendants' Opening Claim Construction Brief          | Appx1962              |

| U.S. Patent No. 4,503,500 (" <i>Magar</i> ")          | Appx2042-Appx2074     |

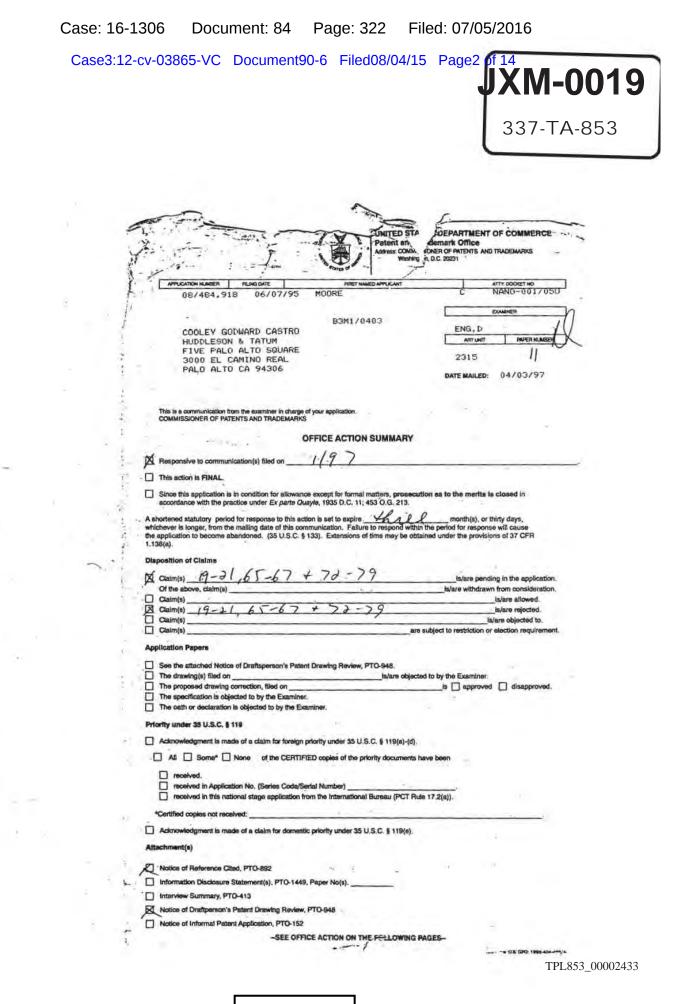

| Office Action (April 3, 1997)                         | Appx2076-Appx2077     |

| Response to Office Action (mailed July 3,             | Appx2090-2097         |

| 1997)                                                 |                       |

| Response to Office Action (mailed February 6,         | Appx2099-Appx2108     |

| 1998)                                                 |                       |

| Response to Office Action (mailed April 11,           | Appx2110-2122         |

| 1996)                                                 |                       |

| Response to Office Action (mailed January 8,          | Appx2124-Appx2138     |

| 1997)                                                 |                       |

| Final Jury Instructions, HTC (Dkt. No. 646)           | Appx2209              |

| Order Granting Emergency Motion for                   | Appx2230-Appx2231     |

| Clarification of Order on Addendum to Jury            |                       |

| Instructions, HTC (Dkt. No. 616) (September           |                       |

| 23, 2013)                                             |                       |

| Memorandum and Order, Technology                      | Appx2233-Appx2260     |

| Properties Ltd. et al. v. Matsushita Elec. Indus.     |                       |

| <i>Co., Ltd., et al.</i> , Case No. 2:05-cv-494 (Dkt. |                       |

| No. 259) (E.D. Tex., June 15, 2007) (the              |                       |

| "Texas Markman Order")                                |                       |

| ITC Claim Construction Order                          | Appx2285-Appx2304     |

| Commission Opinion, Inv. No. 337-TA-853               | Appx2368, Appx2373-   |

| (March 21, 2014) ("Commission Opinion")               | Appx2374              |

| Transcript of Proceedings held on October 2,       | Appx2446-Appx2452   |

|----------------------------------------------------|---------------------|

| 2013, before Paul S. Grewal, Magistrate Judge      |                     |

| (" <i>HTC</i> Trial Transcript")                   |                     |

| ITC Initial Determination                          | Appx2483-Appx2485,  |

|                                                    | Аррх2596            |

| Plaintiffs Responsive Claim Construction Brief     | Appx2908-Appx2920   |

| (Dkt. No. 92)                                      | прря2900 трря2920   |

| Plaintiffs' Motion for De Novo Determination       | Appx3237-Appx3257   |

| of Dispositive Matter Referred to Magistrate       |                     |

| Judge, or, in the Alternative, Motion for Relief   |                     |

| from Nondispositive Pretrial Order of              |                     |

| Magistrate Judge (Dkt. No. 105)                    |                     |

| U.S. Patent No. 4,670,837 ("Sheets")               | Appx3496-Appx3503   |

| Defendants' Response to Plaintiffs' Motion for     | Appx3521-Appx3549   |

| De Novo Determination of Dispositive Matter        |                     |

| Referred to Magistrate Judge, or, in the           |                     |

| Alternative, Motion for Relief from                |                     |

| Nondispositive Pretrial Order of Magistrate        |                     |

| Judge (Dkt. No. 106)                               |                     |

| Transcript of Proceedings held on September        | Appx4345-Appx4348,  |

| 18, 2015, before Paul S. Grewal, Magistrate        | Appx4357-4360,      |

| Judge ("Markman Hearing Transcript")               | Appx4362, Appx4364, |

|                                                    | Appx4378-Appx4379   |

| Stipulation for Entry of Final Judgment Based      | Appx4468-Appx4479   |

| on the Court's Claim Construction (Dkt. No.        | ** **               |

| 109)                                               |                     |

| Notice of Appeal (Dkt. No. 112) (December 7, 2015) | Appx4480-Appx4483   |

## Case: 16-1306 Document: 84 Page: 8 Filed: 07/05/2016

Case 3:12-cv-03865-VC Document 110 Filed 11/13/15 Page 3 of 3

Huawei Device Co., Ltd., Huawei Device USA, Inc., Futurewei Technologies, Inc., Huawei

Technologies USA, Inc., ZTE Corporation, ZTE (USA) Inc., Samsung Electronics Co., Ltd.,

Samsung Electronics America, Inc., LG Electronics, Inc., LG Electronics U.S.A., Inc., Nintendo

Co., Ltd., and Nintendo of America, Inc. (collectively, "Defendants") (together, the "Parties")

have stipulated that all Defendants are entitled to a judgment of non-infringement as a matter of

law as to all of Plaintiffs' asserted claims of the '336 patent in the above-titled and numbered civil

cases (collectively, "this Action").

Accordingly, the Court enters Judgment as follows:

9 Judgment is entered against Plaintiffs and for Defendants as to Plaintiffs' claims for

10 patent infringement with respect to the '336 patent, subject to the parties' right to appeal.

Subject to the parties' right to appeal, the Court further enters judgment for Defendants

and against Plaintiffs on Defendants' respective counterclaims seeking declaratory judgment of

non-infringement and Defendants' respective affirmative defenses of non-infringement, and

declares the '336 patent not infringed by Defendants. Plaintiffs shall take nothing from

Defendants with respect to the asserted claims of the '336 patent.

All other claims, counterclaims, defenses, or other matters which have been asserted,

including Defendants' counterclaims of patent invalidity, are dismissed without prejudice.

Each party shall bear its own costs and attorneys' fees.

IT IS SO ORDERED

Dated: November <u>13</u>, 2015

8

19

20

21

22

23

24

25

26

27

28

VINCE CHHABRIA United States District Judge

#### Аррх3

Case: 16-1306 Document: 84 Page: 10 Filed: 07/05/2016 Case 3:12-cv-03865-VC Document 108 Filed 11/09/15 Page 2 of 2 TECHNOLOGY PROPERTIES LIMITED Case No. 12-cv-03880-VC 1 LLC, et al., Re: Dkt. Nos. 117, 120 Plaintiffs, 2 3 v. 4 LG ELECTRONICS, INC., et al., 5 Defendants. 6 TECHNOLOGY PROPERTIES LIMITED 7 Case No. 12-cv-03881-VC LLC, et al., Re: Dkt. Nos. 106, 109 8 Plaintiffs, 9 v. 10 NINTENDO CO., LTD, et al., 11 Defendants. 12 The Court agrees with the plaintiffs that de novo review of the Magistrate Judge's Report 13 and Recommendation is warranted. Having reviewed the Report and Recommendation de novo, 14 the Court adopts it without modification. 15 16 IT IS SO ORDERED. 17 Dated: November 9, 2015 18 19 VINCE CHHABRIA United States District Judge 20 21 22 23 24 25 26 27 28 2 Appx5

United States District Court Northern District of California

| Case: 16-1306 Document: 84 Pa                                                                           | ge: 11 Filed: 07/05/2016                       |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Case3:12-cv-03865-VC Document98 F                                                                       | -iled09/22/15 Page1 of 12                      |

|                                                                                                         |                                                |

|                                                                                                         |                                                |

|                                                                                                         |                                                |

|                                                                                                         |                                                |

|                                                                                                         |                                                |

|                                                                                                         |                                                |

| UNITED STATES D                                                                                         | DISTRICT COURT                                 |

| NORTHERN DISTRIC                                                                                        | T OF CALIFORNIA                                |

| SAN JOSE I                                                                                              | DIVISION                                       |

| TECHNOLOGY PROPERTIES LIMITED LLC, )                                                                    | Case No. 3:12-cv-03865-VC                      |

| et al., )<br>Plaintiffs, )                                                                              | CLAIM CONSTRUCTION REPOR<br>AND RECOMMENDATION |

| v. )                                                                                                    |                                                |

| HUAWEI TECHNOLOGIES CO., LTD., et al., )                                                                |                                                |

| )<br>Defendants.                                                                                        |                                                |

| TECHNOLOGY PROPERTIES LIMITED LLC,)<br>ET AL.,                                                          | Case No. 3:12-cv-03876-VC                      |

| )<br>PLAINTIFFS, )                                                                                      |                                                |

| V. )                                                                                                    |                                                |

| ZTE CORPORATION, et al.,                                                                                |                                                |

| DEFENDANTS.                                                                                             |                                                |

| TECHNOLOGY PROPERTIES LIMITED LLC,)<br>ET AL.,                                                          | Case No. 3:12-cv-03877-VC                      |

| PLAINTIFFS,                                                                                             |                                                |

| V. )                                                                                                    |                                                |

| )<br>SAMSUNG ELECTRONICS CO., LTD., et al., )                                                           |                                                |

| )<br>DEFENDANTS. )                                                                                      |                                                |

| )                                                                                                       |                                                |

| 1<br>Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC,<br>cv-03881-VC<br>CLAIM CONSTRUCTION REPORT AND RECO |                                                |

| Appx6                                                                                                   |                                                |

United States District Court For the Northern District of California

Case: 16-1306 Document: 84 Page: 12 Filed: 07/05/2016 Case3:12-cv-03865-VC Document98 Filed09/22/15 Page2 of 12 TECHNOLOGY PROPERTIES LIMITED LLC,) Case No. 3:12-cv-03880-VC 1 ET AL., 2 PLAINTIFFS, 3 V. 4 LG ELECTRONICS, INC., et al., 5 DEFENDANTS. 6 TECHNOLOGY PROPERTIES LIMITED LLC, Case No. 3:12-cv-03881-VC 7 ET AL., 8 PLAINTIFFS, 9 V. 10 NINTENDO CO., LTD., et al., 11 DEFENDANTS. 12 13 The parties to this patent infringement suit dispute the construction of just one claim term in 14 U.S. Patent No. 5,809,336: "an entire oscillator disposed upon said integrated circuit substrate."<sup>1</sup> 15 At issue is the impact of various statements made by the patent applicant to the examiner during 16 the patent's prosecution. Because these statements would be understood by one of ordinary skill in 17 the art as disclaiming certain scope of the disputed "entire oscillator" term, the court 18 RECOMMENDS construction of the term to reflect this disclaimer, as follows: "an [oscillator] 19 located entirely on the same semiconductor substrate as the [central processing unit] that does not 20 require a control signal and whose frequency is not fixed by any external crystal." 21 I. 22 Consistent with the Supreme Court's admonition in 1886 that a patent claim not be "a nose 23 of wax, which may be turned and twisted in any direction,"<sup>2</sup> the Federal Circuit has long held that a 24 claim term must be understood as limited if the applicant argued as much during prosecution in 25 <sup>1</sup> See Docket No. 89 at 6-7. 26 <sup>2</sup> White v. Dunbar, 119 U.S. 47, 51 (1886). 27 28 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-

United States District Court For the Northern District of California

cv-03881-VC

## Appx7

CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

## Case: 16-1306 Document: 84 Page: 13 Filed: 07/05/2016

Case3:12-cv-03865-VC Document98 Filed09/22/15 Page3 of 12

| 1 | order to overcome prior art. <sup>3</sup> "[T]he prosecution history can often inform the meaning of the claim |

|---|----------------------------------------------------------------------------------------------------------------|

| 2 | language by demonstrating whether the inventor limited the invention in the course of                          |

| 3 | prosecution, making the claim scope narrower than it would otherwise be."" <sup>4</sup>                        |

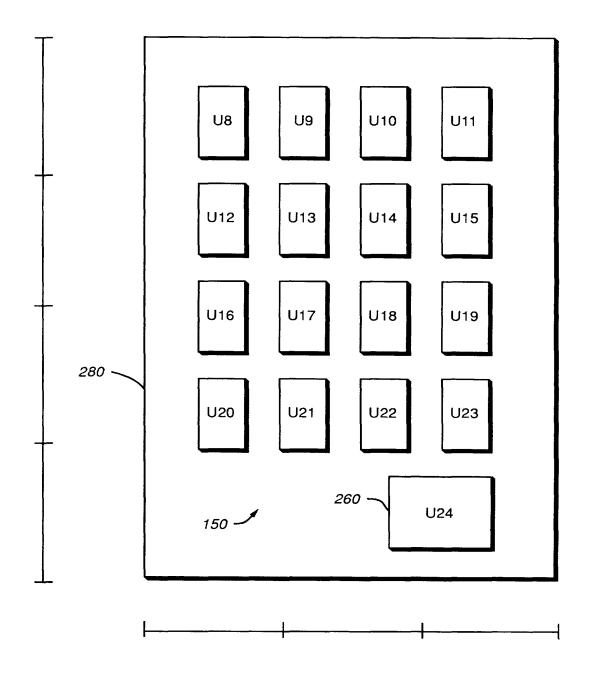

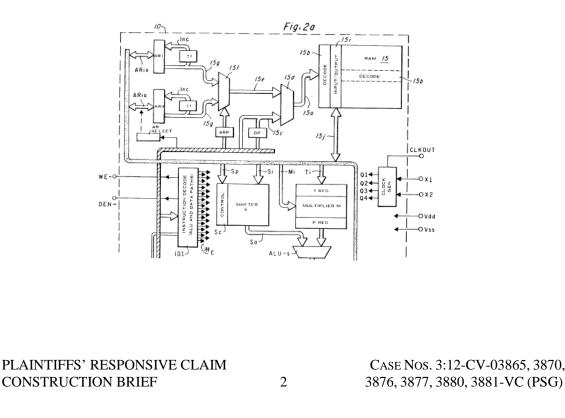

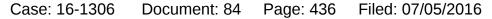

Plaintiff Technology Property Limited and Patriot Scientific brought these patent infringement suits for infringement of three patents: U.S Patent Nos. 5,440,749, 5,530,890 and 5,809,336. Only the '336 patents remains at issue; the others were dismissed by stipulation.<sup>5</sup> The '336 patent, titled "High Performance Microprocessor Having Variable Speed System Clock," was derived along with the others from a single patent application that was subject to nothing less than a ten-way restriction requirement. The result is that the '336 specification includes much discussion that is irrelevant to that which the '336 patent specifically claims.<sup>6</sup>

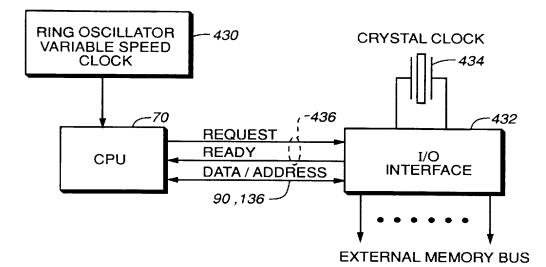

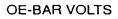

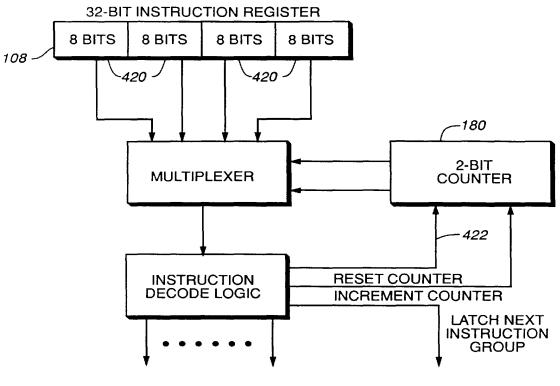

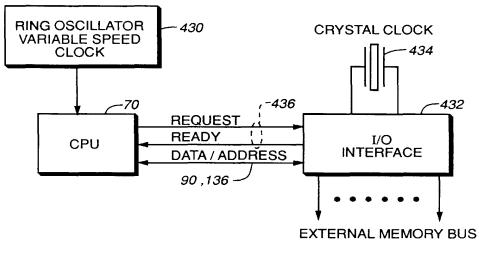

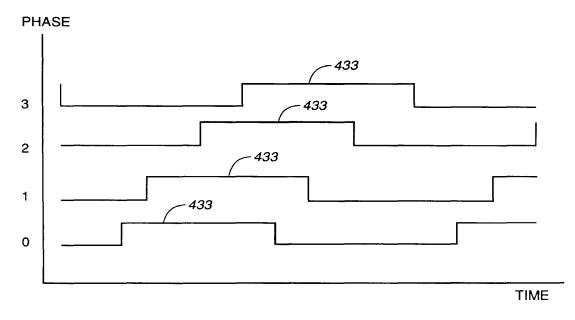

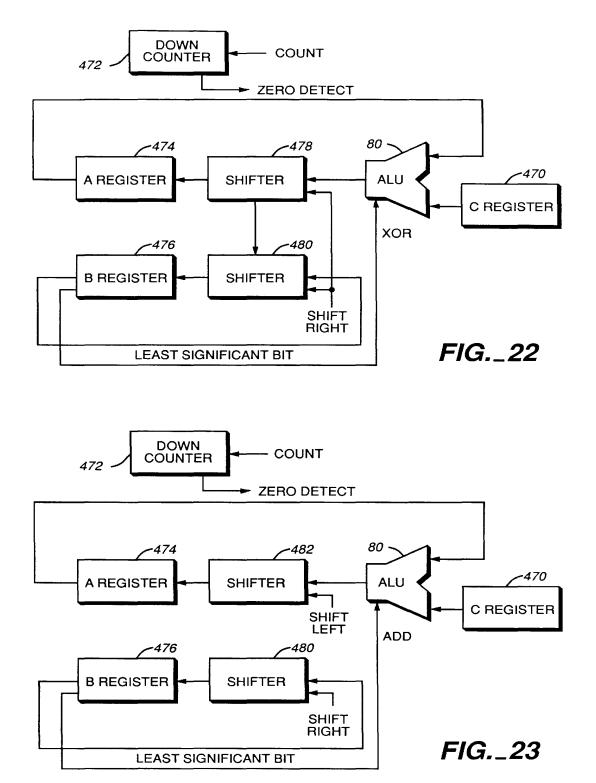

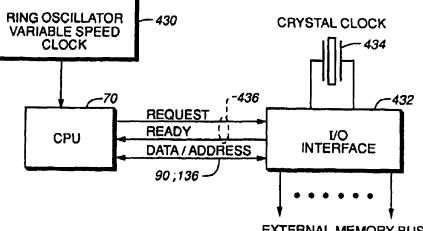

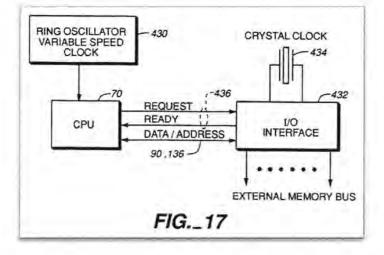

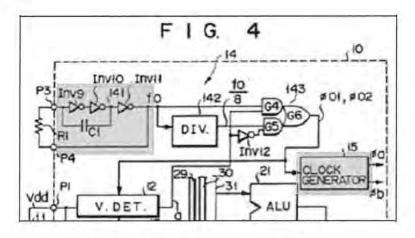

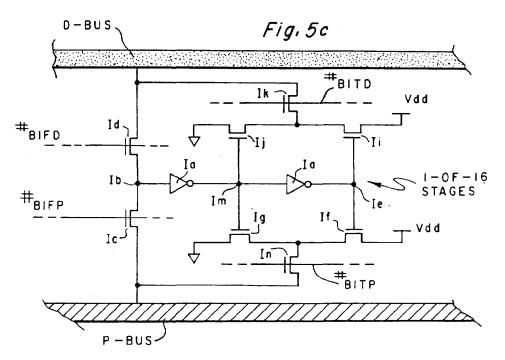

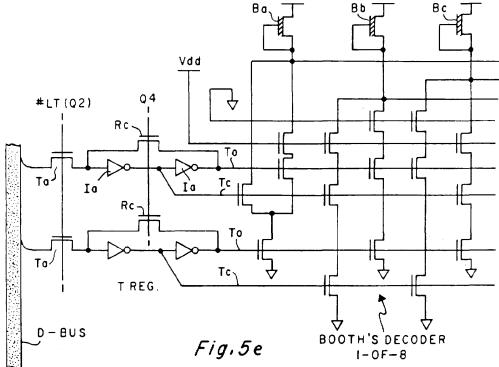

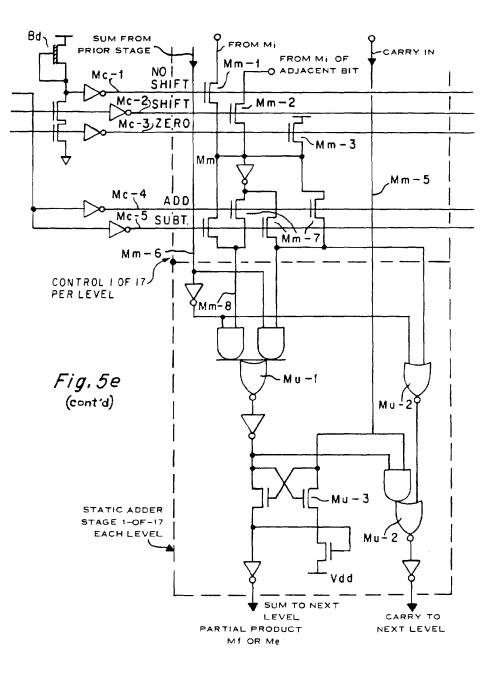

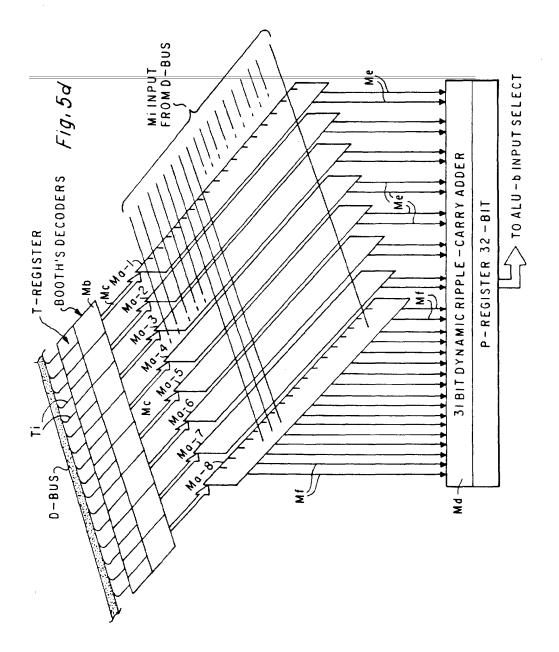

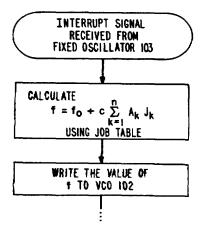

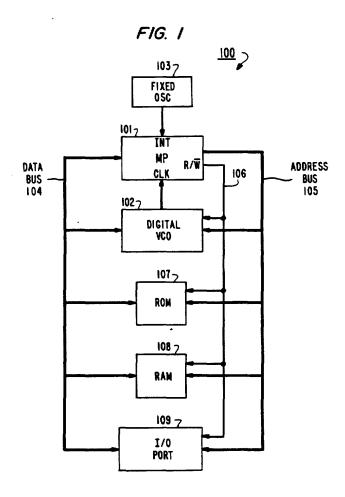

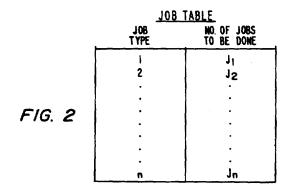

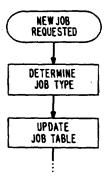

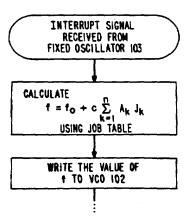

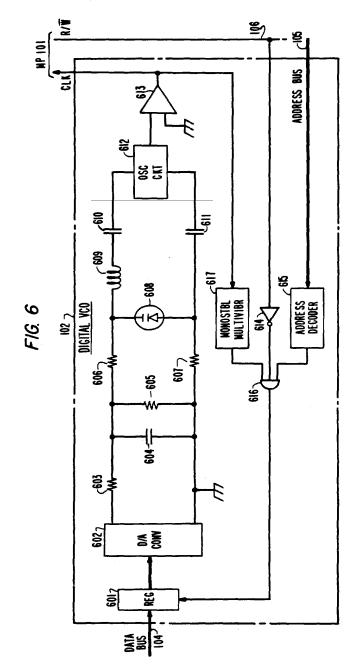

The '336 patent claims an invention that allows the frequency of a central processing unit, the brains of any computing device, to fluctuate based on local conditions. Traditional microprocessors use off-chip, fixed frequency clocks to regulate the CPU's frequency.<sup>7</sup> One result is that the clock needs to be set lower than the CPU's maximum possible frequency to ensure proper operation under worst-case conditions. The '336 patent solves this problem by placing a ring oscillator on the same silicon substrate as the CPU to act as the CPU's clock. Because the ring oscillator is on the same silicon substrate and is made of the same components as the CPU, it is

subject to the same environmental conditions and thus will allow the CPU to operate at higher rates

<sup>3</sup> See, e.g., Southwall Techs., Inc. v. Cardinal IG Co., 54 F.3d 1570, 1576 (Fed. Cir. 1995); see also Rheox, Inc. v. Entact, Inc., 276 F.3d 1319, 1325 (Fed. Cir. 2002) ("Explicit arguments made during prosecution to overcome prior art can lead to a narrow claim interpretation because '[t]he public has a right to rely on such definitive statements made during prosecution."") (quoting *Digital Biometrics, Inc. v. Identix, Inc.*, 149 F.3d 1335, 1347 (Fed. Cir. 1998)).

- <sup>4</sup> Abbott Labs. v. Sandoz, Inc., 566 F.3d 1282, 1289 (Fed. Cir. 2009) (quoting Phillips v. AWH Corp., 415 F.3d 1303, 1317 (Fed. Cir. 2005) (en banc)).

- <sup>5</sup> See Docket No. 86; all docket references are to Case No. 3:12-cv-03865-VC.

- 26 <sup>6</sup> See, e.g., Docket No. 28-3, Ex. C at 3:27-35, 16:43-17:37.

- 27 <sup>7</sup> See Docket No. 28-3, Ex. C at 16:48-50, 17:12-13.

- 3 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

## Appx8

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

28

## Case: 16-1306 Document: 84 Page: 14 Filed: 07/05/2016

Case3:12-cv-03865-VC Document98 Filed09/22/15 Page4 of 12

during good conditions and lower rates during bad. As the specification explains, the

microprocessor may "operate over wide temperature ranges, wide voltage swings, and wide

variations in semiconductor processing" that "all affect transistor gate propagation delays."<sup>8</sup>

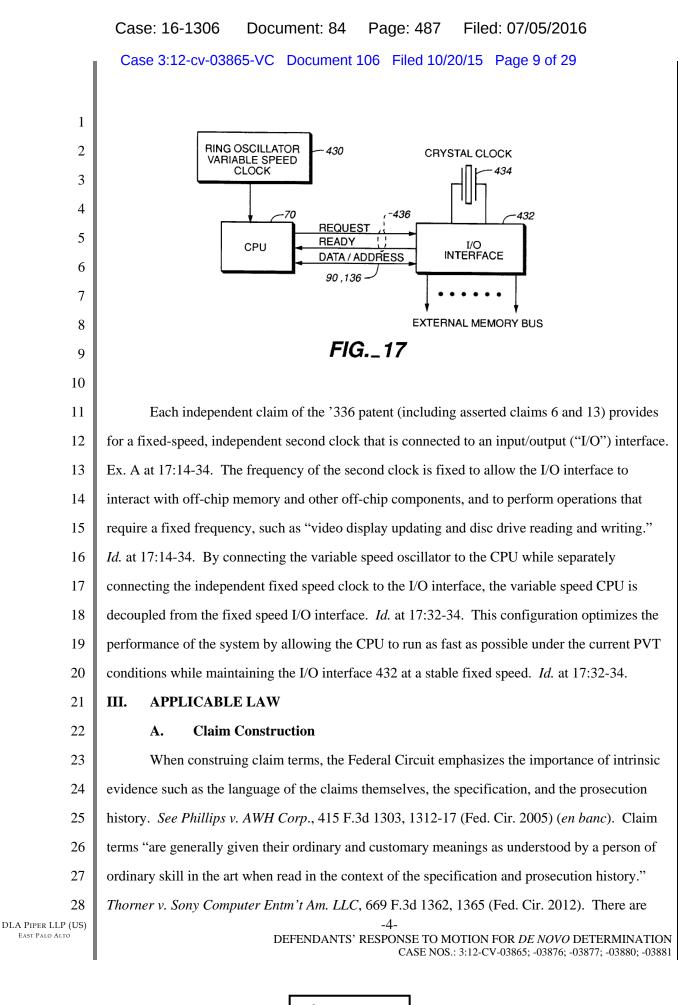

Because other devices with which the microprocessor communicates, both on-chip and off chip, cannot tolerate a variable speed clock, a second, conventional "crystal clock" is separately

connected to the input/output interface.<sup>9</sup>

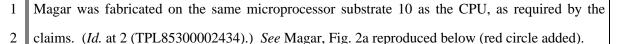

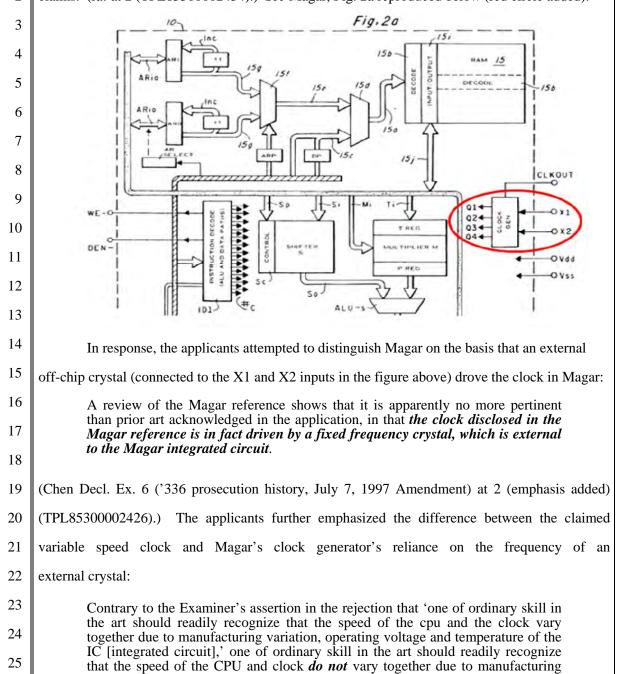

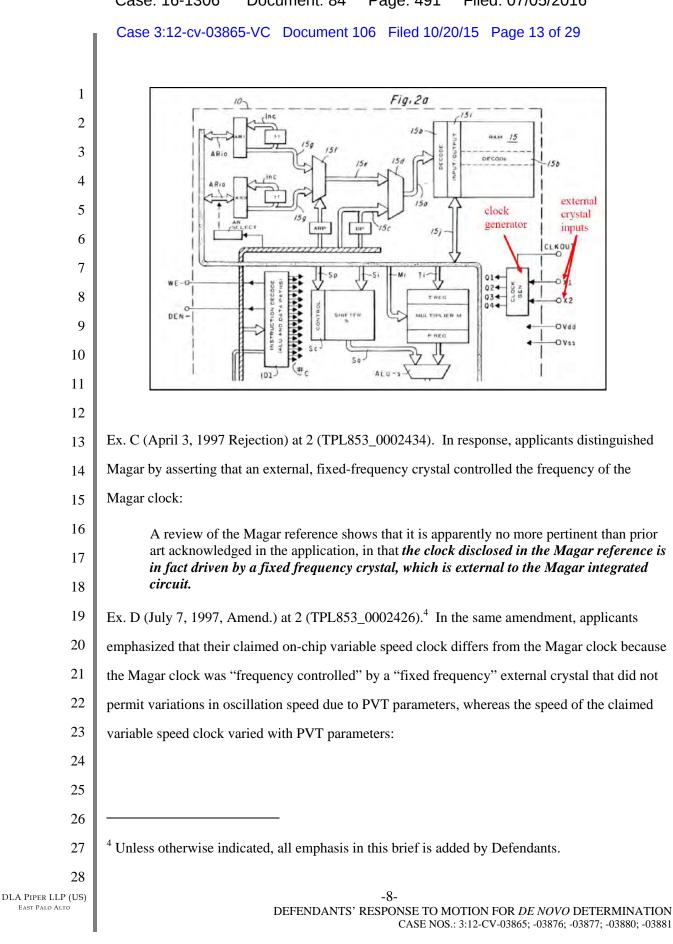

During the '336 patent's prosecution, the applicants made a variety of arguments to the examiner to overcome two key prior art references: U.S. Patent No. 4,503,500 ("Magar") and U.S. Patent No. 4,670,837 ("Sheets"). With respect to Magar, the examiner initially rejected the claims after noting that certain circuitry in Magar was fabricated on the same microprocessor substrate as the CPU, as required by the claims. The applicants then attempted to distinguish Magar by emphasizing that the clock disclosed in Magar was fixed by a crystal that was external to the microprocessor, unlike their on-chip variable speed clock:

[O]ne of ordinary skill in the art should readily recognize that the speed of the CPU and clock *do not* vary together due to manufacturing variation, operating voltage, and temperature of the IC in the Magar processor . . . This is simply because the Magar microprocessor clock is frequency controlled by a crystal which is also external to the microprocessor. Crystals are by design fixed frequency devices whose oscillation speed is designed to be tightly controlled and to vary minimally due to variations in manufacturing, operating voltage and temperature. The Magar microprocessor in no way contemplates a variable speed clock as claimed.<sup>10</sup>

In the same amendment, the applicants also argued that the Magar clock could not practice the

claimed invention because of its reliance on a crystal, which by its nature cannot vary its oscillation

frequency:

[C]rystal oscillators have never, to Applicants' knowledge, been fabricated on a single silicon substrate with a CPU, for instance. Even if they were, as previously mentioned, crystals are by design fixed-frequency devices whose oscillation

- 25 <sup>8</sup> Docket No. 28-3, Ex. C at 16:44-48.

- 26 <sup>9</sup> See Docket No. 28-3, Ex. C at 17:14-34, Fig. 17.

- 27 <sup>10</sup> Docket No. 90-7, Ex. D at 3-4.

4 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

28

| Ш  | Case: 16-1306 Document: 84 Page: 15 Filed: 07/05/2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Case3:12-cv-03865-VC Document98 Filed09/22/15 Page5 of 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|    | frequency is designed to be tightly controlled and to vary minimally due to variations in manufacturing, operating voltage and temperature. The oscillation                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | frequency of a crystal on the same substrate with the microprocessor would                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | inherently not vary due to variations in manufacturing, operating voltage and temperature in the same way as the frequency capability of the microprocessor on the same underlying substrate, as claimed. <sup>11</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|    | The PTO nonetheless issued a second rejection based on Magar, and the applicants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| re | esponded by emphasizing again that the claimed invention did not rely on an external crystal's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| fi | xed frequency to set the clock's frequency rate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|    | The essential difference is that the frequency or rate of the signals is determined<br>by the processing and/or operating parameters of the integrated circuit containing the<br>circuit, while the frequency or rate of the signals depicted in Magar are<br>determined by the fixed frequency of the external crystal. <sup>12</sup>                                                                                                                                                                                                                                                       |

|    | The applicants also disclaimed the use of an external crystal to cause clock signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0  | scillation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | Magar's clock generator relies on an external crystal connected to terminals X1 and X2 to oscillate It is not an entire oscillator in itself. And with the crystal, the                                                                                                                                                                                                                                                                                                                                                                                                                      |

|    | clock rate generated is also conventional in that it is a fixed, not a variable, frequency. The Magar clock is comparable in operation to the conventional crystal clock 434 depicted in Fig. 17 of the present application for controlling the I/O interface at a fixed rate frequency, and not at all like the clock on which the claims are based. <sup>13</sup>                                                                                                                                                                                                                          |

|    | The examiner similarly issued an initial rejection in view of Sheets. In response, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| a  | pplicants distinguished their "present invention" from microprocessors that rely on frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| с  | ontrol information from an external source:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|    | The present invention does not similarly rely upon provision of frequency control information to an external clock, but instead contemplates providing a ring oscillator clock and the microprocessor within the same integrated circuit. The placement of these elements within the same integrated circuit obviates the need for provision of the type of frequency control information described by Sheets, since the microprocessor and clock will naturally tend to vary commensurately in speed as a function of various parameters (e.g., temperature) affecting circuit performance. |

| 11 | <i>Id.</i> at 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12 | <sup>2</sup> <i>Id.</i> at 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13 | <sup>3</sup> <i>Id.</i> at 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| c  | 5<br>Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-<br>v-03881-VC<br>CLAIM CONSTRUCTION REPORT AND RECOMMENDATION                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | Appx10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

United States District Court For the Northern District of California

| I        | Case: 16-1306 Document: 84 Page: 16 Filed: 07/05/2016                                                                                                                                    |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | Case3:12-cv-03865-VC Document98 Filed09/22/15 Page6 of 12                                                                                                                                |  |  |

| 1        | Sheets' system for providing clock control signals to an external clock is thus seen to be unrelated to the integral microprocessor/clock system of the present invention. <sup>14</sup> |  |  |

| 2        | Because the applicants referred to the "present invention" in this statement, their disclaimer applies                                                                                   |  |  |

| 3        | to all claims. <sup>15</sup>                                                                                                                                                             |  |  |

| 4        | But that disclaimer, like the prior disclaimers, could not secure allowance. In response to                                                                                              |  |  |

| 5        | a subsequent rejection, the applicants went even further and disclaimed the use of controlled                                                                                            |  |  |

| 6        | inputs altogether, regardless whether the control is on-chip or not:                                                                                                                     |  |  |

| 7        | Even if the examiner is correct that the variable clock in Sheets is in the same                                                                                                         |  |  |

| 8        | circuit as the microprocessor of system 100, that still does not give the claimed subject matter. In Sheets, a command input is required to change the clock speed. In                   |  |  |

| 9        | the present invention, the clock speed varies correspondingly to variations in                                                                                                           |  |  |

| 10       | operating parameters No command input is necessary to change the clock frequency. <sup>16</sup>                                                                                          |  |  |

| 11       | Thus, according to applicants, controlling the on-chip oscillator's speed using a command signal                                                                                         |  |  |

| 12       | "does not give the claimed subject matter." <sup>17</sup> Indeed, in a later amendment, the applicants left no                                                                           |  |  |

| 13       | doubt that, unlike "all cited references," the claimed oscillator is completely free of inputs and                                                                                       |  |  |

| 14       | extra components:                                                                                                                                                                        |  |  |

| 15       | Crucial to the present invention is that when fabrication and environmental                                                                                                              |  |  |

| 16       | parameters vary, the oscillation or clock frequency and the frequency capability of<br>the driven device will automatically vary together. This differs from all cited                   |  |  |

| 17       | references in that the oscillator or variable speed clock varies in frequency but does not require manual or programmed inputs or external or extra components to                        |  |  |

| 18       | do so. <sup>18</sup>                                                                                                                                                                     |  |  |

| 19<br>20 | After overcoming these and other objections by the examiner, the '336 patent issued on                                                                                                   |  |  |

| 20       | September 15, 1998. The patent has been construed in three previous litigations, including                                                                                               |  |  |

| 21<br>22 |                                                                                                                                                                                          |  |  |

| 22       | <sup>14</sup> Docket No. 90-9, Ex. F at 8.                                                                                                                                               |  |  |

| 23<br>24 | <sup>15</sup> See, e.g., Ballard Med. Prods. v. Allegiance Healthcare Corp., 268 F.3d 1352, 1360-62 (Fed. Cir. 2001).                                                                    |  |  |

| 25       | <sup>16</sup> Docket No. 90-10, Ex. G at 4.                                                                                                                                              |  |  |

| 26       | <sup>17</sup> <i>Id.</i>                                                                                                                                                                 |  |  |

| 27       | <sup>18</sup> Docket No. 90-7, Ex. D at 5.                                                                                                                                               |  |  |

| 28       | 6<br>Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-<br>cv-03881-VC<br>CLAIM CONSTRUCTION REPORT AND RECOMMENDATION                              |  |  |

|          |                                                                                                                                                                                          |  |  |

# United States District Court For the Northern District of California

## Case: 16-1306 Document: 84 Page: 17 Filed: 07/05/2016

Case3:12-cv-03865-VC Document98 Filed09/22/15 Page7 of 12

one before the undersigned that resulted in a nine-day trial. In the Eastern District of Texas, Judge Ward construed the "entire ring oscillator" claim term in claim 1 to preclude reliance on either a control signal or an external crystal/clock generator to generate a clock signal.<sup>19</sup> In reaching this conclusion, Judge Ward explained: "The Court agrees with the defendants that the applicant disclaimed the use of an input control signal and an external crystal/clock generator to generate a clock signal."<sup>20</sup>

Similarly, in a United States International Trade Commission investigation, Judge Gildea construed "entire oscillator" as precluding reliance on either a control signal or an external crystal/clock generator to generate a clock signal.<sup>21</sup> Judge Gildea found that Plaintiffs clearly and unambiguously disclaimed any oscillator that relies on a control signal or an external crystal or frequency generator.<sup>22</sup> The Commission affirmed Judge Gildea's construction.<sup>23</sup>

Likewise, this court construed "ring oscillator" as "an oscillator having a multiple, odd number of inversions arranged in a loop, wherein the oscillator is variable based on the temperature, voltage and process parameters in the environment,"<sup>24</sup> and instructed the jury that the term "entire oscillator" excludes any external clock used to generate the CPU clock signal.<sup>25</sup>

- 24  $\left\| {}^{23} See \text{ Docket No. 90-17, Ex. N at 16-25.} \right\|$

- 25 24 See Acer, Inc. v. Tech. Properties Ltd., No. 5:08-CV-00877 PSG, 2013 WL 4515545, at \*5 (N.D. Cal. Aug. 21, 2013).

<sup>26</sup>

<sup>25</sup> See Docket No. 90-13, Ex. J at 26; Docket No. 90-14, Ex. K at 2; see also Docket No. 90-18, Ex. O at 11, and n.24.

7 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

<sup>&</sup>lt;sup>19</sup> See Docket No. 90-15, Ex. L at 12.

$<sup>^{20}</sup>$  *Id.*

<sup>&</sup>lt;sup>21</sup> See Docket No. 90-16, Ex. M at 40-41; Docket No. 90-17, Ex. N at 16-25.

<sup>21

22</sup> See Docket No. 90-20, Ex. Q at 39-40 (finding that "the essential point made by the applicants in seeking to gain acceptance" of their claims, and their "unqualified statements in distinguishing" the prior art, constituted a "clear disavowal" of claim scope).

#### Case: 16-1306 Document: 84 Page: 18 Filed: 07/05/2016

Case3:12-cv-03865-VC Document98 Filed09/22/15 Page8 of 12

The parties to this litigation agree that the disputed term must be limited as "an [oscillator] that is located entirely on the same semiconductor substrate as the [central processing unit]."<sup>26</sup> Where they disagree is whether the term should further be limited to read as "an [oscillator] that is located entirely on the same semiconductor substrate as the [central processing unit] and does not rely on a control signal or an external crystal/clock generator to cause clock signal oscillation or control clock signal frequency."<sup>27</sup>

#### II.

This court has jurisdiction under 28 U.S.C. §§ 1331 and 1338. The presiding judge referred all pretrial matters to the undersigned pursuant to Fed. R. Civ. P. 72(a).<sup>28</sup>

"To construe a claim term, the trial court must determine the meaning of any disputed words from the perspective of one of ordinary skill in the pertinent art at the time of filing."<sup>29</sup> This requires a careful review of the intrinsic record comprised of the claim terms, written description and prosecution history of the patent.<sup>30</sup>

While claim terms "are generally given their ordinary and customary meaning,"<sup>31</sup> the claims themselves and the context in which the terms appear "provide substantial guidance as to the meaning of particular claim terms."<sup>32</sup> Indeed, a patent's specification "is always highly relevant

<sup>27</sup> Id.

<sup>28</sup> See Docket No. 17.

<sup>29</sup> Chamberlain Group, Inc. v. Lear Corp., 516 F.3d 1331, 1335 (Fed. Cir. 2008).

<sup>32</sup> *Phillips*, 415 F.3d at 1314

28

26

27

8 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

## Appx13

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

<sup>&</sup>lt;sup>26</sup> Docket No. 89 at 7.

<sup>&</sup>lt;sup>30</sup> See id. ("To construe a claim term, the trial court must determine the meaning of any disputed words from the perspective of one of ordinary skill in the pertinent art at the time of filing. Intrinsic evidence, that is the claims, written description, and the prosecution history of the patent, is a more reliable guide to the meaning of a claim term than are extrinsic sources like technical dictionaries, treatises, and expert testimony.") (citing *Phillips*, 415 F.3d at 1312).

<sup>&</sup>lt;sup>31</sup> *Phillips*, 415 F.3d at 1312 (quoting *Vitronics Corp. v. Conceptronic, Inc.*, 90 F.3d 1576, 1582 (Fed. Cir. 1996)).

## Case: 16-1306 Document: 84 Page: 19 Filed: 07/05/2016 Case3:12-cv-03865-VC Document98 Filed09/22/15 Page9 of 12

to the claim construction analysis.<sup>33</sup> Claims "must be read in view of the specification, of which they are part.<sup>34</sup>

Although the patent's prosecution history "lacks the clarity of the specification and thus is less useful for claim construction purposes," it "can often inform the meaning of the claim language by demonstrating how the inventor understood the invention and whether the inventor limited the invention in the course of prosecution, making the claim scope narrower than it would otherwise be."<sup>35</sup> The court also has the discretion to consider extrinsic evidence, including dictionaries, learned treatises and testimony from experts and inventors.<sup>36</sup> Such evidence, however, is "less significant than the intrinsic record in determining the legally operative meaning of claim language."<sup>37</sup> No extrinsic evidence is necessary to resolve the dispute here, however, because the intrinsic record is dispositive that the applicant disclaimed certain claim scope to convince the examiner to issue the patent.

#### III.

"[T]here is no principle of patent law that the scope of surrender of subject matter made during prosecution is limited to what is absolutely necessary to avoid a prior art reference that was the basis for an examiner's rejection."<sup>38</sup> Whether necessary or not to get the examiner to avoid Magar and Sheets, the applicant here surrendered subject matter that the definition of the "entire oscillator" term must account, albeit in language different than that proposed by either side.

<sup>34</sup> Markman v. Westview Instruments, Inc., 52 F.3d 967, 979 (Fed. Cir. 1995); see also Ultimax Cement Mfg. Corp v. CTS Cement Mfg. Corp., 587 F. 3d 1339, 1347 (Fed. Cir. 2009).

<sup>35</sup> *Phillips*, 415 F.3d at 1317 (internal quotations omitted).

<sup>36</sup> See id. ("Although we have emphasized the importance of intrinsic evidence in claim construction, we have also authorized district courts to rely on extrinsic evidence, which 'consists of all evidence external to the patent and prosecution history, including expert and inventor testimony, dictionaries, and learned treatises."") (quoting *Markman*, 52 F.3d at 980).

<sup>37</sup> *Phillips*, 415 F.3d at 1317 (citing *C.R. Bard, Inc. v. U.S. Surgical Corp.*, 388 F.3d 858, 862 (Fed. Cir. 2004)) (internal quotations and additional citations omitted).

<sup>38</sup> Norian Corp. v. Stryker Corp., 432 F.3d 1356, 1361 (Fed. Cir. 2005).

9 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

<sup>&</sup>lt;sup>33</sup> *Phillips*, 415 F.3d at 1312-15.

#### Case: 16-1306 Document: 84 Page: 20 Filed: 07/05/2016

Case3:12-cv-03865-VC Document98 Filed09/22/15 Page10 of 12

1 To avoid Magar, the applicants surrendered any oscillator that like Magar's is fixed by an 2 off-chip crystal. Over and over again, the applicants insisted that its claims did not read on Magar because of this distinction. Whether styled by the applicants as an "essential difference" or "not at 3 all like the clock on which the claims are based,"<sup>39</sup> Magar is distinct from the invention because it 4 5 fixes the frequency of the CPU with a crystal oscillator that is not on the same silicon substrate. Having sold the Patent Office on this distinction, and told the world the same in the prosecution 6 history, the applicants understood that they could not later claim anything else. The Federal Circuit 7 has taught this lesson over and over again.<sup>40</sup> 8 9 <sup>39</sup> Docket No. 90-8, Ex. E at 3, 4. 10 <sup>40</sup> See, e.g., Southwall, 54 F.3d at 1576 ("Claims may not be construed one way in order to obtain their allowance and in a different way against accused infringers."); Rheox, 276 F.3d at 1325 11 ("Explicit arguments made during prosecution to overcome prior art can lead to a narrow claim 12 interpretation because '[t]he public has a right to rely on such definitive statements made during prosecution.""); Gillespie v. Dywidag Sys. Int'l, USA, 501 F.3d 1285, 1291 (Fed. Cir. 2007) ("The 13 patentee is held to what he declares during the prosecution of his patent."); Computer Docking Station Corp. v. Dell, Inc., 519 F.3d 1366, 1379 (Fed. Cir. 2008) (holding that "the sum of the 14 patentees' statements during prosecution would lead a competitor to believe that the patentee had disavowed coverage of laptops" and, thus, affirming. the trial court's construction of the portable 15 computer limitation); Seachange Int'l, Inc. v. C-COR, Inc., 413 F.3d 1361, 1372-75 (Fed. Cir. 16 2005) ("Where an applicant argues that a claim possesses a feature that the prior art does not possess in order to overcome a prior art rejection, the argument may serve to narrow the scope of 17 otherwise broad claim language."); see also Am. Piledriving Equip. v. Geoquip, Inc., 637 F. 3d 1324, 1336 (Fed. Cir. 2011) ("[A]n applicant's argument that a prior art reference is 18 distinguishable on a particular ground can serve as a disclaimer of claim scope even if the applicant distinguishes the reference on other grounds as well."); Chimie v. PPG Indus., Inc., 402 F.3d 1371, 19 1384 (Fed. Cir. 2005) ("The purpose of consulting the prosecution history in construing a claim is 20 to 'exclude any interpretation that was disclaimed during prosecution.""; "Accordingly, 'where the patentee has unequivocally disavowed a certain meaning to obtain his patent, the doctrine of 21 prosecution disclaimer attaches and narrows the ordinary meaning of the claim congruent with the scope of the surrender."") (citations omitted); Microsoft Corp. v. Multi-Tech. Sys., Inc., 357 F.3d 22 1340, 1349 (Fed. Cir. 2004) (a court "cannot construe the claims to cover subject matter broader than that which the patentee itself regarded as comprising its invention and represented to the 23 PTO"); Springs Window Fashions LP v. Novo Indus., L.P., 323 F.3d 989, 993-96 (Fed. Cir. 2003) 24 (rejecting patentee's attempt to narrow the scope of disclaimer, even though the examiner did not rely on the disclaimer to issue the claims); N. Am. Container Inc. v. Plastipak Packaging Inc., 415 25 F.3d 1335, 1345-46 (Fed. Cir. 2005) (holding that "the applicant, through argument [that the priorart inner walls are 'slightly concave'] during the prosecution, disclaimed inner walls of the base 26 portion having any concavity.... [a]lthough the inner walls disclosed in the [prior art] may be viewed as entirely concave"). 27 28

10 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

## Case: 16-1306 Document: 84 Page: 21 Filed: 07/05/2016 Case3:12-cv-03865-VC Document98 Filed09/22/15 Page11 of 12

The song remains much the same regarding Sheets. The applicants distinguished Sheets repeatedly on the ground that Sheets requires control signals, frequency control information or command inputs. In contrast, they characterize the invention upon relying upon or requiring any such signals, information or inputs.<sup>41</sup> Because applicants described this distinction as no less than "crucial," and applicable to the "present invention," their disclaimer applies to all claims.<sup>42</sup>

Plaintiffs principally argue that the distinctions drawn from Magar and Sheets are already expressly included in the patent claims themselves. It is true that the "on-chip/off-chip" distinction and the invention's variability depending on PVT are reflected in other limitations. But those other limitations do not get at the full range of distinctions drawn, especially the claimed invention's oscillator frequency not being fixed by any crystal off-chip and the oscillator not needing any control inputs. The Federal Circuit has been clear that claim construction must reflect all disclaimers, not merely a subset.<sup>43</sup>

The undersigned appreciates that the construction recommended differs from the constructions adopted in the Eastern District of Texas, the International Trade Commission and by the undersigned as presiding judge in *HTC*. It also must be noted that neither party urged this particular language. But putting aside any notion that this court is bound in this case by any prior construction, the recommended construction is consistent with the fundamental meaning of those earlier constructions. After multiple rounds of briefing by the parties and a lengthy hearing, the undersigned is convinced that the particular language urged recommended here best captures what actually happened at the patent office. In the universe of claim construction, that directive is ultimate prime.

22

28

<sup>43</sup> See Krippelz v. Ford Motor Co., 667 F.3d 1261, 1267 (Fed. Cir. 2012); Am. Piledriving Equip. v. Geoquip, Inc., 637 F.3d 1324, 1336 (Fed. Cir. 2011); Elkay v. Mgf. Co. v. Ebco Mfg. Co., 192 F.3d

973, 979 (Fed. Cir. 1999).

11 Case Nos. 3:12-cv-03865-VC, 3:12-cv-03876-VC, 3:12-cv-03877-VC, 3:12-cv-03880-VC, 3:12-cv-03881-VC CLAIM CONSTRUCTION REPORT AND RECOMMENDATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

<sup>23 &</sup>lt;sup>41</sup> See Docket No. 90-9, Ex. F at 8; see also Docket No. 90-10, Ex. G at 4.

<sup>&</sup>lt;sup>42</sup> See, e.g., Ballard Med. Prods. v. Allegiance Healthcare Corp., 268 F.3d 1352, 1360-62 (Fed. Cir. 2001).

| Page12 of 12                  |

|-------------------------------|

| EWAL                          |

| EWAL                          |

| EWAL                          |

| s Magistrate Judge            |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

|                               |

| V-VC, 3:12-cv-03880-VC, 3:12- |

|                               |

United States District Court For the Northern District of California

#### United States Patent [19]

#### Moore et al.

#### [54] HIGH PERFORMANCE MICROPROCESSOR HAVING VARIABLE SPEED SYSTEM CLOCK

- [75] Inventors: Charles H. Moore, Woodside; Russell H. Fish, III, Mt. View, both of Calif.

- [73] Assignee: **Patriot Scientific Corporation**, San Diego, Calif.

- [21] Appl. No.: 484,918

- [22] Filed: Jun. 7, 1995

#### **Related U.S. Application Data**

[62] Division of Ser. No. 389,334, Aug. 3, 1989, Pat. No. 5,440,749.

| [51] | ] Int. Cl. <sup>6</sup> |  | G06F | 1/04 |

|------|-------------------------|--|------|------|

|------|-------------------------|--|------|------|

- [52]

U.S. Cl.

395/845

[58]

Field of Search

395/500, 551,

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,967,104 | 6/1976 | Brantingham   | 364/709.09 |

|-----------|--------|---------------|------------|

| 3,980,993 | 9/1976 | Bredart et al | 395/550    |

| 4,003,028 | 1/1977 | Bennett et al | 395/742    |

| 4,042,972 | 8/1977 | Gruner et al  | 395/389    |

| 4,050,096 | 9/1977 | Bennett       | 395/494    |

| 4,112,490 | 9/1978 | Pohlman et al | 395/287    |

| 4,315,308 | 2/1982 | Jackson       | 395/853    |

US005809336A

#### [11] **Patent Number: 5,809,336**

#### [45] **Date of Patent:** Sep. 15, 1998

| 4.338.675 | 7/1982  | Palmer                |

|-----------|---------|-----------------------|

| 4,398,265 |         | Puhl et al 395/882    |

| 4,453,229 |         | Schaire               |

| 4,503,500 | 3/1985  | Magan 395/800         |

| 4,539,655 |         | Trussell et al        |

| 4,553,201 | 11/1985 | Pollack 395/183.22    |

| 4,627,082 | 12/1986 | Pelgrom et al 377/63  |

| 4,670,837 | 6/1987  | Sheets                |

| 4,680,698 | 7/1987  | Edwards et al 395/800 |

| 4,761,763 | 8/1988  | Hicks 395/286         |

| 5,414,862 | 5/1995  | Suzuki et al 395/750  |

Primary Examiner-David Y. Eng

Attorney, Agent, or Firm-Cooley Godward LLP

#### [57] ABSTRACT

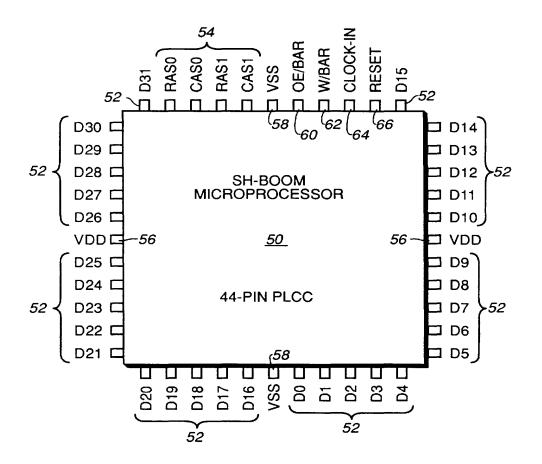

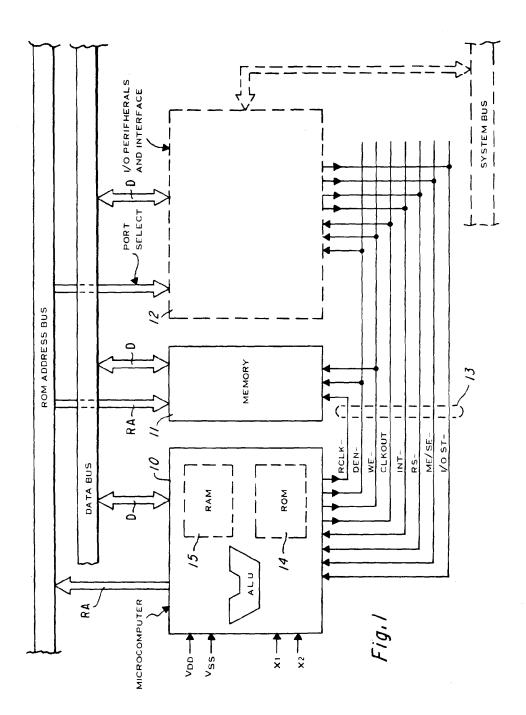

A high performance, low cost microprocessor system having a variable speed system clock is disclosed herein. The microprocessor system includes an integrated circuit having a central processing unit and a ring oscillator variable speed system clock for clocking the microprocessor. The central processing unit and ring oscillator variable speed system clock each include a plurality of electronic devices of like type, which allows the central processing unit to operate at a variable processing frequency dependent upon a variable speed of the ring oscillator variable speed system clock. The microprocessor system may also include an input/output interface connected to exchange coupling control signals, address and data with the central processing unit. The input/output interface is independently clocked by a second clock connected thereto.

#### 10 Claims, 19 Drawing Sheets

U.S. Patent

Sep. 15, 1998

Sheet 1 of 19

FIG.\_1

```

U.S. Patent

```

Sep. 15, 1998

Sheet 2 of 19

FIG.\_2

U.S. Patent

Sep. 15, 1998

Sheet 3 of 19

5,809,336

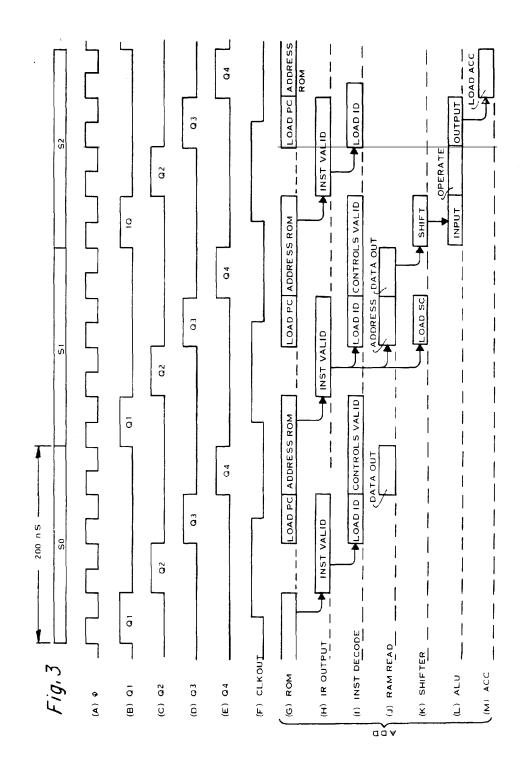

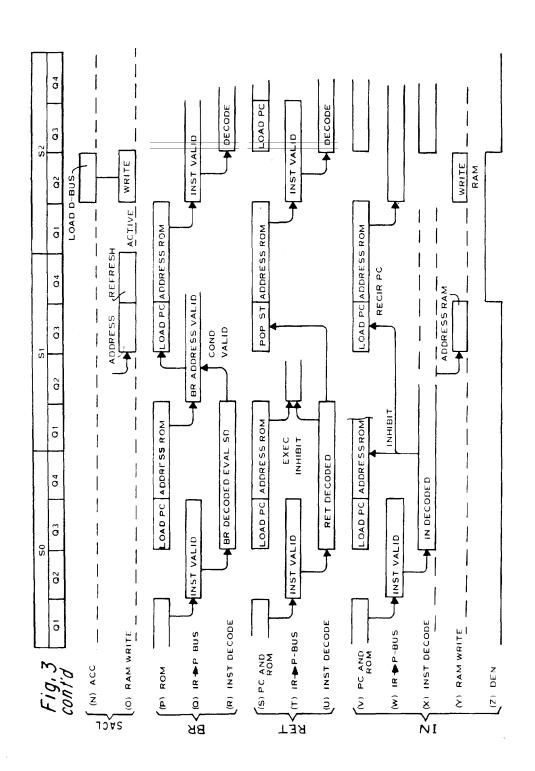

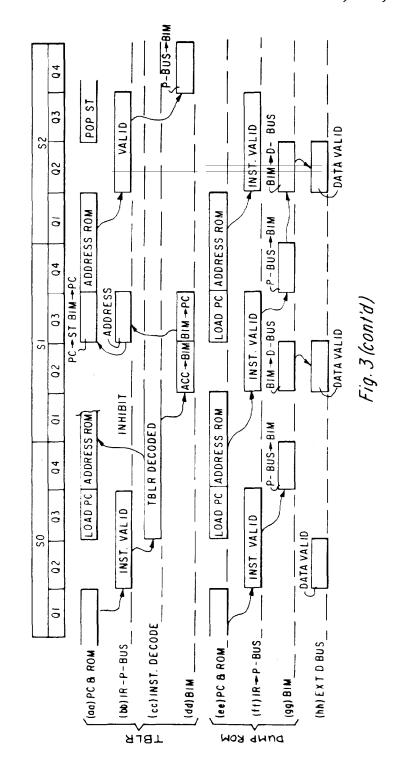

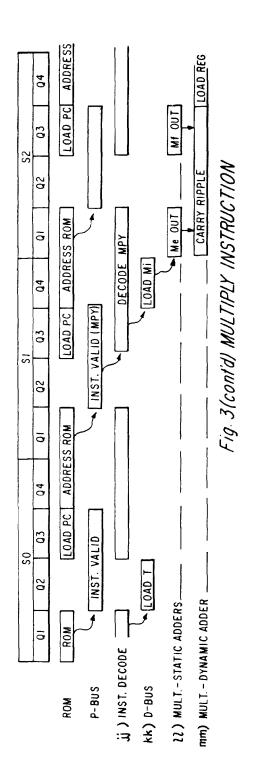

FIG.\_3

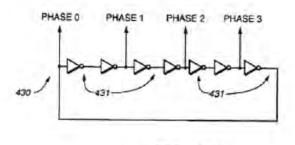

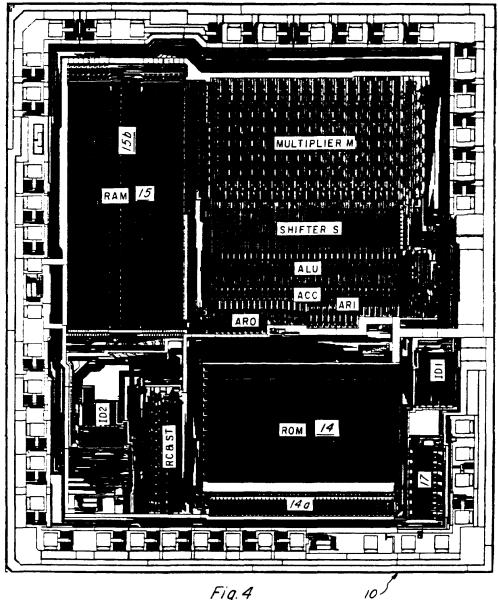

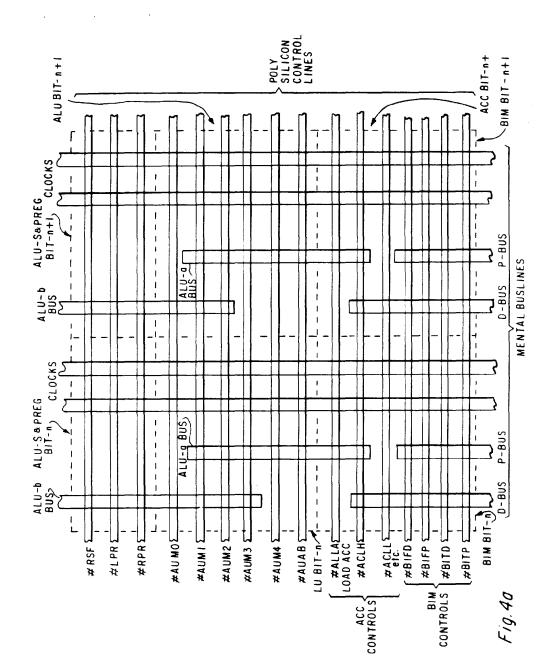

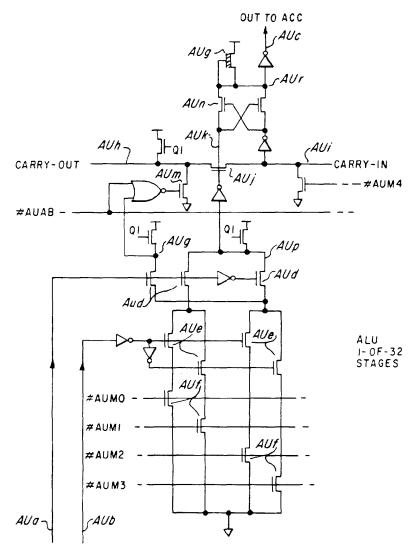

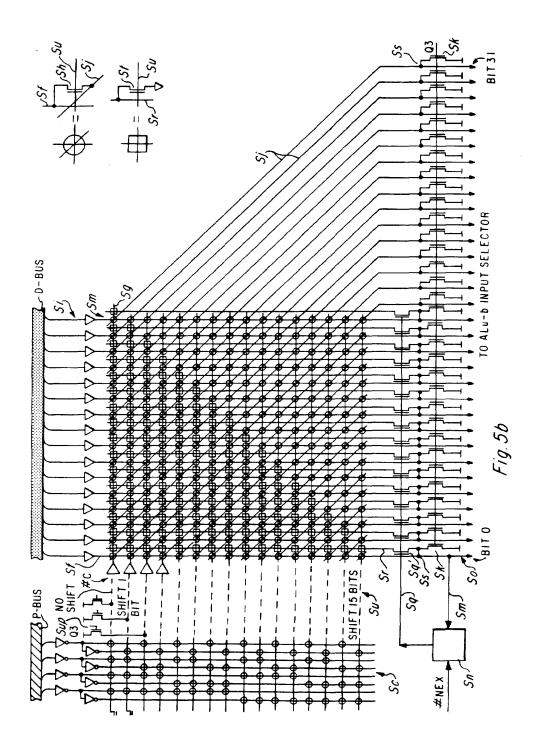

FIG.\_4

## FIG.\_5

Sep. 15, 1998

Sheet 6 of 19

5,809,336

FIG.\_6

Sheet 7 of 19

FIG.\_7

Appx25

Sep. 15, 1998

Sheet 8 of 19

FIG.\_8

FIG.\_9

5,809,336

#### Case: 16-1306 Document: 84 Page: 34 Filed: 07/05/2016

Sep. 15, 1998

Sheet 12 of 19

5,809,336

#### **REGISTER ARRAY**

COMPUTATION STACK

FIG.\_13

U.S. Patent

Sep. 15, 1998

Sheet 14 of 19

5,809,336

FIG.\_15

Appx32

CONTROL SIGNALS

FIG.\_16

FIG.\_18

U.S. Patent

FIG.\_17

FIG.\_19

Appx34

U.S. Patent

Sep. 15, 1998

Sheet 17 of 19

5,809,336

FIG.\_20

```

U.S. Patent

```

Sep. 15, 1998

FIG.\_21

Sheet 19 of 19

5

15

### 5,809,336

## 1

#### HIGH PERFORMANCE MICROPROCESSOR HAVING VARIABLE SPEED SYSTEM CLOCK

#### CROSS REFERENCE TO RELATED APPLICATIONS

This application is a division of U.S. application Ser. No. 07/389,334, filed Aug. 3, 1989, now U.S. Pat. No. 5,440, 749.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

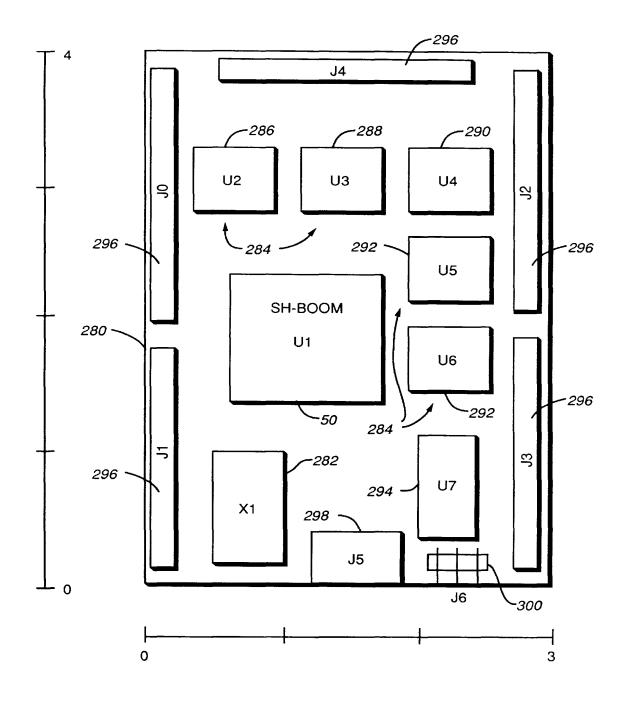

The present invention relates generally to a simplified, reduced instruction set computer (RISC) microprocessor. More particularly, it relates to such a microprocessor which is capable of performance levels of, for example, 20 million instructions per second (MIPS) at a price of, for example, 20 dollars.

2. Description of the Prior Art

Since the invention of the microprocessor, improvements in its design have taken two different approaches. In the first approach, a brute force gain in performance has been achieved through the provision of greater numbers of faster transistors in the microprocessor integrated circuit and an instruction set of increased complexity. This approach is exemplified by the Motorola 68000 and Intel 80X86 microprocessor families. The trend in this approach is to larger die sizes and packages, with hundreds of pinouts. 30

More recently, it has been perceived that performance gains can be achieved through comparative simplicity, both in the microprocessor integrated circuit itself and in its instruction set. This second approach provides RISC microprocessors, and is exemplified by the Sun SPARC and 35 the Intel 8960 microprocessors. However, even with this approach as conventionally practiced, the packages for the microprocessor are large, in order to accommodate the large number of pinouts that continue to be employed. A need therefore remains for further simplification of high perfor- 40 mance microprocessors.

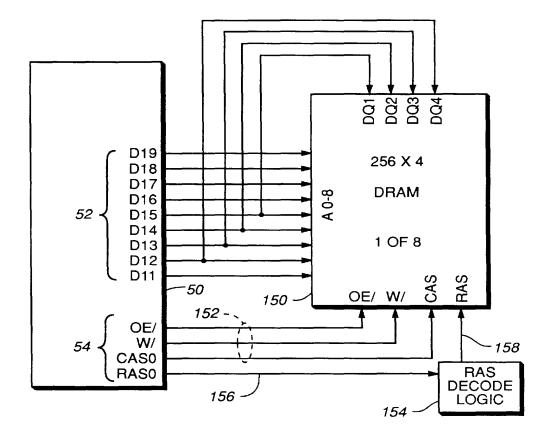

With conventional high performance microprocessors, fast static memories are required for direct connection to the microprocessors in order to allow memory accesses that are fast enough to keep up with the microprocessors. Slower 45 dynamic random access memories (DRAMs) are used with such microprocessors only in a hierarchical memory arrangement, with the static memories acting as a buffer between the microprocessors and the DRAMs. The necessity to use static memories increases cost of the resulting 50 systems.

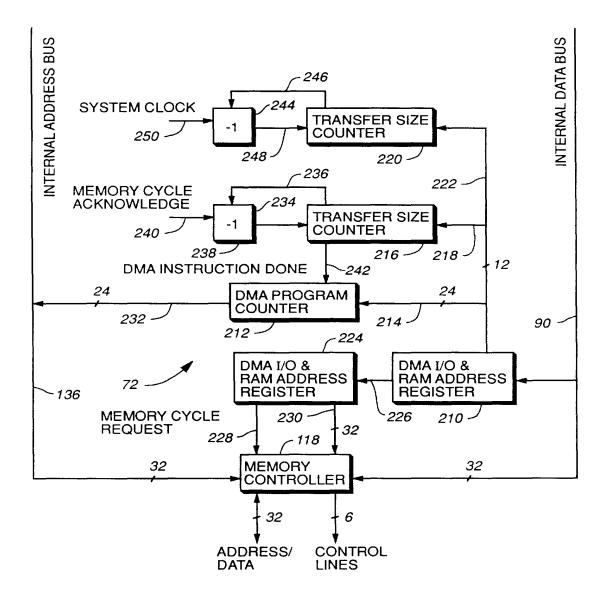

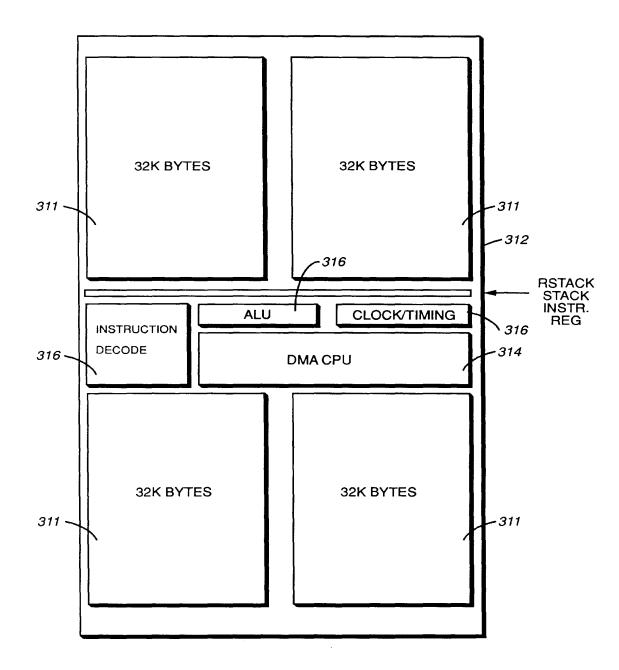

Conventional microprocessors provide direct memory accesses (DMA) for system peripheral units through DMA controllers, which may be located on the microprocessor 55 integrated circuit, or provided separately. Such DMA controllers can provide routine handling of DMA requests and responses, but some processing by the main central processing unit (CPU) of the microprocessor is required.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of this invention to provide a microprocessor with a reduced pin count and cost compared to conventional microprocessors.

It is another object of the invention to provide a high 65 performance microprocessor that can be directly connected to DRAMs without sacrificing microprocessor speed.

2

It is a further object of the invention to provide a high performance microprocessor in which DMA does not require use of the main CPU during DMA requests and responses and which provides very rapid DMA response with predictable response times.

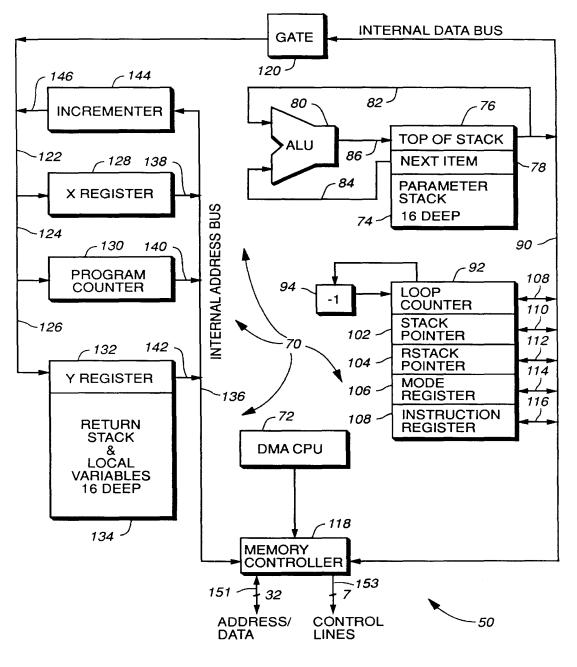

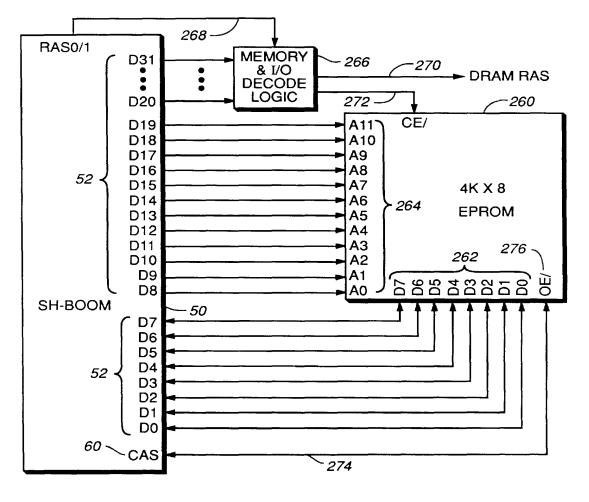

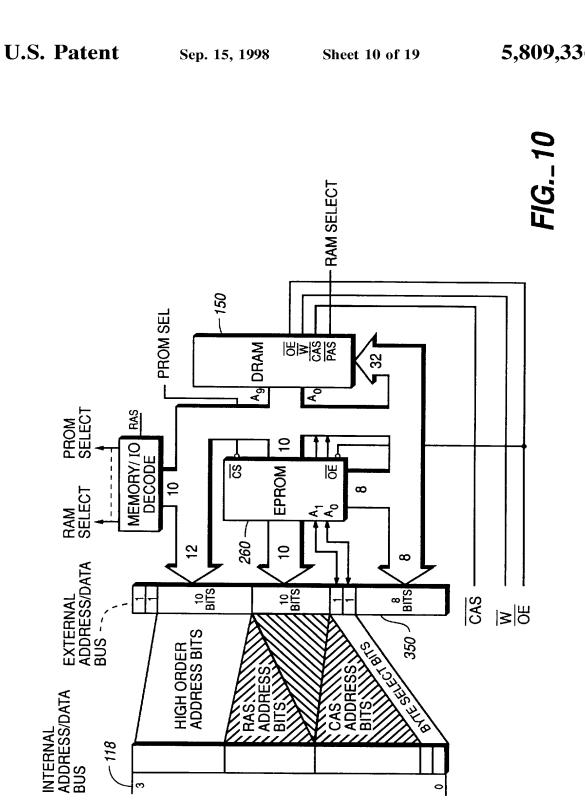

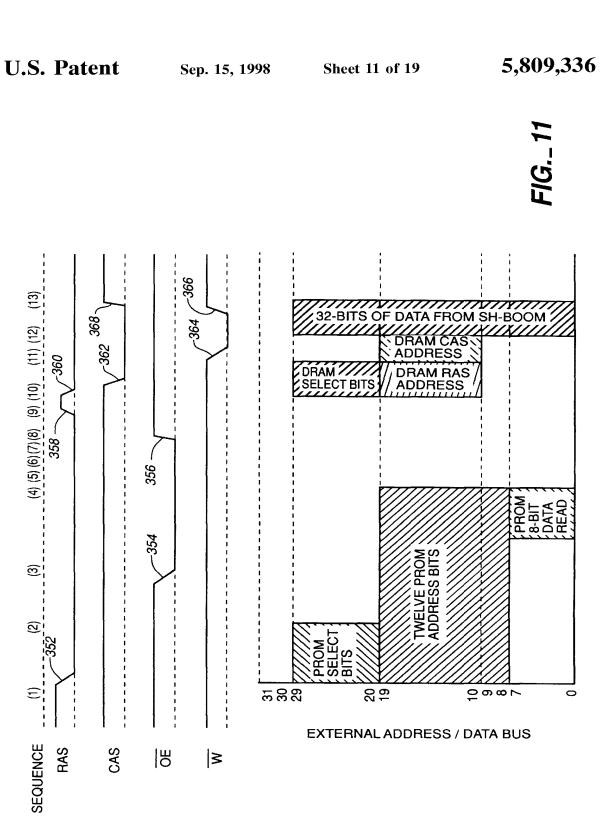

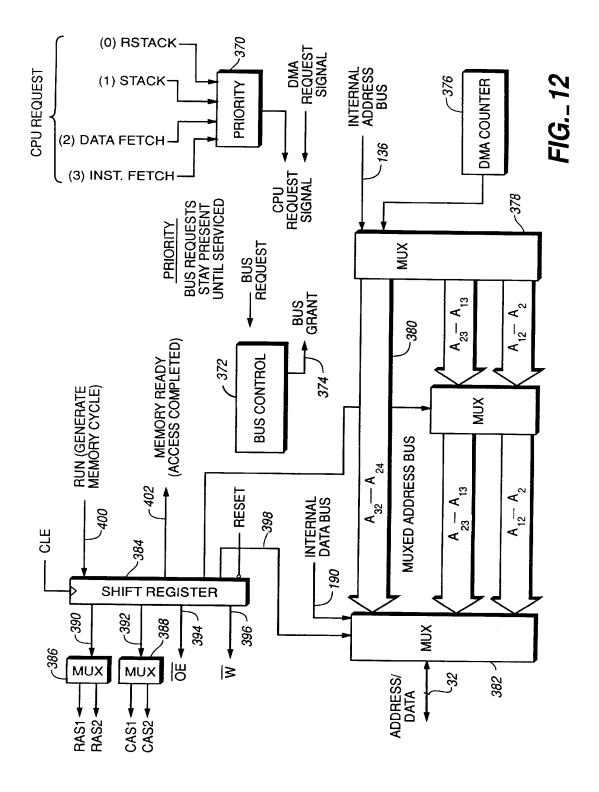

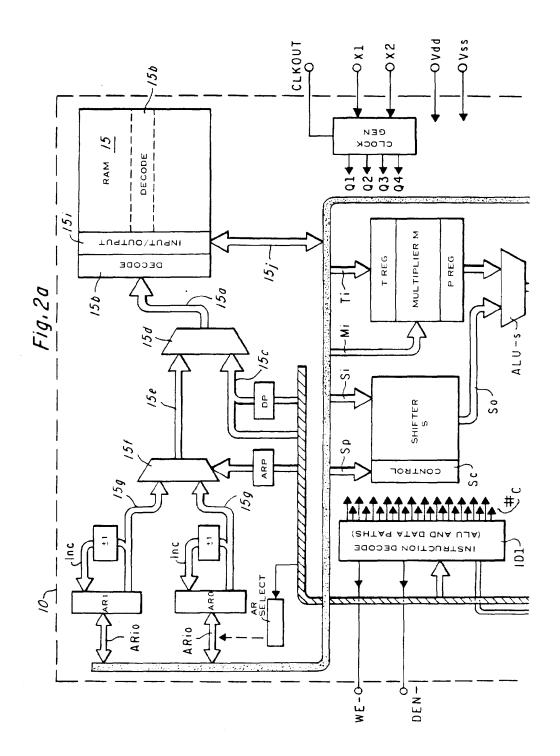

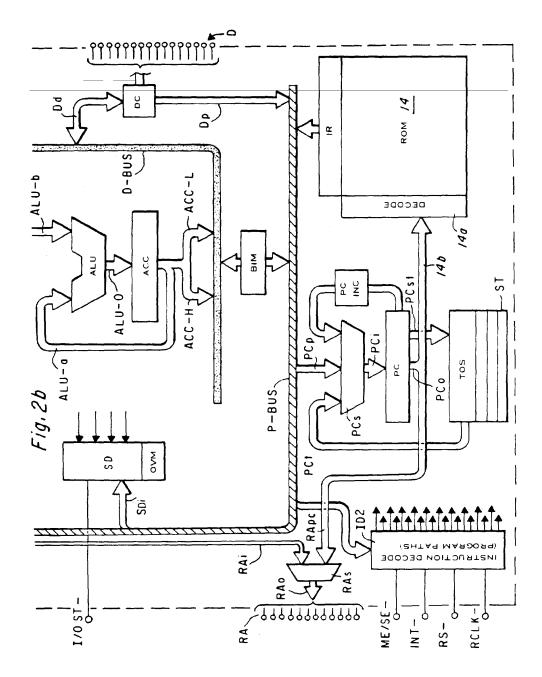

The attainment of these and related objects may be achieved through use of the novel high performance, low cost microprocessor herein disclosed. In accordance with one aspect of the invention, a microprocessor system in 10 accordance with this invention has a central processing unit, a dynamic random access memory and a bus connecting the central processing unit to the dynamic random access memory. There is a multiplexing means on the bus between the central processing unit and the dynamic random access memory. The multiplexing means is connected and configured to provide row addresses, column addresses and data on the bus.

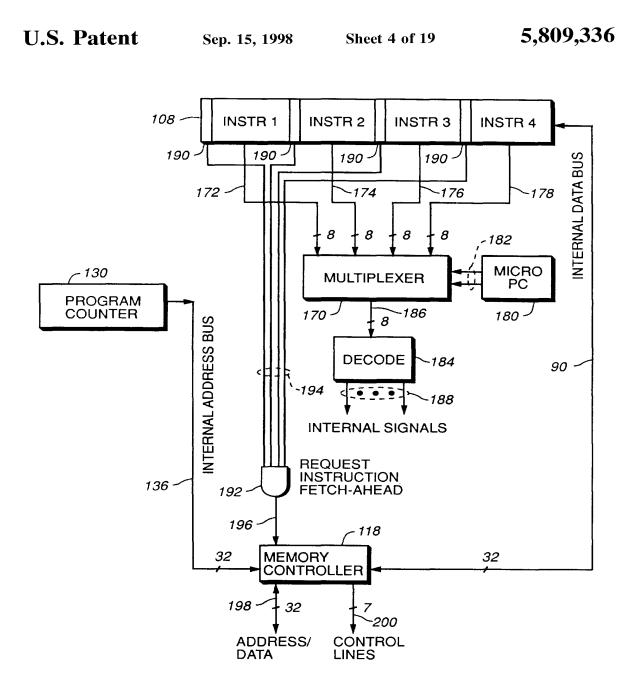

In accordance with another aspect of the invention, the microprocessor system has a means connected to the bus for 20 fetching instructions for the central processing unit on the bus. The means for fetching instructions is configured to fetch multiple sequential instructions in a single memory cycle. In a variation of this aspect of the invention, a programmable read only memory containing instructions for the central processing unit is connected to the bus. The means for fetching instructions includes means for assembling a plurality of instructions from the programmable read only memory and storing the plurality of instructions in the dynamic random access memory.

In another aspect of the invention, the microprocessor system includes a central processing unit, a direct memory access processing unit and a memory connected by a bus. The direct memory access processing unit includes means for fetching instructions for the central processing unit and for fetching instructions for the direct memory access processing unit on the bus.

In a further aspect of the invention, the microprocessor system, including the memory, is contained in an integrated circuit. The memory is a dynamic random access memory, and the means for fetching multiple instructions includes a column latch for receiving the multiple instructions.

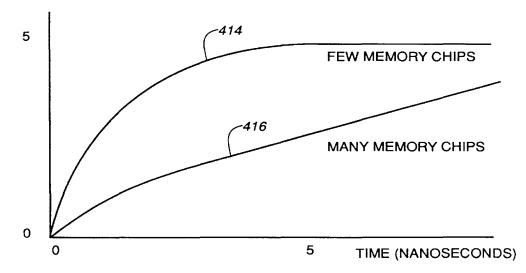

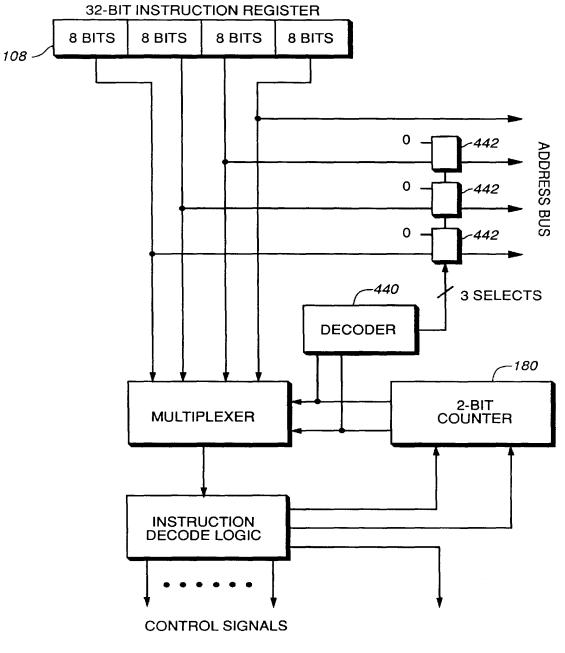

In still another aspect of the invention, the microprocessor system additionally includes an instruction register for the multiple instructions connected to the means for fetching instructions. A means is connected to the instruction register for supplying the multiple instructions in succession from the instruction register. A counter is connected to control the means for supplying the multiple instructions to supply the multiple instructions in succession. A means for decoding the multiple instructions is connected to receive the multiple instructions in succession from the means for supplying the multiple instructions. The counter is connected to said means for decoding to receive incrementing and reset control signals from the means for decoding. The means for decoding is configured to supply the reset control signal to the counter and to supply a control signal to the means for fetching instructions in response to a SKIP instruction in the multiple instructions. In a modification of this aspect of the invention, the microprocessor system additionally has a loop counter connected to receive a decrement control signal from the means for decoding. The means for decoding is configured to supply the reset control signal to the counter and the decrement control signal to the loop counter in response to a MICROLOOP instruction in the multiple instructions. In a further modification to this aspect of the invention, the means for decoding is configured to control

25

the counter in response to an instruction utilizing a variable width operand. A means is connected to the counter to select the variable width operand in response to the counter.

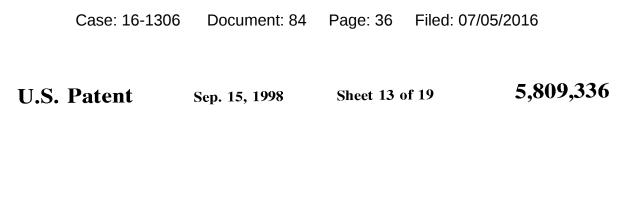

In a still further aspect of the invention, the microprocessor system includes an arithmetic logic unit. A first push 5 down stack is connected to the arithmetic logic unit. The first push down stack includes means for storing a top item connected to a first input of the arithmetic logic unit and means for storing a next item connected to a second input of the arithmetic logic unit. The arithmetic logic unit has an output connected to the means for storing a top item. The means for storing a top item is connected to provide an input to a register file. The register file desirably is a second push down stack, and the means for storing a top item and the register file are bidirectionally connected.

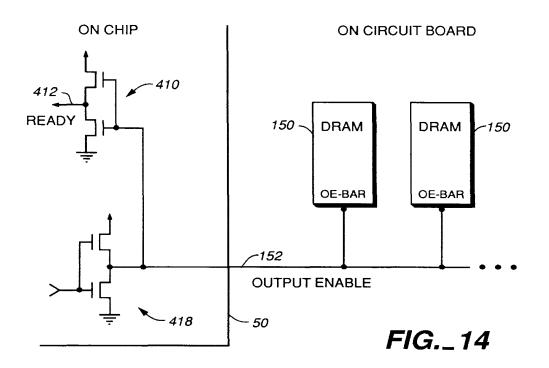

In another aspect of the invention, a data processing system has a microprocessor including a sensing circuit and a driver circuit, a memory, and an output enable line connected between the memory, the sensing circuit and the driver circuit. The sensing circuit is configured to provide a ready signal when the output enable line reaches a predetermined electrical level, such as a voltage. The microprocessor is configured so that the driver circuit provides an enabling signal on the output enable line responsive to the ready signal.

In a further aspect of the invention, the microprocessor system has a ring counter variable speed system clock connected to the central processing unit. The central processing unit and the ring counter variable speed system clock are provided in a single integrated circuit. An input/ output interface is connected to exchange coupling control signals, addresses and data with the input/output interface. A second clock independent of the ring counter variable speed system clock is connected to the input/output interface.

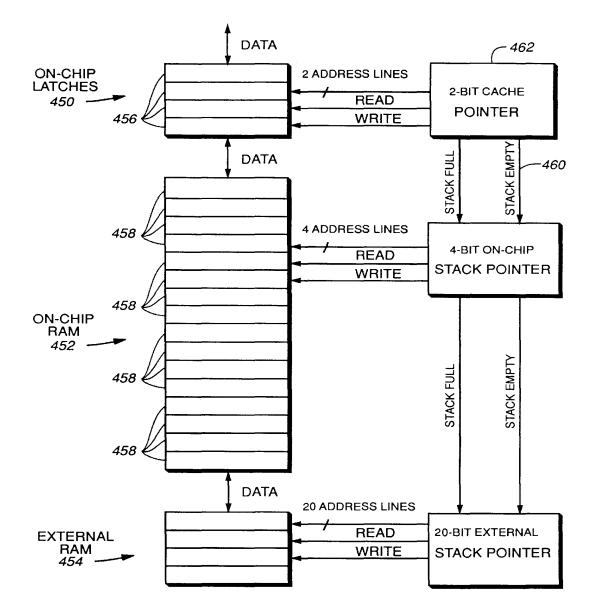

In yet another aspect of the invention, a push down stack is connected to the arithmetic logic unit. The push down stack includes means for storing a top item connected to a first input of the arithmetic logic unit and means for storing a next item connected to a second input of the arithmetic 40 logic unit. The arithmetic logic unit has an output connected to the means for storing a top item. The push down stack has a first plurality of stack elements configured as latches and a second plurality of stack elements configured as a random access memory. The first and second plurality of stack 45 dance with the invention. elements and the central processing unit are provided in a single integrated circuit. A third plurality of stack elements is configured as a random access memory external to the single integrated circuit. In this aspect of the invention, desirably a first pointer is connected to the first plurality of 50 stack elements, a second pointer connected to the second plurality of stack elements, and a third pointer is connected to the third plurality of stack elements. The central processing unit is connected to pop items from the first plurality of stack elements. The first stack pointer is connected to the 55 second stack pointer to pop a first plurality of items from the second plurality of stack elements when the first plurality of stack elements are empty from successive pop operations by the central processing unit. The second stack pointer is connected to the third stack pointer to pop a second plurality 60 of items from the third plurality of stack elements when the second plurality of stack elements are empty from successive pop operations by the central processing unit.

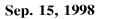

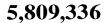

In another aspect of the invention, a first register is connected to supply a first input to the arithmetic logic unit. 65 A first shifter is connected between an output of the arithmetic logic unit and the first register. A second register is

connected to receive a starting polynomial value. An output of the second register is connected to a second shifter. A least significant bit of the second register is connected to The arithmetic logic unit. A third register is connected to supply feedback terms of a polynomial to the arithmetic logic unit. A down counter, for counting down a number corresponding to digits of a polynomial to be generated, is connected to the arithmetic logic unit. The arithmetic logic unit is responsive to a polynomial instruction to carry out an exclusive OR of the contents of the first register with the contents of the third register if the least significant bit of the second register is a "ONE" and to pass the contents of the first register unaltered if the least significant bit of the second register is a "ZERO", until the down counter completes a count. The polynomial to 15 be generated results in said first register.