|    | Case 3:12-cv-03880-VC Document 144 Fi                                                                                                                                                                          | led 06/16/17 Page 1 of 11                              |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| 1  | (Counsel listed on signature page)                                                                                                                                                                             |                                                        |  |

| 2  |                                                                                                                                                                                                                |                                                        |  |

| 3  | UNITED STATES DI<br>NORTHERN DISTRIC                                                                                                                                                                           |                                                        |  |

| 4  | NORTHERN DISTRIC                                                                                                                                                                                               | I OF CALIFORNIA                                        |  |

| 5  |                                                                                                                                                                                                                | Corr No. 2:12 02020 MC                                 |  |

| 6  | TECHNOLOGY PROPERTIES<br>LIMITED LLC, et al.,                                                                                                                                                                  | Case No. 3:12-cv-03880-VC                              |  |

| 7  | Plaintiffs,                                                                                                                                                                                                    | PLAINTIFFS' SECOND AMENDED<br>INFRINGEMENT CONTENTIONS |  |

| 8  | v.                                                                                                                                                                                                             |                                                        |  |

| 9  | LG ELECTRONICS, INC. and LG                                                                                                                                                                                    |                                                        |  |

| 10 | ELECTRONICS U.S.A., INC.,                                                                                                                                                                                      |                                                        |  |

| 11 | Defendants.                                                                                                                                                                                                    |                                                        |  |

| 12 |                                                                                                                                                                                                                |                                                        |  |

| 13 | I. INTRODUCTION                                                                                                                                                                                                |                                                        |  |

| 14 | Plaintiffs' second amended infringement contentions ("Supplemental Contentions") are a                                                                                                                         |                                                        |  |

| 15 | supplement to the ones supplied to LG Electronics, Inc. and LG Electronics U.S.A., Inc.,                                                                                                                       |                                                        |  |

| 16 | (collectively, "Defendants") on July 27, 2015 ("First Amended Contentions") and are being                                                                                                                      |                                                        |  |

| 17 | served pursuant to Defendants' requests for these contentions and the Court's recent order (see                                                                                                                |                                                        |  |

| 18 | Dkt. 142). These contentions set forth Plaintiffs' positions regarding the construction of the term                                                                                                            |                                                        |  |

| 19 | "("Dkt. 142). These contentions set forth Plaintiffs' positions regarding the construction of the term<br>"entire oscillator" as established in the Federal Circuit's recent opinion (see Federal Circuit Case |                                                        |  |

| 20 | No. 16-1306, Doc. 99-2 ("the Fed. Cir. Opinion").                                                                                                                                                              | eur s recent opinion (see rederar en eur case          |  |

| 21 |                                                                                                                                                                                                                | that the proper construction for the claim term        |  |

| 22 | "entire oscillator disposed upon said integrated cir                                                                                                                                                           |                                                        |  |

| 23 |                                                                                                                                                                                                                |                                                        |  |

| 24 | on the same semiconductor substrate as the central processing unit that [a] does not require a                                                                                                                 |                                                        |  |

| 25 | command input to change the clock frequency and [b] whose frequency is not fixed by any external crystal." Fed. Cir. Opinion at 16.                                                                            |                                                        |  |

| 26 |                                                                                                                                                                                                                | tion that Plaintiffs' First Amended Contentions        |  |

| 27 | "cannot be correct under the [District] Court's or                                                                                                                                                             |                                                        |  |

| 28 |                                                                                                                                                                                                                |                                                        |  |

|    | term "entire oscillator"] given the stipulated judgment of non-infringement." See Case No. 3:12-<br>PLAINTIFFS' SECOND AMENDED CASE NO. 3:12-cv-03880-VC<br>INFRINGEMENT CONTENTIONS                           |                                                        |  |

#### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 2 of 11

cv-03877-VC, Dkt. 123 at 4, (Defendants' Case Management Statement). Plaintiffs' First 1 Amended Contentions, served before the District Court's construction, are not incorrect. At 2 worst, they are not up-to-date as they do not address the disclaimers found by the District Court 3 or the Federal Circuit, since neither of those courts had ruled on the construction of the "entire 4 oscillator" term when the First Amended Contentions were served. In the First Amended 5 Contentions, Plaintiffs correctly identified the ring oscillators in Defendants' accused products as 6 corresponding to the "entire oscillator" claim element. Plaintiffs stand by this portion of the First 7 Amended Contentions as well as the rest of the First Amended Contentions. Nevertheless, 8 Plaintiffs' contentions were based on Judge Grewal's previous construction of "entire oscillator" 9 from a prior case and did not address the negative limitations later placed on the "entire 10 oscillator" element (*i.e.*, the Federal Circuit's disclaimers). These Supplemental Contentions, 11 therefore, add to the First Amended Contentions and are consistent with the theories of 12 infringement presented therein. 13

Accordingly, these Supplemental Contentions will address the two disclaimers found by 14 the Federal Circuit that are directed to claim elements 6.c and 13.b in the First Amended 15 Contentions. The construction that requires "an oscillator located entirely on the same 16 semiconductor substrate as the central processing unit" is addressed in the First Amended 17 Contentions. The First Amended Contentions set forth Plaintiffs' theories of infringement 18 against accused products that are identified in Column A of Exhibit A (the "Accused Products"). 19 These Supplemental Contentions are directed to the same Accused Products as the First 20 Amended Contentions. 21

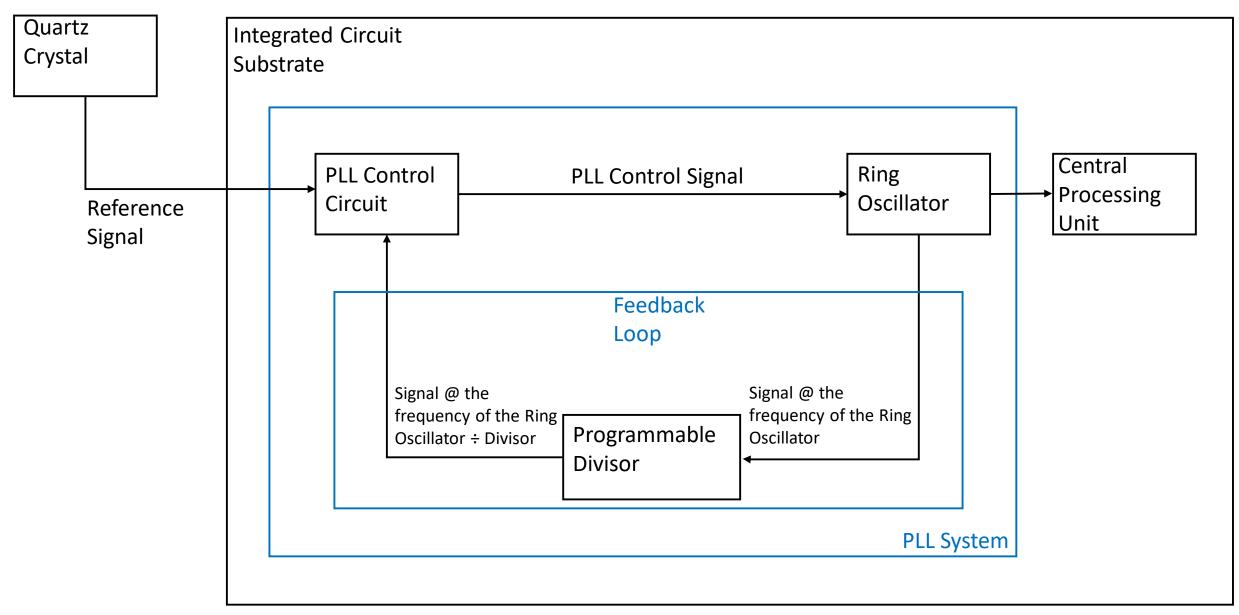

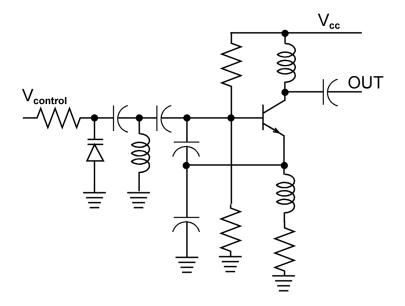

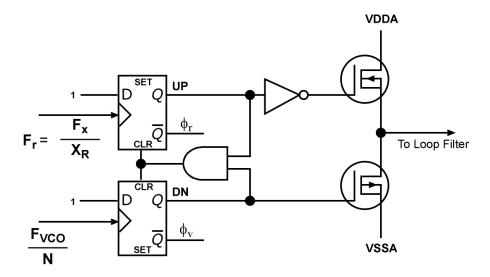

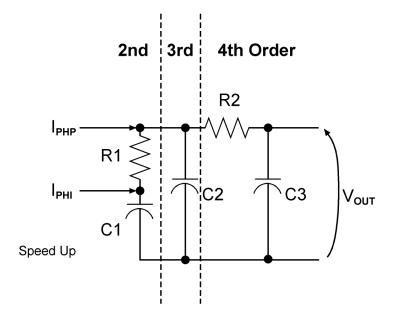

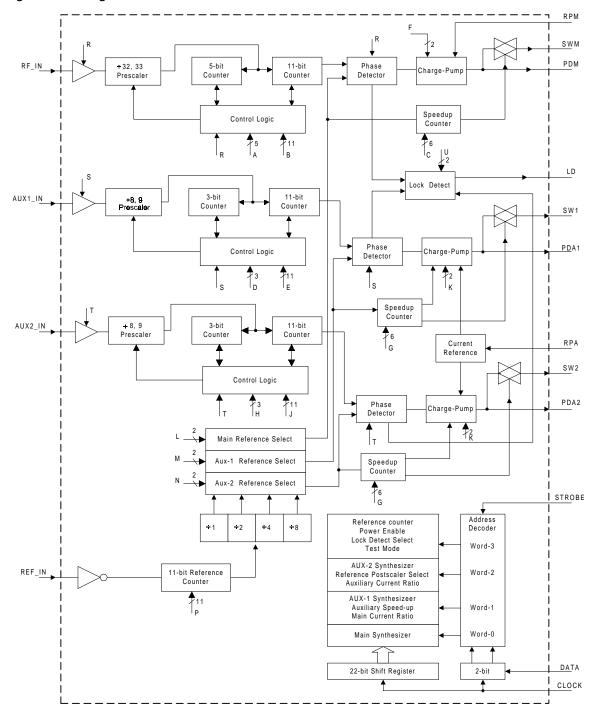

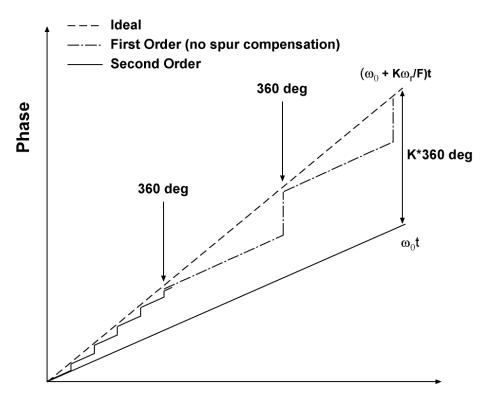

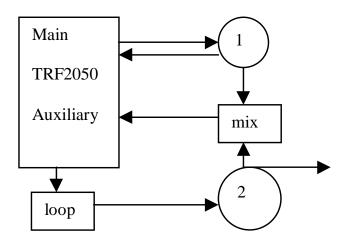

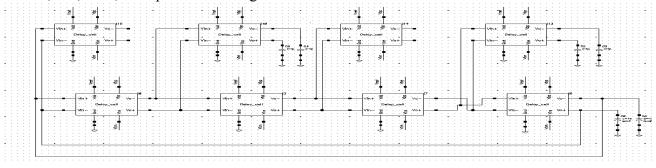

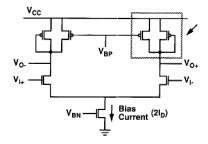

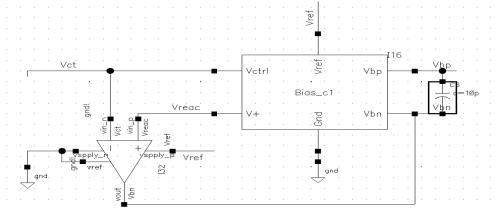

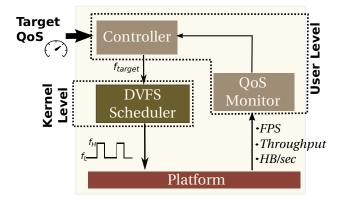

For reference and to avoid any misunderstandings arising from the inconsistent use of terminology in describing a PLL clocking system, a PLL system that is representative of the PLL systems found in each of the Accused Products is attached hereto as Exhibit B (referred to in its entirety as the "Representative Clocking System"), with certain features labeled. For the avoidance of doubt, Plaintiffs contend that each component and signal shown in the Representative Clocking System is present in each of the Accused Products. These labels will be used below in describing the Plaintiffs' positions. Specific implementations of PLLs used in

PLAINTIFFS' SECOND AMENDED INFRINGEMENT CONTENTIONS

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 3 of 11

various Accused Products are found in the Qualcomm, NVidia, IBM, and Texas Instruments document productions. *See, e.g.*, QTPL2PDS0063576, QTPL2PDS005450, QTPL2PDS0054987, QTPL2PDS0017582, QTPL2PDS007614, TI-0165418, and PDSND128219-22. Further, Plaintiffs' expert, Dr. Vojin Oklobdzija, explained the general operation of a particular PLL within a related product at trial. *See generally HTC Corp. v. Tech. Props. Ltd.*, Case No: C-08-00882-PSG, Trial Tr. vol. 3, 552:5-565:25, Sept. 25, 2013.

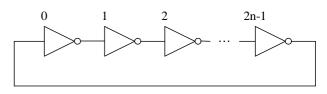

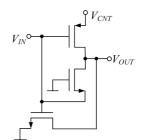

Ring Oscillator frequencies depend entirely on PVT (processing, voltage, and temperature). The Ring Oscillator corresponds to the "entire oscillator" in claim elements 6.c and 13.b because it is the part of the circuit that oscillates naturally in response to PVT. The specifics of this oscillator are not believed to be necessary to these contentions, as the claims simply require an "entire oscillator."

The voltage of the Ring Oscillator, which is illustrated in Ex. B, in the Accused Products 12 may be controlled either by a current control or voltage control. The PLL Control Signal, as 13 illustrated in Ex. B, is an analog signal from the PLL Control Circuit to the Ring Oscillator. If 14 the Ring Oscillator is a current controlled ring oscillator, the PLL Control Signal may adjust the 15 current supplied to the Ring Oscillator. If the Ring Oscillator is a voltage controlled ring 16 oscillator, the PLL Control Signal may adjust the voltage supplied to the Ring Oscillator. Again, 17 this difference is not believed to be important to these Supplemental Contentions. As such, the 18 PLL Control Signal of the Accused Products may control the current or voltage source to the 19 Ring Oscillator. 20

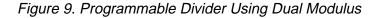

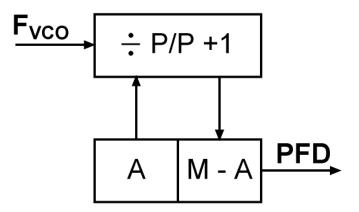

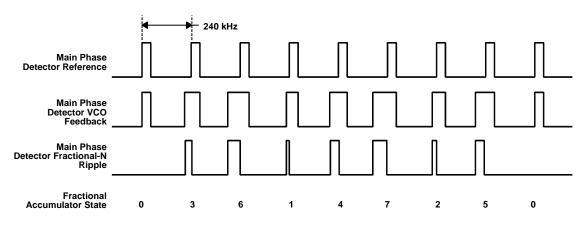

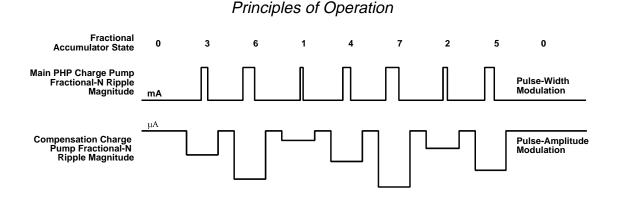

As shown in Ex. B, the Programmable Divisor is a storage element that contains a value that is used to divide down the frequency of the signal on the Feedback Loop input to the Divisor. This behavior is well known in the art. *See, e.g.*, Fractional/Integer-N PLL Basics, Technical Brief SWRA029, Texas Instruments, 2010 (attached hereto as Exhibit C). For example, the Programmable Divisor may contain the value 8. In the instance that the frequency of the signal on the Feedback Loop was 800 MHz, the frequency of the signal on the Feedback Loop when it exited the Programmable Divisor would be 100 MHz.

28

1

2

3

4

5

6

7

8

9

10

11

PLAINTIFFS' SECOND AMENDED INFRINGEMENT CONTENTIONS

Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 4 of 11

The other elements in shown in Ex. B are also well known in the art and are not further explained here.

2 3

4

5

6

7

8

9

10

11

12

13

14

II.

1

## AN OSCILLATOR . . . THAT DOES NOT REQUIRE A COMMAND INPUT TO CHANGE THE CLOCK FREQUENCY

Plaintiffs' position regarding disclaimer (a) is that using a command input to change the frequency of the Ring Oscillator found in the Accused Products is allowable, but it cannot be the sole means by which the frequency of the oscillator's oscillations are changed. In other words, the claim language having this disclaimer is met as long as something other than a command input can change the frequency of the Ring Oscillator. Moreover, since a ring oscillator is by nature inherently variable in response to process, voltage and temperature ("PVT") changes, no command input is ever *required* to change the clock frequency. *See also HTC Corp. v. Tech. Props. Ltd.*, Case No: C-08-00882-PSG, Trial Tr. vol. 3, 627:25-629:11, Sept. 25, 2013 (testimony of Dr. Oklobdzija regarding the "well-known fact" that chips vary due to process, voltage, and temperature).

The Federal Circuit explained that each of the statements made during prosecution were 15 made in such a way to explain that the architecture of the chip "eliminates the need for a 16 command input to change clock frequency" but that "none of [the prosecution history] statements 17 disclaim an entire oscillator receiving a command input for any purpose." See Fed. Cir. Opinion 18 at 16. The opinion highlights that the Patentee argued that Sheets' clock system was "unrelated" 19 to the claimed invention, that "no command input was necessary to change the clock 20 frequency," and that the claims did not "rely upon the provision of frequency control 21 information to an external clock." Id. (underlining added). The Federal Circuit intentionally 22 used the word *require* rather than *utilize*, use, or *include*, which makes clear that the Federal 23 Circuit held that while the entire oscillator may also have a command input which changes the 24 frequency, it may not be the sole means of doing so. 25

As discussed in the subsections below, the clock frequency of the Ring Oscillators in the processors of the Accused Products can be changed by mechanisms other than by "command inputs." *See* Ex. A, where the processors are listed in Column B and referred to herein as

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 5 of 11

"Accused Products' Processors." As an example and assuming *arguendo* that the writing of a value to the Programmable Divisor on the Feedback Loop of the PLL System is a "command input," the frequency of oscillation of the Ring Oscillators in the Accused Products' Processors contained in the Accused Products of Ex. A can change by means other than "command inputs" reprogramming the Programmable Divisor.

## 6

1

2

3

4

5

7

# A. The PLL Control Circuit Manages the Frequency Range of the Oscillators in the Accused Products

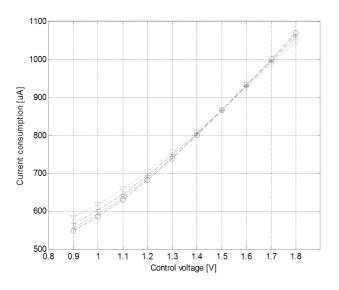

Plaintiffs contend that the PLL Control Circuit, shown in Ex. B and found in the Accused 8 Products' Processors, makes adjustments to the PLL Control Signal to adjust the frequency at 9 which the Ring Oscillator oscillates even when the Programmable Divisor is at a constant value 10 and the PLL circuit as a whole is "locked." By definition, a Ring Oscillator requires only a 11 supply voltage to oscillate, and thus adjustments are made by regulating voltage. These 12 adjustments are used to keep the frequency of the Ring Oscillator within a predetermined range 13 as conditions surrounding the Ring Oscillator change (e.g., electrical and temperature 14 conditions). Neither voltage supply variations to the Ring Oscillator nor environmental or 15 temperature changes of the Oscillator is a "command input" used to change the clock frequency, 16 yet these factors affect the frequency at which the Oscillator oscillates. 17

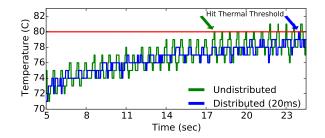

In the case where the frequency of the Ring Oscillator decreases when the temperature of 18 the Ring Oscillator increases, as the temperature increases, the PLL Control Circuit will, at some 19 point, determine that the frequency of the signal on the Feedback Loop has drifted outside the 20 predetermined range of the PLL. In a hypothetical example, at Point in Time A, the temperature 21 of the Ring Oscillator is at 23 °C (room temperature), the Oscillator is oscillating at 200 MHz, 22 the frequency of the Reference Signal is 50 MHz, and the voltage of the Control Signal is at 23 0.5V. Later, at Point in Time B, the temperature of the Ring Oscillator has risen to 24 °C which 24 causes the Oscillator to oscillate at 199.5 MHz (with all other values being the same as at Point in 25 Time A). In this situation, the PLL Control Circuit will increase the voltage of the Control Signal 26 to 0.6 V, which will then cause the Oscillator to again start oscillating at 200 MHz (the desired 27 value). 28

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 6 of 11

In actuality, the adjustments described in the preceding paragraph occur nearly in real time and may be much smaller in magnitude than described above. In other words, there are many, many small sporadic adjustments to the Control Signal. But, the cumulative adjustments made to the frequency of the Ring Oscillator through the PLL Control Signal may be in the tens or hundreds of megahertz as the temperature of the Ring Oscillator changes. PLLs experience both long-term (hours, days, months) and short-term (seconds or less) instability.

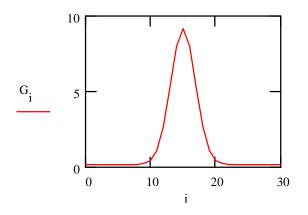

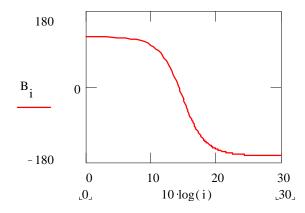

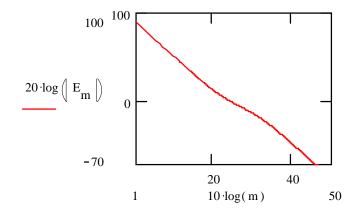

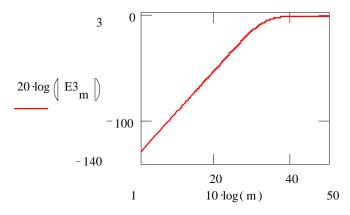

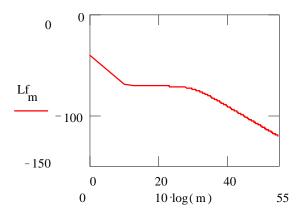

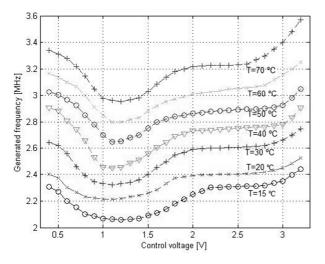

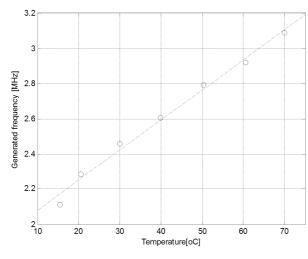

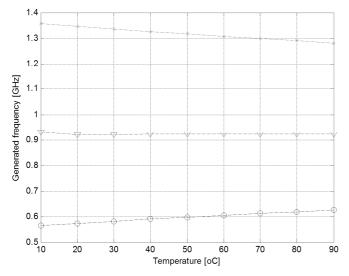

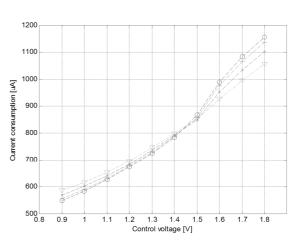

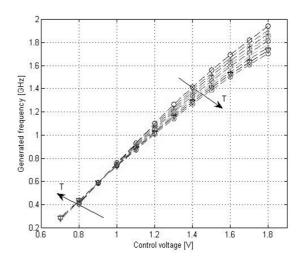

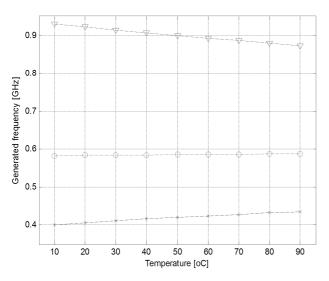

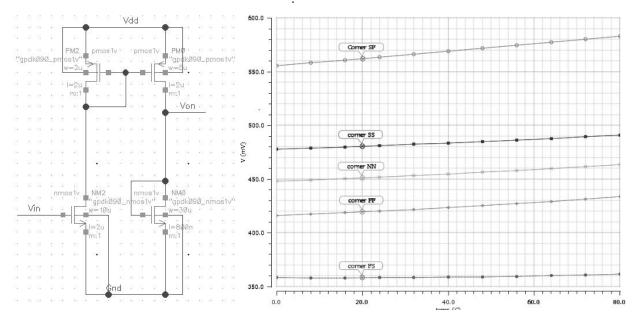

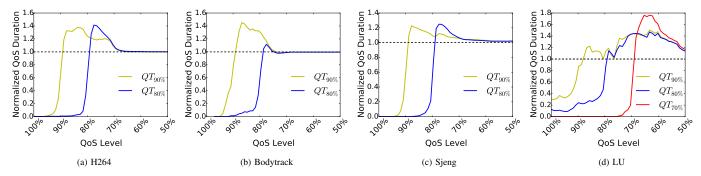

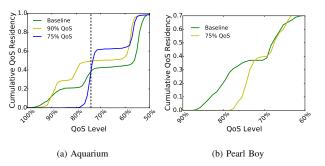

Exhibit D is a document titled "Thermal Analysis of CMOS Voltage-Controlled 7 Oscillators" by Maciej Frankiewicz and Andrzej Kos (the "Kos Article"). Figure 6 of the Kos 8 Article shows how the frequency of the ring oscillator described in the article varies as a function 9 of temperature, with the control voltage being held steady. Looking at the top curve, the 10 particular ring oscillator being discussed operates at approximately 1.35 MHz at 10 °C and 11 operates at approximately 1.29 MHz at 90 °C. If one wished to hold the frequency of this 12 oscillator relatively constant through the use of a PLL Control Circuit, such a Circuit would have 13 to provide a cumulative upward adjustment to the ring oscillator described in the Kos Article of 14 60 MHz (1.35-1.29 MHz) as the circuit's temperature increased from 10 to 90 °C. Such 15 adjustments would, most likely, be in the form of increasing the tuning voltage of the ring 16 oscillator. See also Exhibit E, which is a document titled "Low Power, Temperature and Process 17 Compensated CMOS Ring Oscillator" by Mihai Eugen Marin and Razvan Cristian Marin at 1 18 (stating "Without any compensation scheme the central frequency drift of the CMOS [ring] 19 oscillator can be up to 100% when the temperature is varied."). 20

Further, the only way the PLL Control Circuit would know to make such adjustments would be due to the fact that it has sensed that the frequency of the Ring Oscillator has moved outside the predetermined range of the PLL. In other words, the PLL Control Circuit first detects that the frequency of the Ring Oscillator has moved outside the predetermined range, and then adjusts it (higher or lower as required) back into the predetermined range.

Plaintiffs contend that the Ring Oscillators in the Accused Products' Processors previously identified in the First Amended Infringement Contentions function in a similar manner. The frequency of the Ring Oscillators in the Accused Products' Processors vary as a

PLAINTIFFS' SECOND AMENDED INFRINGEMENT CONTENTIONS

1

2

3

4

5

6

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 7 of 11

result of electrical and environmental variations, but for sporadic adjustments to the frequency of the oscillator by a control signal - which signal has been stimulated by the changing frequency of the Ring Oscillator. Thus, the PLL Control Circuit can and does sporadically adjust the frequency of the Ring Oscillator in the Accused Products Processors in the absence of anything that could be considered a "command input."

6

1

2

3

4

5

### **B.** Variation of the Ring Oscillator Prior to Phase Lock

During power up and state changes of the PLL (e.g., when the Programmable Divisor is 7 altered), the frequency range in which the Ring Oscillators oscillate is not "phase locked" to the 8 Reference Signal. Ring Oscillators, like most physical devices, cannot move from one state to 9 another instantly. In the specific case of Ring Oscillators, they cannot change instantly from 10 oscillating at 0 Hz (at power-up) to 400 MHz instantaneously. Likewise, they cannot change 11 from 400 MHz to 1000 MHz in an instant. Instead, it takes a finite amount of time for the Ring 12 Oscillators to reach the desired frequency and to settle at that frequency. During this period of 13 time, the frequency at which the Ring Oscillators are oscillating will not be related to the 14 Reference Signal by the PLL Control Circuit. Plaintiffs contend these variations in frequency of 15 the Ring Oscillators are not in response to a "command input." 16

17

#### C. Variation of the Oscillator during Phase Lock

Plaintiffs contend that the frequency at which the Ring Oscillators in the Accused 18 Products' Processor oscillate varies due to the inherent nature of the Ring Oscillators to change 19 frequency as a result of temperature and voltage and process variations, even when the Ring 20 Oscillators are phase locked by the PLL Control Circuit. As discussed in the '336 Patent, ring 21 oscillators, in general, tend to vary as a result of process, voltage, and temperature variations. 22 The function of the PLL Control Circuit in the Accused Products' Processors is to manage the 23 inherent and unavoidable frequency variations of the Ring Oscillators from varying as much as 24 they would in the absence of the PLL Control Signal. But, keeping this range overly small can 25 make a PLL System more expensive and consume more power. The optimal range is one that 26 allows for some natural variations of the frequency of the Ring Oscillator, yet is not so great as to 27 introduce errors into the CPU which is being clocked by the Ring Oscillator. The range of 28

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 8 of 11

variation over which the Ring Oscillators in the Accused Products' Processor oscillate is evidence that the frequency of oscillation of the Ring Oscillator varies in the absence of a "command input."

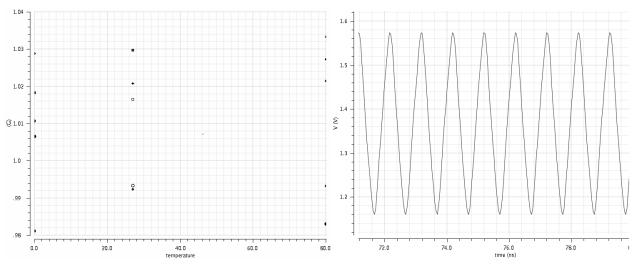

Furthermore, the management of the Ring Oscillators' frequency occurs no more than once every cycle of the Reference Signal. In an exemplary case, where the frequency of the Reference is 20 MHz and the frequency of the Ring Oscillator is 1.28 GHz (64 times that of the Reference Signal), adjustments (if any) to the frequency of the Ring Oscillator will occur no more often than once every 64 cycles of the Ring Oscillator (i.e., once for every cycle of the Reference Signal). For the intervening cycles, the Ring Oscillator will be free running and will not be controlled by the PLL Control Circuit. During these intervening cycles, the frequency of the Ring Oscillator can change and is additional evidence that the frequency of the Ring Oscillator does not require a "command input" to change frequency.

12 13

1

2

3

4

5

6

7

8

9

10

11

### **D.** Thermal Throttling of the Accused Products' Processors

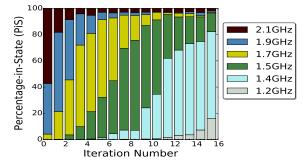

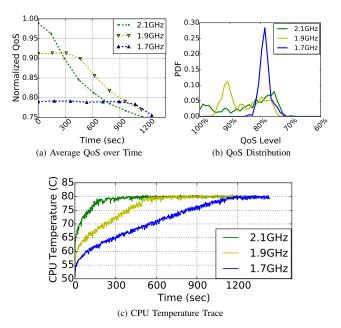

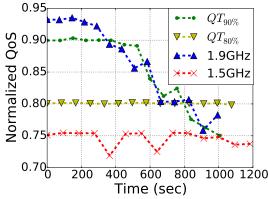

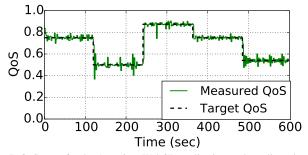

Plaintiffs contend that modern phones and tablets implement a technique called "thermal 14 throttling" which reduces the operating frequency of the phone/tablet's processor if the 15 temperature of the processor becomes too high. See "Just Enough is More: Achieving 16 Sustainable Performance in Mobile Devices under Thermal Limitations" by Onur Sahin, Paul 17 Thomas Varghese, Ayse K. Coskun at 1 (attached hereto as Exhibit F, the "Coskun Article") 18 (stating "modern mobile systems adopt CPU throttling techniques that adaptively reduce the 19 operating frequency of the mobile processor to mitigate thermal emergencies."). Reducing the 20 operating frequency of the mobile processor means that the frequency at which the ring oscillator 21 in the mobile system oscillates is lowered to reduce the heat generated by the processor (the 22 higher a frequency a processor operates, the more energy it consumes and the higher the 23 temperature of the processor (all other things being constant)). 24

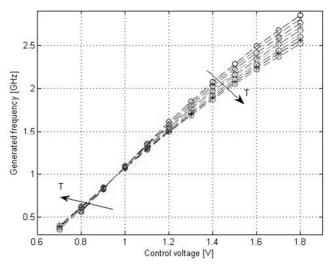

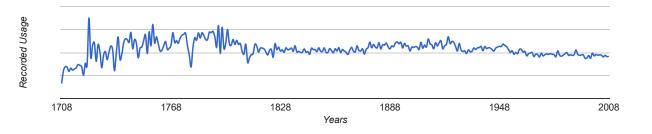

The Coskun Article illustrates in Fig. 1 how the frequency at which a Qualcomm MDP8974 processor operates decreases over time as the processor is forced to operate a lower frequencies to meet thermal constraints. Coskun Article, Fig. 1 at 2. Plaintiffs believe that the behavior of the MDP8974 processor is representative of all of the Accused Products' Processors,

PLAINTIFFS' SECOND AMENDED INFRINGEMENT CONTENTIONS

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 9 of 11

to the extent that they can sense temperature and reduce the operating frequency of the processor if the temperature becomes too high. As shown in Fig. 1, the operating frequencies of the MDP8974 vary from 2.1 GHz to 1.2 GHz.

Plaintiffs contend that, to the extent that this thermal throttling is accomplished by some means other than altering the value of the Programmable Divisor in the PLL System of a particular Accused Product, that this throttling demonstrates how the frequency at which the oscillator in an Accused Product can be changed other than through the use of a command input.

Information about how the Accused Products' Processors implement thermal throttling is within the possession of the manufacturers of such Processors, namely Qualcomm, IBM, Texas Instruments, NVidia, and Samsung. Plaintiffs are awaiting this information through discovery requests served prior to this lawsuit being appealed to the Federal Circuit.

## III. AN OSCILLATOR . . . WHOSE FREQUENCY IS NOT FIXED BY ANY EXTERNAL CRYSTAL

Plaintiffs contend that the frequency at which the Ring Oscillators in the Accused Product's Processors oscillate is *never* fixed (by anything), but rather is by nature inherently variable.

These Ring Oscillators oscillate at various frequency ranges to serve a variety of use cases. One use case is that the Ring Oscillators oscillate at low frequencies when the Accused Products are not in use (*e.g.*, standby mode, low-power mode, etc.), which lowers the power consumed by the Accused Products' Processors. In turn, this will lower the power consumption in general, including the power drawn from the batteries of the Accused Products. Additional side effects of drawing lower power will be that the Products will operate at lower temperatures which may lengthen the life of the Processors and other components in the Accused Products.

A separate use case is when the Accused Products are required to perform some computationally intensive tasks and/or have a number of tasks to perform at one time. In such cases, the Ring Oscillators oscillate at higher frequency ranges to provide an enhanced user experience (*i.e.*, the Accused Products will "feel" responsive and fast).

28

24

25

26

27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

PLAINTIFFS' SECOND AMENDED INFRINGEMENT CONTENTIONS

### Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 10 of 11

1

2

3

4

5

6

7

Evidence that the Ring Oscillators in the Accused Products' Processors operate at a variety of frequencies, spanning from approximately 400 MHz to over 1500 MHz (in some cases), is found in the documents/pages listed in Column C of Ex. A.

Plaintiffs' interpretation of the term "fixed", as used in the disclaimer found by the Federal Circuit, is "not fluctuating or varying", "definite", or "predetermined and not subject to or able to be changed" (*e.g.*, a fixed interest rate or a fixed period of time). *See* Exhibit G for a list of dictionary definitions of the term "fixed."

Given that the Ring Oscillators in the Accused Products' Processors are variable in 8 frequency and not fixed, Plaintiffs contend that the frequencies of the oscillators are not fixed by 9 any component or device, including an external crystal. Plaintiffs agree that the frequency range 10 of a Ring Oscillator is determined, in part, by the frequency of an external crystal. But, the 11 crystal reference is merely sampled as a basis for comparison, and does not propagate past the 12 PLL Control Circuit. But, by altering the value in the Programmable Divisor, the frequency 13 range of the Ring Oscillator in the Accused Products' Processors is varied during the normal use 14 of the Accused Products. 15

Furthermore, since the Ring Oscillators in the Accused Products' Processors are by nature, inherently variable in response to PVT and are never fixed, Plaintiffs contend that the frequencies of the Oscillators are not fixed by any component or device, including an external crystal. By definition, a Ring Oscillator requires only a supply voltage to oscillate, and thus adjustments are made by regulating voltage. The external crystal is not a voltage supply.

Finally, the variations of frequency described above in Section II further demonstrate that the ring oscillators in the Accused Products' Processors are not "fixed" by an external crystal.

23 Dated: June 16, 2017 Respectfully submitted, 24 /s/ Barry J. Bumgardner 25 **NELSON BUMGARDNER, P.C.** Edward R. Nelson, III (Pro Hac Vice) 26 ed@nelbum.com 27 Brent Nelson Bumgardner (Pro Hac Vice) brent@nelbum.com 28 Barry J. Bumgardner (Pro Hac Vice) PLAINTIFFS' SECOND AMENDED CASE NO. 3:12-cv-03880-VC INFRINGEMENT CONTENTIONS 10

| I        | Case 3:12-cv-03880-VC Document 144 Filed 06/16/17 Page 11 of 11                         |

|----------|-----------------------------------------------------------------------------------------|

| 1        | barry@nelbum.com<br>Thomas Christopher Cecil ( <i>Pro Hac Vice</i> )                    |

| 2        | tom@nelbum.com<br>John Murphy ( <i>Pro Hac Vice</i> )                                   |

| 3        | murphy@nelbum.com<br>3131 West 7 <sup>th</sup> Street, Suite 300                        |

| 4        | Fort Worth, Texas 76107                                                                 |

| 5        | [Tel.] (817) 377-9111<br>[Fax] (817) 377-3485                                           |

| 6        | Attorneys for Plaintiff                                                                 |

| 7        | PHOENIX DIGITAL SOLUTIONS, LLC                                                          |

| 8        |                                                                                         |

| 9        | /s/ William L. Bretschneider (with permission)<br>SILICON VALLEY LAW GROUP              |

| 10       | William L. Bretschneider (SBN 144561)                                                   |

| 11       | wlb@svlg.com<br>50 W. San Fernando Street, Suite 750                                    |

| 12       | San Jose, California 95113<br>[Tel.] (408) 573-5700                                     |

| 13       | [Fax] (408) 573-5701                                                                    |

| 14       | Attorneys for Plaintiff<br>TECHNOLOGY PROPERTIES LIMITED, LLC                           |

| 15       |                                                                                         |

| 16       |                                                                                         |

| 17       |                                                                                         |

| 18       | <b>CERTIFICATE OF SERVICE</b>                                                           |

| 19       | I hereby certify that on June 16, 2017, I caused the foregoing document to be served on |

| 20       | counsel of record via the Court's CM/ECF system.                                        |

| 21       |                                                                                         |

| 22<br>23 | Dated: June 16, 2017By:/s/ Barry J. BumgardnerBarry J. BumgardnerBarry J. Bumgardner    |

| 23<br>24 |                                                                                         |

| 25       |                                                                                         |

| 26       |                                                                                         |

| 27       |                                                                                         |

| 28       |                                                                                         |

|          | PLAINTIFFS' SECOND AMENDED CASE NO. 3:12-cv-03880-VC INFRINGEMENT CONTENTIONS           |

|          | 11                                                                                      |

Case 3:12-cv-03880-VC Document 144-1 Filed 06/16/17 Page 1 of 13

# Exhibit "A"

## EXHIBIT A

| Column A<br>Accused Products                  | Column B<br>Accused Products' Processors      | Column C<br>Citations                                                                                                                                                                                         |

|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG D820 Nexus 5 NA TD-<br>LTE 16GB            | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                |

| LG Incite CT810                               | 32bit Qualcomm MSM7201A                       | QTPL2PDS0042530, QTPL2PDS0042565                                                                                                                                                                              |

| LG P930 Nitro HD                              | 32bit Qualcomm Snapdragon S3<br>APQ8060       | QTPL2PDS0005912, QTPL2PDS000596, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG D725 G3 Vigor / G3 S<br>LTE-A (LG B2 Mini) | 32bit Qualcomm Snapdragon<br>400 MSM8926      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                 |

| LG P509 Optimus T / P504                      | 32bit Qualcomm MSM7227                        | QTPL2PDS004389, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62, QTPL2PDS0015662, QTPL2PDS0015666                                                               |

| LG G2 D801 4G LTE                             | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                |

| LG US740 Apex                                 | 32bit Qualcomm MSM7627                        | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                |

| LG AS680 Optimus 2                                | 32bit Qualcomm MSM7627T                       | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

|---------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG US730 Splendor                                 | 32bit Qualcomm Snapdragon S2<br>MSM8655       | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                                                       |

| LG G3 VS985 LTE-A (LG<br>B2)                      | 32bit Qualcomm Snapdragon<br>801 MSM8974AC v3 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                           |

| LG VS930 Spectrum 2 /<br>Optimus LTE 2            | 32bit Qualcomm Snapdragon S4<br>MSM8960       | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004384                                                                                                                                                                                      |

| LG D415 Optimus L90 / L<br>Series III L90 (LG W7) | 32bit Qualcomm Snapdragon<br>400 MSM8226      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404,<br>QTPL2PDS0014415, QTPL2PDS0078918                                                                                                                                                            |

| LG MS910 Esteem 4G<br>(LG Bryce)                  | 32bit Qualcomm Snapdragon S2<br>MSM8655       | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                                                       |

| LG AS695 Optimus Plus                                   | 32bit Qualcomm MSM7627A                          | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

|---------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG E980 Optimus G Pro<br>5.5 4G LTE                     | 32bit Qualcomm Snapdragon<br>600 APQ8064T        | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                                                                            |

| LG G3 LS990 TD-LTE<br>(LG B2)                           | 32bit Qualcomm Snapdragon<br>801 MSM8974AC v3    | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                           |

| LG LS720 Optimus F3 4G<br>LTE                           | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite     | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                                                                                                     |

| LG D631 G Vista / G Pro 2<br>Lite LTE-A (LG B1 Lite)    | 32bit Qualcomm Snapdragon<br>400 MSM8926         | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                                                                            |

| LG L55C Optimus Q (LG<br>Gelato Q)                      | 32bit Qualcomm MSM7627T                          | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG VS415PP Optimus<br>Zone 2 / L Series III L40<br>CDMA | 32bit Qualcomm Snapdragon<br>200 MSM8210/MSM8610 | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415                                                                                                                                                                                |

| LG US670 Optimus U                                      | 32bit Qualcomm MSM7627                           | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                                                                           |

| LG UK410 G Pad 7.0 LTE<br>(LG E7)    | 32bit Qualcomm Snapdragon<br>400 MSM8926         | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                      |

|--------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG V400 G Pad 7.0 (LG<br>E7)         | 32bit Qualcomm Snapdragon<br>400 MSM8226/APQ8026 | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404,<br>QTPL2PDS0014415,QTPL2PDS0078918                                                                                                       |

| LG V500 G Pad 8.3 WiFi               | 32bit Qualcomm Snapdragon<br>600 APQ8064T        | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                      |

| LG LW770 Optimus<br>Regard           | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite     | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                                               |

| LG E970 Optimus G 4G<br>LTE (LG Gee) | 32bit Qualcomm Snapdragon S4<br>Pro APQ8064      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                      |

| LG LW690 Optimus C                   | 32bit Qualcomm MSM7627                           | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                     |

| LG C729 DoublePlay                   | 32bit Qualcomm Snapdragon S2<br>MSM8255          | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG P870 Escape 4G                    | 32bit Qualcomm Snapdragon S3<br>APQ8060          | QTPL2PDS0005912, QTPL2PDS000596, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798      |

| LG VS920 Spectrum 4G               | 32bit Qualcomm Snapdragon S3<br>MSM8660      | QTPL2PDS0010976-77, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                   |

|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG LS740 Volt 4G TD-<br>LTE / F90  | 32bit Qualcomm Snapdragon<br>400 MSM8926     | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                      |

| LG VS840PP Optimus<br>Exceed       | 32bit Qualcomm Snapdragon S3<br>MSM8660      | QTPL2PDS0010976-77, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                   |

| LG VK700 G Pad 10.1 4G<br>LTE      | 32bit Qualcomm Snapdragon<br>400 MSM8926     | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                      |

| LG C900 Optimus 7Q (LG<br>Pacific) | 32bit Qualcomm Snapdragon S1<br>QSD8250      | QTPL2PDS0109783, QTPL2PDS01 09788-91,<br>QTPL2PDS0109801, QTPL2PDS0015662, QTPL2PDS0015666                                                                                                                         |

| LG LG730 Venice                    | 32bit Qualcomm Snapdragon S2<br>MSM8655      | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG VS870 Lucid 2                   | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                                               |

| LG L45C Optimus Net                  | 32bit Qualcomm MSM7627T                       | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43, QTPL2PDS0016441, QTPL2PDS0004798 |

|--------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG E960 Nexus 4 (LG<br>Mako)         | 32bit Qualcomm Snapdragon S4<br>Pro APQ8064   | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                                                                             |

| LG G Flex 2                          | Qualcomm Snapdragon 810                       | PDSND165482                                                                                                                                                                                                                                                               |

| LG Optimus F7 US780                  | 32bit Qualcomm Snapdragon S4<br>MSM8960       | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004384                                                                                                                                                                                       |

| LG MS323 L Series III<br>L70 (LG W5) | 32bit Qualcomm Snapdragon<br>200 MSM8210      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415                                                                                                                                                                                 |

| LG MS659 Optimus F3 4G<br>LTE        | 32bit Qualcomm Snapdragon<br>400 MSM8930      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0097028-30, QTPL2PDS0097587                                                                                                                                         |

| LG VM720 Optimus F3<br>4G LTE        | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite  | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                                                                                                      |

| LG Optimus F7 LG870                  | 32bit Qualcomm Snapdragon S4<br>MSM8960       | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004384                                                                                                                                                                                       |

| LG P925 Thrill 4G                    | 32bit Texas Instruments OMAP<br>4430          | See generally PDSND136955-137050, and particularly PDSND136959-136968                                                                                                                                                                                                     |

| LG VK810 G Pad 8.3 4G<br>LTE         | 32bit Qualcomm Snapdragon<br>600 APQ8064T     | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                                                                             |

| LG LS995 G Flex TD-LTE               | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                            |

| LG D520 Optimus F3Q 4G<br>LTE (LG FX3) | 32bit Qualcomm Snapdragon<br>400 MSM8930      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0097028-30, QTPL2PDS0097587                                                                |

|----------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG G3 D851 LTE-A (LG<br>B2)            | 32bit Qualcomm Snapdragon<br>801 MSM8974AC v3 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                   |

| LG VN270 Cosmos Touch                  | Qualcomm QSC6055                              | QTPL2PDS0015662, QTPL2PDS0015666                                                                                                                                                                 |

| LG MS840 Connect 4G<br>(LG Cayman)     | 32bit Qualcomm Snapdragon S3<br>MSM8660       | QTPL2PDS0010976-77, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG MS870 Spirit 4G                     | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite  | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                             |

| LG LS860 Mach 4G LTE<br>(LG Cayenne)   | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite  | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                             |

| LG VS980 G2 4G LTE                     | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                   |

| LG E960 Nexus 4 16GB<br>(LG Mako)      | 32bit Qualcomm Snapdragon S4<br>Pro APQ8064   | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                    |

| LG D959 G Flex                         | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                   |

| LG Ally VS740                          | 32bit Qualcomm MSM7627                        |                                                                                                                                                                                                  |

| LG G3 D850 LTE-A (LG<br>B2)            | 32bit Qualcomm Snapdragon<br>801 MSM8974AC v3 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                   |

| LG V909 Optimus Pad /<br>G-Slate                      | 32bit NVIDIA Tegra 2 250 T20                | PDSND128215                                                                                                                                                                                                        |

|-------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG Fathom VS750                                       | 32bit Qualcomm Snapdragon S1<br>QSD8650     | QTPL2PDS0109783, QTPL2PDS01 09788-91,<br>QTPL2PDS0109801, QTPL2PDS0015662, QTPL2PDS0015666                                                                                                                         |

| LG MS690 Optimus M                                    | 32bit Qualcomm MSM7627                      | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                     |

| LG LS970 Optimus G /<br>Eclipse 4G (LG Gee)           | 32bit Qualcomm Snapdragon S4<br>Pro APQ8064 | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                      |

| LG D500 Optimus F6                                    | 32bit Qualcomm Snapdragon<br>400 MSM8930    | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0097028-30, QTPL2PDS0097587                                                                                  |

| LG LS696 / VM696<br>Optimus Elite                     | 32bit Qualcomm MSM8655                      | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG VS810PP L Fino LTE                                 | 32bit Qualcomm Snapdragon<br>200 MSM8212    | QTPL2PDS0092329, QTPL2PDS0092422, QTPL2PDS0092467,<br>QTPL2PDS0092474, QTPL2PDS0092628, QTPL2PDS0014190-<br>95, QTPL2PDS0013205, QTPL2PDS0014399,<br>QTPL2PDS0014404, QTPL2PDS0014415                              |

| LG P769 Optimus L9                                    | 32bit Texas Instruments OMAP<br>4430        | See generally PDSND136955-137050, and particularly PDSND136959-136968                                                                                                                                              |

| LG G4                                                 | Qualcomm Snapdragon 808                     | PDSND165482                                                                                                                                                                                                        |

| LG VS880 G Vista / G Pro<br>2 Lite LTE-A (LG B1 Lite) | 32bit Qualcomm Snapdragon<br>400 MSM8926    | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                      |

| LG V700 G Pad 10.1 WiFi                  | 32bit Qualcomm Snapdragon<br>400 APQ8026      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415                                                                                                                                                                                |

|------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG V410 G Pad 7.0 LTE<br>(LG E7)         | 32bit Qualcomm Snapdragon<br>400 MSM8926      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                                                                            |

| LG LS980 G2 TD-LTE                       | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                           |

| LG G2 D800 4G LTE                        | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                           |

| LG VM701 Optimus Slider<br>(LG Gelato Q) | 32bit Qualcomm MSM7627T                       | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG LS840 Viper 4G LTE                    | 32bit Qualcomm Snapdragon S3<br>MSM8660       | QTPL2PDS0010976-77, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                                                                         |

| LG MS695 Optimus M+                      | 32bit Qualcomm MSM7627A                       | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG VS660 Vortex                               | 32bit Qualcomm MSM7627                    | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                                                                           |

|-----------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG MS395 F60 4G LTE                           | 64bit Qualcomm Snapdragon<br>410 MSM8916  | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0092826, QTPL2PDS0092947,                                                                                                                                          |

| LG LS670 Optimus S                            | 32bit Qualcomm MSM7627                    | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                                                                           |

| LG LS855 Marquee                              | 32bit Texas Instruments OMAP<br>3630      | See generally PDSND133115-177, and particularly PDSND133125-132                                                                                                                                                                                                          |

| LG VS700 Enlighten (LG<br>Gelato Q)           | 32bit Qualcomm MSM7627T                   | QTPL2PDS0084161, QTPL2PDS0084333, QTPL2PDS0085583,<br>QTPL2PDS0085658, QTPL2PDS0085661-62,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG LS885 G3 Vigor TD-<br>LTE (LG B2 Mini)     | 32bit Qualcomm Snapdragon<br>400 MSM8926  | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                                                                            |

| LG VS950 Intuition /<br>Optimus Vu            | 32bit Qualcomm Snapdragon S4<br>MSM8960   | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004384                                                                                                                                                                                      |

| LG V510 G Pad 8.3 WiFi<br>Google Play Edition | 32bit Qualcomm Snapdragon<br>600 APQ8064T | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0076265                                                                                                                                                            |

| LG VS890 Enact (LG<br>FX3)                    | 32bit Qualcomm Snapdragon<br>400 MSM8930  | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0097028-30, QTPL2PDS0097587                                                                                                                                        |

| LG VS876 Lucid 3 / F90<br>LTE           | 32bit Qualcomm Snapdragon<br>400 MSM8926      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                                                                                            |

|-----------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG G3 US990 LTE-A /<br>AS990 (LG B2)    | 32bit Qualcomm Snapdragon<br>801 MSM8974AC v3 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                                                                                           |

| LG UN270 Attune                         | Qualcomm QSC6055                              | QTPL2PDS0015662, QTPL2PDS0015666                                                                                                                                                                                                                                         |

| LG VS910 Revolution 4G                  | 32bit Qualcomm Snapdragon S2<br>MSM8655       | QTPL2PDS0060696-97, QTPL2PDS0060574,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798                                                       |

| LG MS770 Motion 4G                      | 32bit Qualcomm Snapdragon S4<br>MSM8960 Lite  | QTPL2PDS0019673, QTPL2PDS0004585, QTPL2PDS0004706, QTPL2PDS0004735, QTPL2PDS0004378, QTPL2PDS0004384                                                                                                                                                                     |

| LG AS740 Axis                           | 32bit Qualcomm MSM7627                        | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                                                                                           |

| LG GW820 eXpo (LG<br>Monaco)            | 32bit Qualcomm Snapdragon S1<br>QSD8650       | QTPL2PDS0109783, QTPL2PDS01 09788-91,<br>QTPL2PDS0109801, QTPL2PDS0015662, QTPL2PDS0015666                                                                                                                                                                               |

| LG VS410PP Optimus<br>Zone / Optimus L3 | 32bit Qualcomm MSM7625A                       | QTPL2PDS0022015, QTPL2PDS0022032, QTPL2PDS0023960,<br>QTPL2PDS0023965, QTPL2PDS0023969-72,<br>QTPL2PDS0050684, QTPL2PDS0050688, QTPL2PDS0013875-<br>76, QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

| LG MS500 Optimus F6                     | 32bit Qualcomm Snapdragon<br>400 MSM8930      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0097028-30, QTPL2PDS0097587                                                                                                                                        |

| LG VM670 Optimus V                      | 32bit Qualcomm MSM7627                        | QTPL2PDS0084161, QTPL2PDS0084161, QTPL2PDS0084333,<br>QTPL2PDS0085583, QTPL2PDS0085658, QTPL2PDS0085661-<br>62                                                                                   |

|-----------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LG D950 G Flex                          | 32bit Qualcomm Snapdragon<br>800 MSM8974AA v2 | QTPL2PDS001336, QTPL2PDS0080648, QTPL2PDS0080682,<br>QTPL2PDS0080690, QTPL2PDS0080976, QTPL2PDS0014827,<br>QTPL2PDS0015274-275, QTPL2PDS001352, QTPL2PDS001352                                   |

| LG LS660 Tribute 4G TD-<br>LTE / LS660P | 32bit Qualcomm Snapdragon<br>400 MSM8926      | QTPL2PDS0014190-95, QTPL2PDS0013205,<br>QTPL2PDS0014399, QTPL2PDS0014404, QTPL2PDS0014415,<br>QTPL2PDS0078918                                                                                    |

| LG VS840 Lucid 4G (LG<br>Cayman)        | 32bit Qualcomm Snapdragon S3<br>MSM8660       | QTPL2PDS0010976-77, QTPL2PDS0050684,<br>QTPL2PDS0050688, QTPL2PDS0013875-76,<br>QTPL2PDS0013878, QTPL2PDS0013882-85,<br>QTPL2PDS0013907, QTPL2PDS0013842-<br>43,QTPL2PDS0016441, QTPL2PDS0004798 |

Case 3:12-cv-03880-VC Document 144-2 Filed 06/16/17 Page 1 of 2

# Exhibit "B"

## Case 3:12-cv-03880-VC Document 144-2 Filed 06/16/17 Page 2 of 2 Exhibit B

## **Representative Clocking System**

Case 3:12-cv-03880-VC Document 144-3 Filed 06/16/17 Page 1 of 56

# Exhibit "C"

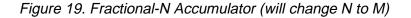

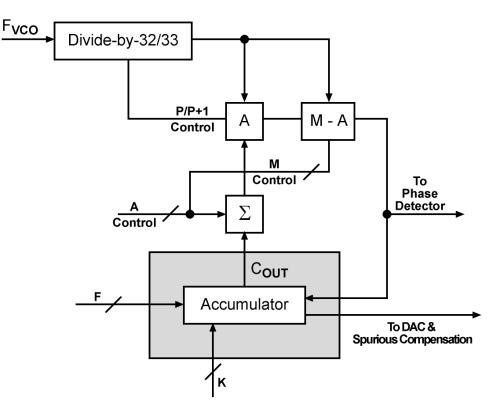

## Fractional/Integer-N PLL Basics

Edited by Curtis Barrett

Wireless Communication Business Unit

## Abstract

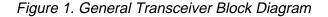

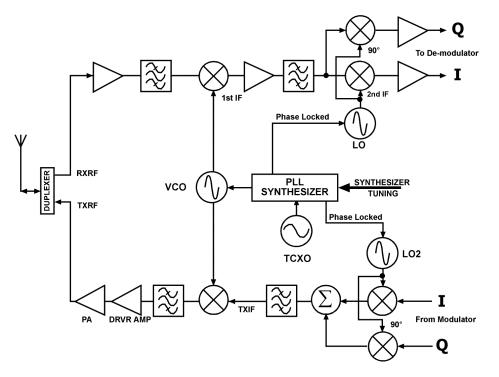

Phase Locked Loop (PLL) is a fundamental part of radio, wireless and telecommunication technology. The goal of this document is to review the theory, design and analysis of PLL circuits. PLL is a simple negative feedback architecture that allows economic multiplication of crystal frequencies by large variable numbers. By studying the loop components and their reaction to various noise sources, we will show that PLL is uniquely suited for generation of stable, low noise tunable RF signals for radio, timing and wireless applications.

Some of the main challenges fulfilled by PLL technology are economy in size, power and cost while maintaining good spectral purity.

This document details basic loop transfer functions, loop dynamics, noise sources and their effect on signal noise profile, phase noise theory, loop components (VCO, crystal oscillators, dividers and phase detectors) and principles of integer-N and fractional-N technology. The approach will be mainly heuristic, with many design examples.

This document is written for designers, technicians and project managers. Design procedures, equations, performance interpretation, CAD and examples are included to help those who have little experience. A list of reference books and articles is also included.

## Ų

### Contents

| Introduction to Phase Locked Loop (PLL)                           | 5  |

|-------------------------------------------------------------------|----|

| Digital PLL Synthesis<br>PLL Components                           |    |

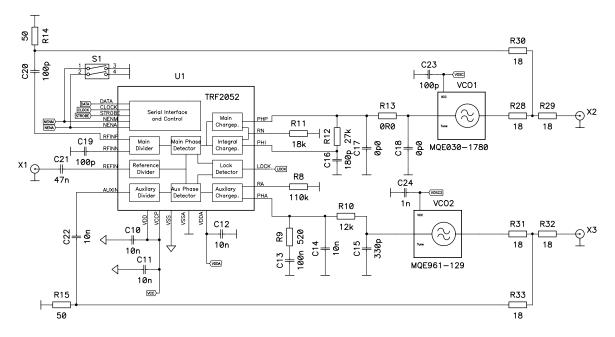

| Voltage Controlled Oscillators (VCO)                              |    |

| Phase Frequency Detectors (PFD)                                   | 0  |

| Dividers                                                          |    |

| Loop Filter                                                       |    |

| The Simple Math of PLL                                            |    |

| Feedback Loop Analysis                                            |    |

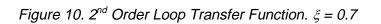

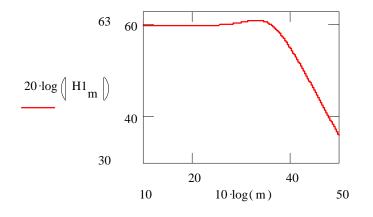

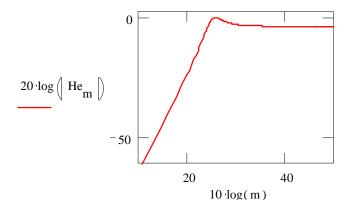

| Loop Transfer Function                                            |    |

| Loop Filter Design                                                | 17 |

| Natural Frequency and Loop Bandwidth                              |    |

| Passive Loops and Charge Pump                                     |    |

| Lock-up Time and Speed Up                                         |    |

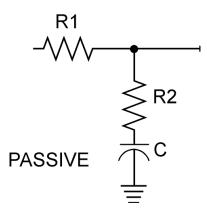

| Loop Order and Type                                               | 24 |

| Loop Stability and Phase Margin                                   | 24 |

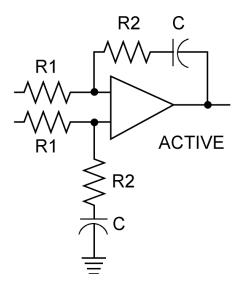

| Active and Passive Loops Summary                                  | 25 |

| Modulation                                                        |    |

| Integer-N PLL                                                     |    |

| Concept<br>Basic Operation                                        |    |

| Functional Description                                            |    |

| Advantages and Limitations                                        |    |

| Fractional-N PLL                                                  |    |

| Concept                                                           |    |

| Functional Description                                            |    |

| Divider Dynamics                                                  |    |

| Fractional Accumulator                                            |    |

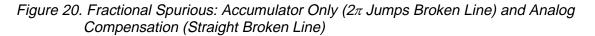

| Fractional Spurious Signals and Compensation                      |    |

| Advantages and Limitation                                         |    |

| Comparison                                                        |    |

| Phase Noise                                                       |    |

| Definitions and Conversions<br>Division and Multiplication Effect |    |

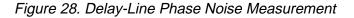

| Phase Noise Measurements                                          |    |

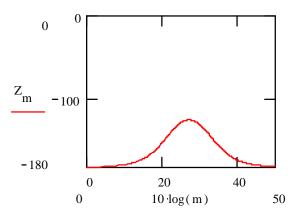

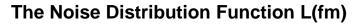

| The Noise Distribution Function L(fm)                             | 44 |

| Noise Sources in PLL                                              | 44 |

| Spurious Suppression                                              | 46 |

| Reference Spurious Signals                                        |    |

| Fractional Spurious Signals                                       |    |

| Spurious Signal Suppression                                       | 47 |

| The Effect of Phase Noise on System Performance                   |    |

| Loop Response Simulation<br>Multi-Loop Design                     |    |

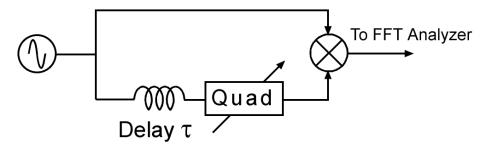

| Measurements Techniques                                           |    |

| Phase Noise                                                       |    |

| Spurious Signals                                                  |    |

| Switching Speed                                                   |    |

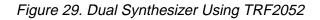

| The TI Family of PLL ASICs                                        | 51 |

| Summary and FAQ                                                   | 52 |

| Glossary                                                          |    |

| References and Further Reading                                    |    |

|                                                                   |    |

## Ų

## Figures

| Figure 1. General Transceiver Block Diagram                                                                                 | 4  |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Integer-N (classical) PLL Block Diagram                                                                           | 5  |

| Figure 3. L-Band VCO Schematics                                                                                             | 9  |

| Figure 4. Oscillator Open Loop Gain Model                                                                                   | 10 |

| Figure 5. Oscillator Open Loop Phase Model                                                                                  | 10 |

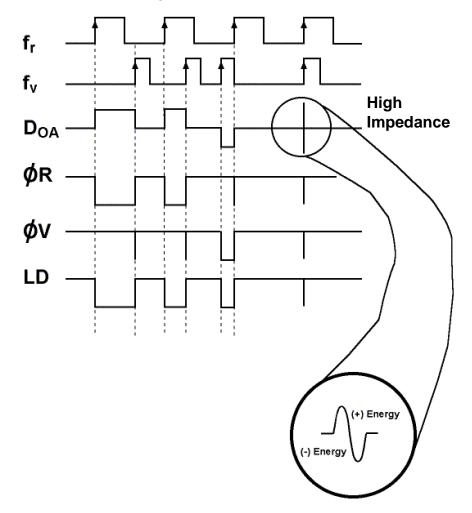

| Figure 6. Phase Frequency Detector Schematic                                                                                |    |

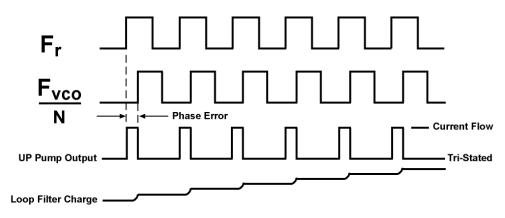

| Figure 7. Phase Detector Output (Voltage, Current) Waveforms, for Fv/N <fr< td=""><td></td></fr<>                           |    |

| Figure 8. Phase Detector Timing Waveforms                                                                                   |    |