|              |                                                                                                                                 | Lector                                                            | $\sim$                                        |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------|

| <b>A</b> )   |                                                                                                                                 | Approved for use through 04/                                      | 30/2007. OMB 0651-0033                        |

|              | e Paperwork Reduction Act of 1995, no persons are required to report to a colle                                                 | ction of information unless it displays a v                       | valid OMB control number.                     |

| 71338 U.S. 🍂 | EQUEST FOR EX PARTE REEXAMINATION                                                                                               |                                                                   | 90008237                                      |

|              | Address to:<br>Mail Stop Ex Parte Reexam<br>Commissioner for Patents<br>P.O. Box 1450                                           | Attorney Docket No.: 06                                           | 0 <b>9/21/06</b><br>99974-0160                |

|              | Alexandria, VA 22313-1450                                                                                                       | Date: September 21,                                               |                                               |

| 1. <u>X</u>  | This is a request for <i>ex parte</i> reexamination pursuant to 37 CF issued <u>September 15, 1998</u> . The request is made by | y:                                                                | 809.336                                       |

|              | patent owner.                                                                                                                   | er.                                                               |                                               |

| 2. X         | The name and address of the person requesting reexamination                                                                     | n is:                                                             | -                                             |

|              | Matthew A. Smith, on behalf of NEC Elect                                                                                        | ronics Americ <b>a</b> , Inc.                                     |                                               |

|              | Foley & Lardner LLP                                                                                                             |                                                                   |                                               |

|              | 3000 K Street NW, Suite 500, Washington,                                                                                        | DC 20007                                                          |                                               |

| 3.           | a. A check in the amount of \$ is enclosed to                                                                                   | o cover the reexamination fee, 3                                  | 37 CFR 1.20(c)(1);                            |

|              | <ul> <li>b. The Director is hereby authorized to charge the fee as set<br/>to Deposit Account No(s)</li> </ul>                  | st forth in 37 CFR 1.20(c)(1)<br>ubmit duplicative copy for fee p | processing); or                               |

| X            | c. Payment by credit card. Form PTO-2038 is attached.                                                                           |                                                                   |                                               |

| 4.           | Any refund should be made by C check or C credit to 37 CFR 1.26(c). If payment is made by credit card, refund m                 | Deposit Account No<br>ust be to credit card account.              | <u></u> .                                     |

| 5. <u>X</u>  | A copy of the patent to be reexamined having a double colu<br>enclosed. 37 CFR 1.510(b)(4)                                      | mn format on one side of a sep                                    | parate paper is                               |

| 6.           | CD-ROM or CD-R in duplicate, Computer Program (Append<br>Landscape Table on CD                                                  | lix) or large table                                               |                                               |

| 7.           | Nucleotide and/or Amino Acid Sequence Submission<br>If applicable, items a. – c. are required.                                  |                                                                   |                                               |

|              | a. Computer Readable Form (CRF)<br>b. Specification Sequence Listing on:                                                        |                                                                   |                                               |

|              | i. CD-ROM (2 copies) or CD-R (2 copies); or<br>ii. paper                                                                        |                                                                   |                                               |

|              | c. Statements verifying identity of above copies                                                                                |                                                                   |                                               |

| 8.           | A copy of any disclaimer, certificate of correction or reexamin                                                                 | ation certificate issued in the p                                 | atent is included.                            |

| 9. 🗶         | Reexamination of claim(s) $1 - 10$                                                                                              |                                                                   | is requested.                                 |

| 10. X        | A copy of every patent or printed publication relied upon is sul<br>Form PTO/SB/08, PTO-1449, or equivalent.                    | bmitted Herewith Including Bills<br>01 FC:1812                    | 6693 98988237<br>669 thereof on<br>2520.00 0P |

| 11.          | An English language translation of all necessary and pertinent publications is included.                                        | t non-English language patents                                    | s and/or printed                              |

| L            | [Page 1 of 2]                                                                                                                   |                                                                   | to file (and by the LISPTO                    |

This collection of information is required by 37 CFR 1.510. The information is required to 0 2j to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 2 hours to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Mail Stop Ex Parte Reexam, Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450. If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

| Under the Paperwork Reduction Act of 1995, no pers                                                                                                                                                                                                                                            | sons are required to                                                                                                                                                                                                                                                           | U.S. Patent and Trademark C                                                                                                 | PTO/SB/57 (04-05)<br>for use through 04/30/2007. OMB 0651-0033<br>Office; U.S. DEPARTMENT OF COMMERCE<br>nless it displays a valid OMB control number. |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 12. X The attached detailed request includ                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                |                                                                                                                             |                                                                                                                                                        |  |  |  |

| a. A statement identifying each subs<br>publications. 37 CFR 1.510(b)(1)<br>b. An identification of every claim for<br>and manner of applying the cited                                                                                                                                       | tantial new que<br>which reexami                                                                                                                                                                                                                                               | stion of patentability based on p<br>nation is requested, and a deta                                                        | iled explanation of the pertinency                                                                                                                     |  |  |  |

| 13. A proposed amendment is included                                                                                                                                                                                                                                                          | (only where the                                                                                                                                                                                                                                                                | patent owner is the requester).                                                                                             | . 37 CFR 1.510(e)                                                                                                                                      |  |  |  |

| 14. X a. It is certified that a copy of this red<br>the patent owner as provided in 3                                                                                                                                                                                                         | <ul> <li>a. It is certified that a copy of this request (if filed by other than the patent owner) has been served in its entirety on the patent owner as provided in 37 CFR 1.33(c).</li> <li>The name and address of the party served and the date of service are:</li> </ul> |                                                                                                                             |                                                                                                                                                        |  |  |  |

| Mr. Drew S. Hamilto                                                                                                                                                                                                                                                                           | n                                                                                                                                                                                                                                                                              |                                                                                                                             |                                                                                                                                                        |  |  |  |

| Knobbe, Martens, 01                                                                                                                                                                                                                                                                           | .son & Be <b>a</b> r                                                                                                                                                                                                                                                           | , LLP                                                                                                                       |                                                                                                                                                        |  |  |  |

| 550 W C St. Suite 1                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                |                                                                                                                             |                                                                                                                                                        |  |  |  |

| Date of Service: September                                                                                                                                                                                                                                                                    | 21, 2006                                                                                                                                                                                                                                                                       |                                                                                                                             | ; or                                                                                                                                                   |  |  |  |

| b. A duplicate copy is enclosed sin                                                                                                                                                                                                                                                           | ice service on p                                                                                                                                                                                                                                                               | atent owner was not possible.                                                                                               |                                                                                                                                                        |  |  |  |

| 15. Correspondence Address: Direct all com                                                                                                                                                                                                                                                    | munication abo                                                                                                                                                                                                                                                                 | ut the reexamination to:                                                                                                    |                                                                                                                                                        |  |  |  |

| X The address associated with Customer N                                                                                                                                                                                                                                                      | umber: 22                                                                                                                                                                                                                                                                      | 2428                                                                                                                        |                                                                                                                                                        |  |  |  |

| Firm or                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                |                                                                                                                             |                                                                                                                                                        |  |  |  |

| Address                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                |                                                                                                                             | <u> </u>                                                                                                                                               |  |  |  |

| City                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                | State                                                                                                                       | Zip                                                                                                                                                    |  |  |  |

| Country                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                | <b>I</b> ,,,,,,,,,,,                                                                                                        |                                                                                                                                                        |  |  |  |

| Telephone                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                | Email                                                                                                                       | ·                                                                                                                                                      |  |  |  |

|                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                |                                                                                                                             |                                                                                                                                                        |  |  |  |

| b. Copending reexamination                                                                                                                                                                                                                                                                    | ation No<br>Control No<br>lo                                                                                                                                                                                                                                                   |                                                                                                                             | ·                                                                                                                                                      |  |  |  |

| a. Copending reissue Applic<br>b. Copending reexamination<br>c. Copending Interference N<br>x d. Copending litigation style                                                                                                                                                                   | ation No<br>Control No<br>lo<br>d:                                                                                                                                                                                                                                             |                                                                                                                             |                                                                                                                                                        |  |  |  |

| a. Copending reissue Applic     b. Copending reexamination     c. Copending Interference N     x d. Copending litigation styled     Technology Prope     Case No. 2:05-cv                                                                                                                     | ation No<br>Control No<br>lo<br>d:<br>rties Limi<br>-00494-TJW                                                                                                                                                                                                                 | ted, Inc. v. Fujitsu<br>, Feder <b>a</b> l District Co                                                                      | Limited et al.,                                                                                                                                        |  |  |  |

| a. Copending reissue Applic     b. Copending reexamination     c. Copending Interference N     x d. Copending litigation style     Technology Prope                                                                                                                                           | ation No.<br>Control No.<br>lo.<br>rties Limi<br>-00494-TJW<br>s, Marshal<br>ay become pu                                                                                                                                                                                      | ted, Inc. v. Fujitsu<br>, Federal District Co<br>1 Division<br>blic. Credit card information                                | Limited et al.,<br>ourt for the Eastern<br>should not be                                                                                               |  |  |  |

| a. Copending reissue Applic     b. Copending reexamination     c. Copending Interference N     x d. Copending litigation styled     Technology Prope     Case No. 2:05-cv-     District of Texa WARNING: Information on this form m                                                           | ation No.<br>Control No.<br>lo.<br>rties Limi<br>-00494-TJW<br>s, Marshal<br>ay become pu                                                                                                                                                                                      | ted, Inc. v. Fujitsu<br>, Federal District Co<br>1 Division<br>blic. Credit card information<br>n and authorization on PTO- | Limited et al.,<br>ourt for the Eastern<br>should not be<br>2038.                                                                                      |  |  |  |

| a. Copending reissue Applic     b. Copending reexamination     c. Copending Interference N     x d. Copending litigation styled     Technology Prope     Case No. 2:05-cv-     District of Texa WARNING: Information on this form m                                                           | ation No<br>Control No<br>d:<br>rties Limi<br>-00494-TJW<br>s, Marshal<br>ay become pu<br>ard informatio                                                                                                                                                                       | ted, Inc. v. Fujitsu<br>, Federal District Co<br>1 Division<br>blic. Credit card information                                | Limited et al.,<br>ourt for the Eastern<br>should not be<br>2038.                                                                                      |  |  |  |

| a. Copending reissue Applic<br>b. Copending reexamination<br>c. Copending Interference N<br>d. Copending litigation styled<br><u>Technology Prope</u><br><u>Case No. 2:05-cv</u><br><u>District of Texa</u><br>WARNING: Information on this form m<br>included on this form. Provide credit c | ation No<br>Control No<br>d:<br>rties Limi<br>-00494-TJW<br>s, Marshal<br>ay become pu<br>ard informatio                                                                                                                                                                       | ted, Inc. v. Fujitsu<br>, Federal District Co<br>1 Division<br>blic. Credit card information<br>n and authorization on PTO- | Limited et al.,<br>ourt for the Eastern<br>should not be<br>2038.                                                                                      |  |  |  |

I

## 71338 U.S. PTO

### 09/21/06IN THE UNITED STATES PATENT AND TRADEMARK OFFICE 338 U.S. PTO 90008237 Caption: In re Reexamination of Charles MOORE, et al.

Title: HIGH PERFORMANCE MICROPROCESSOR HAVING VARIABLE SPEED SYSTEM CLOCK

Pat. No.: 5,809,336

Issue Date: Sept. 15, 1998

Examiner: unassigned

Art Unit: unassigned

#### **REQUEST FOR EX PARTE REEXAMINATION UNDER 37 C.F.R. §1.510**

Mail Stop Ex Parte Reexamination Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Sir:

Enclosed please find a request for *ex parte* reexamination of U.S. Pat. No. 5,809,336 ("the '336 patent") under 35 U.S.C. § 302 and 37 C.F.R. § 1.510, together with the fee required under 37 C.F.R. § 1.20(c)(1). The request is filed on behalf of NEC Electronics America, Inc. A detailed presentation of the prior art in light of the claims is attached as Appendix A.

#### I. STATEMENT POINTING OUT EACH SUBSTANTIAL NEW QUESTION OF PATENTABILITY

The following Substantial New Questions of Patentability are presented and

summarized briefly below. These questions are presented in more detail in Appendix A.

**#**\

#### A. Are claims 1, 3, and 5-10 of U.S. Pat. No. 5,809,336 anticipated under 35 U.S.C. § 102(b) by or Obvious under 35 U.S.C. § 103(a) Over Ledzius, *et al.*, U.S. Pat. No. 4,691,124?

**8**2,

•

U.S. Pat. No. 4,691,124 to Ledzius, et al. (Exhibit 2) is prior art under 35 U.S.C.

§102 (b), and was not cited during the original prosecution of the of the '336 patent. The disclosure of Ledzius, *et al.* describes all elements of claims 1, 3 and 5-10 as described below. In particular, the Ledzius, *et al.* reference discloses a feature considered by the Applicants to be "<u>crucial</u>" to the patentability of the claims: a free-running ring oscillator on an integrated circuit substrate. *See* Exhibit 10, p. 5. No other prior art reference of record in the original prosecution describes this feature. The Requester thus believes that there is a substantial likelihood that a reasonable Examiner would have considered the teachings of the Ledzius, *et al.* reference to be important in deciding whether the claims of the '336 patent were patentable.

# B. Are claims 1-10 of U.S. Pat. No. 5,809,336 obvious under 35 U.S.C. § 103(a) over the Mead & Conway textbook in view of in view of IEEE Std 796-1983?

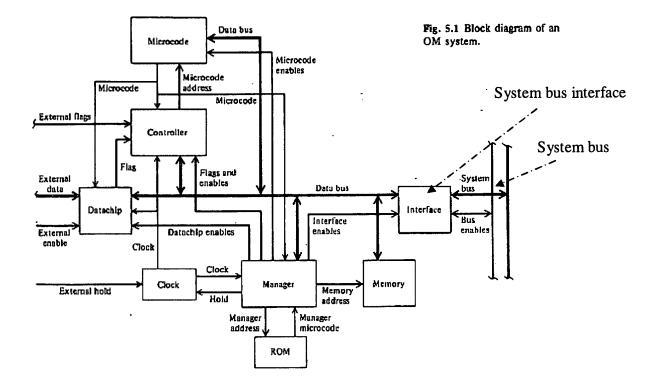

Like the Ledzius, et al. reference, the 1980 Mead & Conway textbook

"Introduction to VLSI Systems" (Exhibit 18) describes the use of free-running ring oscillators to clock microprocessors. Mead & Conway further describe the use of a microprocessor with a system bus and system bus interface. The IEEE Std. 796-1983 provides a standard system bus and system bus interface that were designed for use with multiple devices of different types, and which disclose the input / output elements of claims 1-10. Both references were published more than one year prior to the earliest possible benefit date of the '336 patent and are prior art under 35 U.S.C. § 102(b). Neither reference was cited to the office during original prosecution. Since no reference before the Examiner during original prosecution taught the use of a free-running ring oscillator as a system clock or the use of a system bus interface, Requester respectfully submits that there is a substantial likelihood that a reasonable Examiner would have considered

the teachings of the Mead & Conway textbook and the IEEE Std. 796-1983 reference to be important in deciding whether the claims of the '336 patent were patentable.

•

e)

# C. Are claims 1-10 of U.S. Pat. No. 5,809,336 obvious under 35 U.S.C. § 103(a) over Kato, U.S. Pat. No. 4,766,567 in view of Crosby, *et al.*, U.S. Pat. No. 4,750,111?

Like the Ledzius, *et al.* reference, U.S. Pat. No. 4,766,567 to Kato (Exhibit 4) describes a microprocessor circuit with a free-running on-chip ring oscillator. U.S. Patent No. 4,750,111 to Crosby, *et al.* describes a processor bus and externally clocked interface meeting all the input / output interface limitations of claims 1-10. The interface can be used with a wide variety of processors running at different speeds and external memory. Kato is prior art at least under 35 U.S.C. § 102(e), Crosby *et al.* is prior art under 35 U.S.C. § 102(b). Since no reference before the Examiner during original prosecution disclosed a free-running on-chip ring oscillator or a synchronous processor bus with external memory, Requester believes that there is a substantial likelihood that a reasonable Examiner would have considered the teachings of the Kato and Crosby, *et al.* references to be important in deciding whether the claims of the '336 patent were patentable.

## II. AN IDENTIFICATION OF EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED. Reexamination is requested for all claims 1-10.

#### III. MANNER OF APPLYING THE CITED PRIOR ART TO EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED.

Please see attached Appendix A, below, "Manner of Applying the Cited Prior Art to Every Claim for Which Reexamination is Requested."

#### IV. A COPY OF EVERY PATENT OR PRINTED PUBLICATION RELIED UPON OR REFERRED TO.

Every patent or printed publication relied upon or referred to is attached as

follows and is also cited on the attached modified Form PTO/SB/42:

EXHIBIT NO. REFERENCE

- EXHIBIT 1 Moore, *et al.*, U.S. Pat. No. 5,809,336.

- EXHIBIT 2 Ledzius, et. al, U.S. Pat. No. 4,691,124.

- EXHIBIT 3 Crosby, et al., U.S. Pat. No. 4,750,111.

- EXHIBIT 4 Kato, U.S. Pat. No. 4,766,567.

- EXHIBIT 5 TPL Web Site.

- EXHIBIT 6 Kronlage, U.S. Patent No. 4,079,338.

- EXHIBIT 7 Hotta, *et al.* U.S. Pat. No. 5,133,064.

- EXHIBIT 8 File History of the '336 Patent: Amendment of April 15, 1996.

- EXHIBIT 9 File History of the '336 Patent: Amendment of January 8, 1997.

- EXHIBIT 10 File History of the '336 Patent: Amendment of July 3, 1997.

- EXHIBIT 11 Magar, U.S. Pat. No. 4,503,500.

- EXHIBIT 12 Schaire, U.S. Pat. No. 4,453,229.

- EXHIBIT 13 Claim Chart Provided by Alleged Patent Owner in part Technology Properties, Ltd. Pursuant to Local Rules of the Federal District Court of the Eastern District of Texas.

- EXHIBIT 14 IEEE Std. 796-1983.

- EXHIBIT 15 Antonaccio, et al., U.S. Pat. No. 4,223,880.

- EXHIBIT 16 Brenig, U.S. Pat. No. 4,718,081.

- EXHIBIT 17 Y. Parker, Multi-Microprocessor Systems (1983), Chapter 1.

- EXHIBIT 18 Mead & Conway, Introduction to VLSI Systems (1980).

#### V. A COPY OF THE REEXAMINATION PATENT IN DOUBLE-COLUMN FORMAT

A copy of the reexamination patent in double column format is attached as

Exhibit 1.

۶.

é.

VI. CERTIFICATION THAT A COPY OF THE REQUEST FILED BY A PERSON OTHER THAN THE PATENT OWNER HAS BEEN SERVED IN ITS ENTIRETY ON THE PATENT OWNER AT THE ADDRESS AS PROVIDED FOR IN § 1.33(C).

I hereby certify that on September 21, 2006, I caused a complete copy of this

request for ex parte reexamination together with all exhibits and attachments to be served upon

the following party by First Class Mail as provided in 37 C.F.R. §1.248(a)(4):

Mr. Drew S. Hamilton Knobbe, Martens, Olson & Bear, LLP 550 W C St Ste 1200 San Diego, CA 92101

Date Sept. 21, 2006

Matthew A. Smith Registration No. 49,003

#### VII. NOTICE OF PENDING LITIGATION

Requester is aware that U.S. Pat. No. 5,809,336 is being asserted by Technology

Properties Limited, Inc. before the Federal District Court for the Eastern District of Texas in the

case styled:

•

Technology Properties Limited, Inc., v. Fujitsu Limited et al., Case No. 2:05-cv-00494-TJW, Federal District Court for the Eastern District of Texas, Marshall Division. The Commissioner is hereby authorized to charge any additional fees which may be required regarding this request under 37 C.F.R., or credit any overpayment, to Deposit Account No. 19-0741. Should no proper payment be enclosed herewith, as by a check or credit card payment form being in the wrong amount, unsigned, post-dated, otherwise improper or informal or even entirely missing, the Commissioner is authorized to charge the unpaid amount to Deposit Account No. 19-0741.

Respectfully submitted,

Date Scipt. 21. 2006

FOLEY & LARDNER LLP Customer Number: 22428 PATENT TRADEMARK OFFICE Telephone: (202) 295-4618 Facsimile: (202) 672-5399

9

**a** 1

By\_

Matthew A. Smith Registration No. 49,003

#### **APPENDIX A:**

4 9

#### MANNER OF APPLYING THE CITED PRIOR ART TO EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED

#### TABLE OF CONTENTS

÷

| I.   | Introduction.  |                                                                              | 4  |

|------|----------------|------------------------------------------------------------------------------|----|

| II.  | Technology A   | At Issue And Field of the Invention                                          | 4  |

| III. | Patent Owner   | 's Claim Interpretations                                                     | 17 |

| IV.  | Claims 1-10    | are Invalid Under 35 U.S.C. § 102(b) or 35 U.S.C. § 103(a) over              |    |

|      | Ledzius, et al | 1                                                                            | 18 |

|      | 1.             | Claim 1                                                                      | 18 |

|      | 2.             | Claim 2                                                                      | 24 |

|      | 3.             | Claim 3                                                                      | 25 |

|      | 4.             | Claim 4                                                                      | 26 |

|      | 5.             | Claim 5                                                                      | 26 |

|      | 6.             | Claim 6                                                                      | 27 |

|      | 7.             | Claim 7                                                                      | 30 |

|      | 8.             | Claim 8                                                                      | 30 |

|      | 9.             | Claim 9                                                                      | 31 |

|      | 10.            | Claim 10                                                                     | 31 |

| V.   | Claims 1-10    | are Invalid Under 35 U.S.C. § 103(a) over Mead & Conway in View              |    |

| ۰.   |                | 796-1983                                                                     | 32 |

|      | 1.             | Claim 1                                                                      |    |

|      | 2.             | Claim 3                                                                      |    |

|      | 2.<br>3.       | Claim 4                                                                      |    |

|      | <i>4</i> .     | Claim 5                                                                      |    |

|      | 5.             | Claim 6                                                                      |    |

|      | 5.<br>6.       | Claim 7                                                                      |    |

|      | 7.             | Claim 8                                                                      |    |

|      | 8.             | Claim 9                                                                      |    |

|      | 9.             | Claim 10                                                                     |    |

|      |                |                                                                              |    |

| VI.  |                | of U.S. Pat. No. 5,809,336 are Invalid Under 35 U.S.C. § 103(a) over         | 10 |

|      |                | at. No. 4,766,567 in view of Crosby, <i>et al.</i> , U.S. Pat. No. 4,750,111 |    |

|      | 1.             | Claim 1                                                                      |    |

|      | 2.             | Claim 2                                                                      |    |

|      | 3.             | Claim 3                                                                      |    |

|      | 4.             | Claim 4                                                                      |    |

|      | 5.             | Claim 5                                                                      |    |

|      | 6.             | Claim 6                                                                      |    |

|      | 7.             | Claim 7                                                                      |    |

|      | 8.             | Claim 8                                                                      |    |

|      | 9.             | Claim 9                                                                      |    |

|      | 10.            | Claim 10                                                                     | 52 |

| VII. | Conclusions | 54 |

|------|-------------|----|

|------|-------------|----|

• •

#### I. INTRODUCTION

÷

Technology Properties Limited, Inc. ("TPL"), a self-styled "purpose-built boutique that specializes in the development, commercialization and management of IP assets," (Exhibit 5), has sued several major suppliers of microprocessors for infringement of U.S. Pat. No. 5,809,336 ("the '336 patent") before the Federal District Court for the Eastern District of Texas. TPL appears to believe that any computer sold today requires a license under the '336 patent. On its Web site, for example, TPL states "[u]se of US '336 is prevalent across most microprocessors from low speed microcontrollers to sophisticated systems on chips....Virtually every product manufactured today utilizing microprocessors or embedded processors will require an MMP Portfolio license."

The dense thicket of highly relevant, unexamined prior art that predates the '336 patent, however, belies TPL's views. As the Requester will show, at the time of the earliest possible benefit date of the '336 patent (1989), every technique claimed by the '336 patent, although ultimately not commercially successful, had already become part of the prior art. For these reasons, Requester respectfully submits that all claims of the '336 patent should be reexamined and found unpatentable in light of the newly cited prior art.

#### II. TECHNOLOGY AT ISSUE AND FIELD OF THE INVENTION

The '336 patent deals, broadly speaking, with methods for clocking microprocessors. In many commercially available microprocessors, a clock is required to help control the operation of the microprocessor and to help synchronize events between different components of the microprocessor system. Using a clock, the components of the microprocessor

system can be synchronized, so that communications between components can take place

efficiently.

Claim 1 of the '336 patent is reproduced here for the Examiner's reference:

1. A microprocessor system, comprising a single integrated circuit including a central processing unit and an entire ring oscillator variable speed system clock in said single integrated circuit and connected to said central processing unit for clocking said central processing unit,

said central processing unit and said ring oscillator variable speed system clock each including a plurality of electronic devices correspondingly constructed of the same process technology with corresponding manufacturing variations, a processing frequency capability of said central processing unit and a speed of said ring oscillator variable speed system clock varying together due to said manufacturing variations and due to at least operating voltage and temperature of said single integrated circuit;

an on-chip input/output interface connected to exchange coupling control signals, addresses and data with said central processing unit; and a second clock independent of said ring oscillator variable speed system clock connected to said input/output interface.

The first body limitation claims "an entire ring oscillator variable speed system

clock...for clocking said central processing unit". The figure on the face of the '336 patent

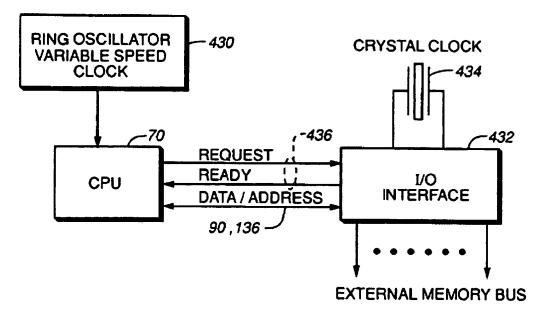

shows a relevant configuration:

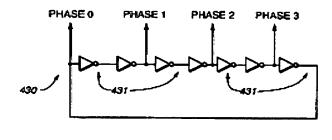

A ring oscillator as recited in claim 1 (and shown in the Figure above as reference symbol 430) can be defined as an odd number of inverting elements connected in a loop. Each inverter operates after a small delay to produce an output that is the inverse of its input. Figure 18 of the '336 patent shows a typical ring oscillator, which has seven inverters connected serially in a ring form:

FIG.\_18

Since the number of inverting elements is odd, the system is unstable, and the output of any one inverter will change roughly as fast as the series of the remaining inverters can switch. For example, if the first node (phase 0) in Fig. 18 is at low voltage (LO), the output of the first inverter will be high voltage (HI). The output of the following inverters, working from left to right will be

Inverter 2 output (phase 1)LOInverter 3 outputHIInverter 4 output (phase 2)LOInverter 5 outputHIInverter 6 output (phase 3)LOInverter 7 output (phase 0)HI

The output of the seventh inverter is connected to the input of the first inverter (phase 0), which began at LO. Since the output of the seventh inverter is HI, this changes all of the values in the above table to their opposites. In this manner, the input voltage to the first

inverter (and indeed all of the inverters) changes as fast as the other inverters in the ring can switch. Using these principles, a number of ring oscillator configurations can be produced, some of which are shown in the 1980 Mead & Conway undergraduate textbook entitled "*Introduction to VLSI Systems*" (Exhibit 18, p. 234-35).

According to the '336 patent, since a ring oscillator is constructed from semiconductor elements, its frequency may vary over a wide range with ambient and manufacturing conditions. This is in contrast to crystal-based oscillators and conventional frequency-controlled ring oscillators, which vary their oscillation frequencies within a more limited range. The '336 patent microprocessor design calls for allowing the ring oscillator to run freely, in the hope that it will vary in the same way as the speed of other semiconductor components in the microprocessor with changes temperature and other conditions.

The purported advantage of this may be considered as follows: suppose the CPU changes the speed at which it can carry out operations like addition and multiplication with changes in temperature and other conditions. If the maximum (error-free) CPU speed becomes lower, but the clock speed remains the same, there is some risk that the maximum CPU speed will dip below the clock speed. To take this into account, designers can use a "safe" clock speed—one significantly lower than the maximum CPU speed under normal conditions. The '336 patent, however, claims to solve the problem in a different way: by placing the clock resonator on the same integrated circuit as the CPU, and allowing the resonator to run freely, without constraint. According to the '336 patent, this allows the clock to be designed to run faster, because it will automatically scale back its speed if the CPU slows down:

The ring oscillator 430 is useful as a system clock, with its stages 431 producing phase 0-phase 3 outputs 433 shown in FIG. 19,

because its performance tracks the parameters which similarly affect all other transistors on the same silicon die. By deriving system timing from the ring oscillator 430, <u>CPU 70 will always</u> <u>execute at the maximum frequency possible, but never too fast</u>. [Col. 16, l. 63 – col. 17, l. 2] (emphasis added).

The '336 patent describes that the ring oscillator varies over a wide range of

#### frequencies:

.

.

The CPU 70 executes at the fastest speed possible using the adaptive ring counter clock 430. Speed may vary by a factor of four depending upon temperature, voltage, and process. [Col. 17, ll. 19-22]

The Applicants considered this feature central to their invention, and represented

this to the Office several times during original prosecution. For example, in their Amendment of

April 15, 1996, the Applicants stated:

Applicants note that the present invention is directed to a microprocessor system including a central processing unit and a ring oscillator variable speed system clock connected thereto. In accordance with the claimed invention, the central processing unit and the ring oscillator variable speed system clock are provided in a single integrated circuit. This allows for example the central processing unit to track variations in the speed of the ring oscillator variable speed system clock are disposed in the same integrated circuit. [Exhibit 8, p. 6] (emphasis added).

In their Amendment of January 8, 1997, Applicants stated:

In the interview, the fact that <u>operating characteristics of electronic</u> <u>devices in an integrated circuit will track one another depending on</u> <u>variations in the manufacturing process</u> used to make the integrated circuit was discussed. <u>This allows the microprocessor to</u> <u>operate at its fastest safe operating speed</u>, given its manufacturing process or changes in its operating temperature or voltage. In contrast, prior art microprocessor systems are given a rated speed based on possible worst case operating conditions and an external clock is used to drive them no faster than the rated speed. [Exhibit 9, pp. 3-4] (emphasis added).

In their Amendment of July 3, 1997, the Applicants assured the Examiner:

<u>Crucial</u> to the present invention is that since both the oscillator or variable speed clock and driven device are on the same substrate, when the fabrication and environmental parameters vary, the oscillation or clock frequency and the frequency capability of the driven device will automatically vary together. This differs from all <u>cited</u> references in that the oscillator or variable speed clock and the driven device are on the same substrate.... [Exhibit 10, p. 5] (emphasis added).

The Office was not able to rebut such statements during original prosecution,

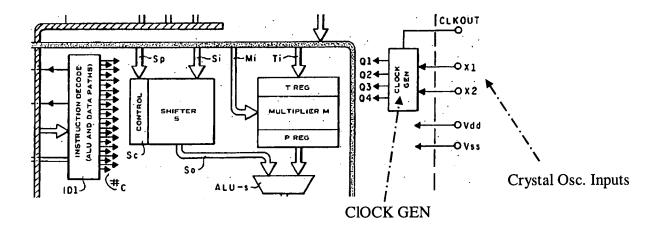

which were true only in the limited vacuum of the "cited prior art". The reference before the Examiner that most closely approximated the "on-chip ring oscillator" or "variable speed system clock" was the Magar patent, (U.S. Pat. No. 4,503,500, Exhibit 11). The Magar patent described an off-chip crystal oscillator, with on-chip clock generation circuitry. The pertinent portions of Fig. 2A from the Magar patent are shown below, with dashed arrows added by the Requester to indicate particular features:

Magar shows "CLOCK GEN" circuitry on the right-hand side of Fig. 2A that is on a single substrate with the CPU. The CLOCK GEN circuitry, however, has crystal oscillator inputs X1 and X2. This leads to the supposition that CLOCK GEN is not a resonator itself, but

rather circuitry that amplifies, filters or otherwise prepares the crystal resonator output for use as

a CPU clock. Since the crystal resonator of Magar was off-chip, the Applicants were able to

assert:

٠

.

one of ordinary skill in the art should readily recognize the speed of the CPU and the clock *do not* vary together due to manufacturing variation, operating voltage and temperature of the IC in the Magar microprocessor, as taught in the above quotation from the reference. This is simply because the Magar microprocessor clock is frequency-controlled by a crystal which is also external to the microprocessor. Crystals are by design fixedfrequency devices whose oscillation speed is designed to be tightly controlled and to vary minimally due to variations in manufacturing, operating voltage and temperature. The Magar microprocessor in no way contemplates the variable speed clock as claimed. (emphasis in original) [Amendment of July 3, 1997, Exhibit 10, p. 3-4]

If the Office had had access to the best prior art, it could have quickly met this

argument with a better rejection. In fact, by 1980, the use of on-chip ring oscillators to clock

integrated circuits was undergraduate textbook knowledge, appearing in Mead & Conway

(Exhibit 18). In Chapter 7, the Mead & Conway textbook discusses integrated circuit clocks,

stating that they are most easily constructed using on-chip ring oscillators, and that the frequency

of the ring oscillators will vary with ambient conditions and process technology:

Process variation in integrated circuit fabrication does not allow accurate resonant networks to be fabricated by usual means, but it is perfectly feasible, indeed essential for self-contained VLSI systems, to generate clock signals <u>on the chip</u>....[T]he role of the clock in a synchronous system is to connect sequence and time....A *model* of the temporal behavior of the systems being clocked is built into the clock generator or in the choice of times for the various timers. The easiest way to build these timers is as <u>chains of inverters</u>. The propagation <u>delay</u> time of such a chain will of course <u>vary with  $\tau$ </u>, according to the way in which the <u>fabrication process</u>, aging, temperature and power voltage affect  $\tau$ . However, these variations only make the inverter chain a better model of the system being clocked than a fixed timer would be....Clocks that employ these delays as timers are all elaborations of the *ring oscillator*. [Exibit 25, p. 233-35](italics in original, underlining added).

Numerous other examples are found in the art prior to 1989. One example of the use of a frequency-controlled ring oscillator is provided in U.S. Pat. No. 4,079,338 to Kronlage (Exhibit 6). The Kronlage patent issued in 1978, more than ten years before the earliest possible filing date of the applications leading to the '336 patent. Kronlage describes the use of an <u>on-</u>chip ring oscillator. For example, the Abstract provides:

[a] novel ring oscillator circuit includes means by which the repetition rate is adjustable...The ring oscillator may be fabricated on a single substrate along with other  $I^2L$  circuitry and be utilized as the clock source therefore. [Abstract]

As a third example, Ledzius, et al., U.S. Pat. No. 4,691,124, shows a ring

oscillator used to drive a processor at its maximum possible speed (Exhibit 2; Figs. 1-2; RN 18,

58). The description states:

5

[s]ince both clock generator 18 and functional circuit 16 <u>are</u> <u>constructed on substrate 14, clock generator 18 compensates for</u> <u>temperature and process caused variations in the true maximum</u> <u>speed of functional circuit 16. The frequency of the clock signal</u> <u>produced by clock generator 18 varies to reflect process and</u> <u>temperature variances</u>. Accordingly, process caused variations are compensated because clock generator 18 is always physically made from the same batch and section of a semiconductor wafer as functional circuit 16. Slowest signal path 38 of functional circuit 16 controls the true maximum speed. Accordingly, process variations which affect slowest signal path 38 also affect clock generator 18. [Exhibit 2; col. 4, lines 5-14] (emphasis added).

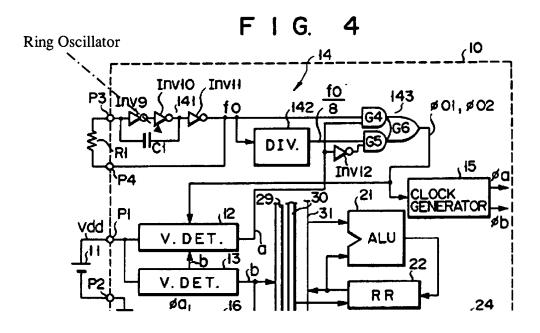

Yet another example may be found in Kato, U.S. Pat. No. 4,766,567, which deals

with a single chip microprocessor, states "first clock generating section 141 may be replaced by a

ring oscillator of the known type or a CR clock oscillator similar which is completely built on

semiconductor substrate 10. When a ring oscillator is used, its output frequency lowers in

proportion to the speed of the data processing circuit which is lowered due to the drop of power supply voltage. Therefore, the above-mentioned advantages will be more prominent." [Exhibit 4; Fig. 4, RN 141, Col. 10, l. 67 – Col. 11, l. 7] (emphasis added).

ъ.

P

Since the Office had not been provided with the art describing a "crucial" limitation of the claims, its later discovery is respectfully submitted to raise a substantial new question of patentability.

The '336 patent also mentions, although not in sufficient detail to satisfy the requirements of 35 U.S.C. § 112, a communications interface for the processor. For example, claim 19 (patent claim 1) was amended to recite:

an on-chip input/output interface connected to exchange coupling control signals, addresses and data with said central processing unit; and a second clock, independent of said first ring oscillator variable speed system clock connected to said input/output interface.

Since the ring oscillator varies its output over a wide range of frequencies, the question arises as to how the processor can communicate with other devices off of the integrated circuit, which have no information about the ring oscillator's speed. Does the processor force the outside world to run at the speed of the ring oscillator? If one credits the specification of the '336 patent, this solution would be of limited practical use, since other devices would not vary in their processing frequency capabilities in the same way as the ring oscillator would vary its speed.

More likely, the processor employs an "asynchronous" interface that allows the processor, which has a wide range of speeds due to the ring oscillator, to interact with other

devices that may have more fixed operation frequencies. The '336 patent tangentially states this idea as follows:

...

.

The CPU 70 executes at the fastest speed possible using the adaptive ring counter clock 430. Speed may vary by a factor of four depending upon temperature, voltage, and process. The external world must be synchronized to the microprocessor 50 for operations such as video display updating and disc drive reading and writing. This synchronization is performed by the I/O interface 432, speed of which is controlled by a conventional crystal clock 434. [Exhibit 1, Col. 17, Il. 19-27]

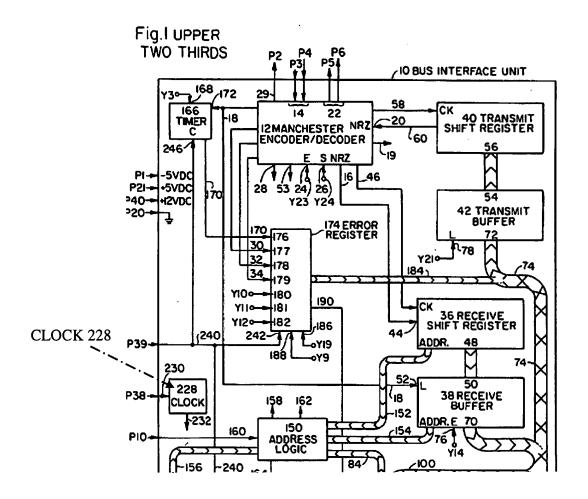

During original prosecution, the Examiner apparently considered the most

relevant art regarding these final limitations to be the Schaire reference, U.S. Pat. No. 4,453,229 (Exhibit 12). As noted by Examiner Eng in the Office Action of December 12, 1995, Schaire shows an input/output interface with a clock 228. Figure 1 from Schaire is partially reproduced here, with a dashed arrow added to point out the clock 228:

1

In response to the Examiner's rejections of claim 20 over Schaire in combination with Sheets, Applicants stated that "Schaire provides no indication that bus interface unit 10 is clocked by a signal from a clock different from that used to clock the host microprocessor."

Again, however, the best art was not before the Examiner. In fact asynchronous interfacing between systems with different clock speeds had been known for years in the art. The 1980 undergraduate text Mead & Conway, for example, described the principle nearly ten years before the filing of the first Moore, *et al.* application as follows:

> A system such as a microprocessor may be entirely synchronous internally but cannot extend this synchrony indefinitely to encompass all of the external world with which it may interact. If asynchronous signals of external origin are allowed to enter a synchronous system as ordinary inputs, the timing constraints

required to assure correct operation cannot be satisfied, since there is no known relationship between the timing of the asynchronous inputs and the clock....So, a slightly smarter thing to do is to ensure that only one clocked storage element is affected by a given asynchronous input. A clocked storage element that is used this way is called a synchronizer, since it is intended to produce an output signal that is in synchrony with the clock. [Exhibit 18, pp. 237-38.

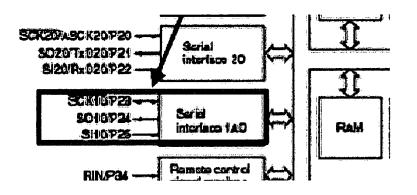

Hotta, et al., U.S. Pat. No. 5,133,064 (Exhibit 7, filed April 28, 1988), is also

indicative of the state of the art with regard to asynchronous interfaces in the relevant time

period. For example, in the Background of the Invention section of Hotta et al., prior art work on

asynchronous interfaces is described. Figure 3 of the Hotta, et al. reference is shown below:

٩.

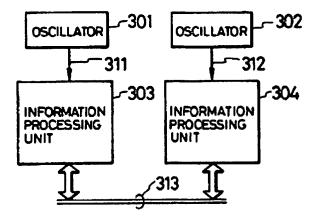

Each processor operates with a separate, independent oscillator. See Hotta, et al.,

col. 2, ll. 1-3. As noted in Hotta, *et al.*, this necessitates the use of well-known asynchronous interfaces available in the art prior to 1989:

The arrangement of the second prior art approach [Fig. 3] is <u>often</u> <u>found in microprocessor systems</u> or the like. Each information processing unit corresponds to an LSI chip. The first problem of this prior art approach is that, since the two information processing units are controlled by two different clock signals, the information processing units must be interfaced asynchronously. [Col. 2, ll. 3-15].

Numerous other asynchronous interfaces and synchronous interfaces with dual clock schemes had been known for years prior to the filing of the application leading to the '336 patent. For example, Ledzius, *et al.*, U.S. Pat. No. 4,691,124, shows an on-chip ring oscillator used to drive the microprocessor at its maximum theoretical processing speed, coupled to an on-chip input/output interface connected to a processor bus driven by an external clock. *See* Exhibit 2, col. 3, l. 67 – col. 4, l. 2.

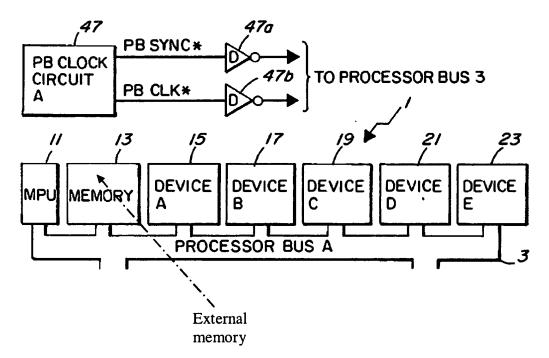

Another example is provided by U.S. Pat. No. 4,750,111 to Crosby, *et al.* (Exhibit 3), which describes a multi-processor BOSS bus. The BOSS bus is a synchronous bus for use with multiple processors having different clock speeds. *See* col. 8, 1. 59 – col. 9, 1. 1; col. 5, ll. 45-52; col. 5, 1. 64 – col. 6, 1. 7. The processor bus has an interface (Fig. 5, col. 4, ll. 19-21) to each processor on the system for exchanging data, address and control signals. *See* claim 1, element (e); col. 2, ll. 52-58; col. 10, ll. 10-42. The processor bus runs at a clock rate independent of each processor that is fed to each processor bus interface. *See* col. 13, ll. 22-27; col. 9, ll. 19-26; col. 7, ll. 37-49; col. 10, ll. 26-42; Fig. 5 (inputs PBCLK and PBSYNC); col. 9, ll. 3-6.

Similarly, IEEE Std. 796-1983 (Exhibit 14) describes a standardized processor/memory bus based on the Intel Microbus® that is designed to "[allow] modules of different speeds to be interfaced by way of the bus." *See* p. 9. The bus can be operated in multimaster mode. *See id.* Each master has a CPU which sends "command signals, address signals, and memory or I/O addresses" through the "bus exchange logic" to the system bus. *See* p. 11, §2.1.1. The 796 Bus Specification calls for two clock lines. The first clock line BCLK\* is used to synchronize bus contention logic and can be generated by only one master at a time,

meaning that the bus contention logic, part of the bus interface on other masters on the system are necessarily operating with an external clock. *See* p.12, §2.1.3.1.1. There is also a CCLK\*, which is a fixed frequency clock generated by one of the master systems and supplied to all other masters. *See* p.12, §2.1.3.1.1.

As a further example, U.S. Pat. No. 4,223,880 to Antonaccio, *et al.* (Exhibit 15), describes a multiprocessor system bus. Each processor has an interface unit which exchanges "data, address and control information" with a CPU by way of an intraprocessor bus. *See* col. 2, 11. 5-15; Fig. 2. The bus operates according to a bus sync clock signal that is a derivative of the master system clock signal and which is fed into each bus interface module. *See* col. 5, 11. 17-40.

Requester thus makes this request based on the simple belief that a reasonable Examiner, presented with the most relevant prior art describing the features claimed to be patentable by the applicants, would not have allowed the claims in their present form. A detailed application of the prior art cited in the request, not before the Office during original prosecution, is described below.

#### III. PATENT OWNER'S CLAIM INTERPRETATIONS

The purported patent owner (in part) TPL has taken the position that the claims of '336 patent cover all microprocessors, including those that do not use variable speed clocks. The Requester, of course, opposes the claim interpretations proposed by TPL. Requester further recognizes that the Examiner is required to examine the claims under their broadest reasonable construction, whereas the construction given by a court may be considerably narrower. *See In re Yamamoto*, 740 F.2d. 1569, 1571 (Fed. Cir. 1984). TPL's constructions will be presented where

pertinent in this request, however, as an aide to the Examiner in understanding the how the claims are being understood and asserted by the patent owner.

#### IV. CLAIMS 1-10 ARE INVALID UNDER 35 U.S.C. § 102(B) OR 35 U.S.C. § 103(A) OVER LEDZIUS, *ET AL*.

U.S. Pat. No. 4,691,124 to Ledzius et al. ('124 patent) is entitled "[s]elf-

compensating, maximum speed integrated circuit". The circuit employs an on-chip ring oscillator with input/output ports clocked by a second clock. The '124 patent discloses each element of all claims expressly or inherently, except as noted below. The Ledzius, *et al.* patent issued on September 1, 1987 and is prior art under 35 U.S.C. § 102(b).

1. Claim 1

• •

•

# (a) A microprocessor system, comprising a single integrated circuit including a central processing unit

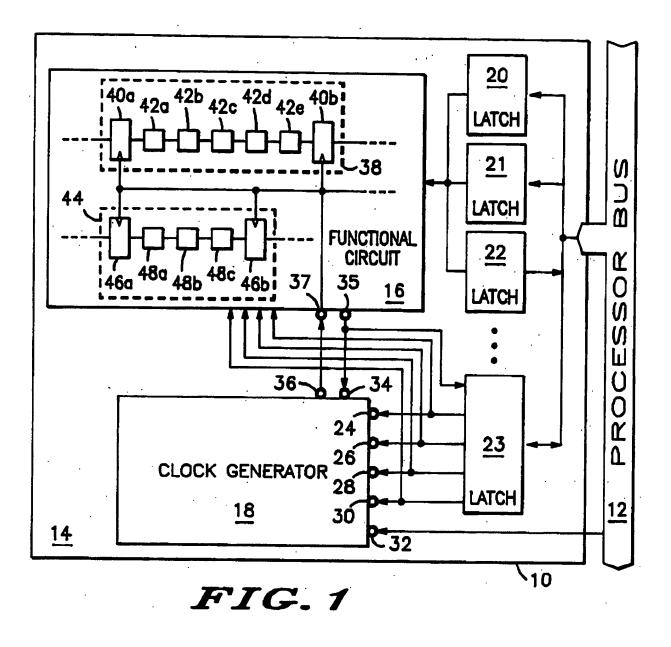

The '124 patent discloses a microprocessor system comprising an integrated

circuit. For example, the specification refers to an integrated circuit (IC) attached to a processor bus:

Referring to FIG. 1, an integrated circuit (IC) 10 couples to a processor bus 12. Processor bus 12 includes conventional address, data, and control lines as may be required for a processor (not shown) to successfully communicate with IC 10. A functional circuit 16, a clock generator 18, and interface devices, such as latches 20, 21, 22, and 23 reside on a substrate 14 within IC 10." [Col. 2, ll. 24-32.]

The IC 10 is disclosed as having, among other things, a digital signal processing

function. *See* col. 2, lines 43-45. One skilled in the art would immediately recognize that a circuitry for performing a digital signal processing function would include a CPU. As of 1989, a digital signal processor was conventionally implemented as a programmable microprocessor with a central processing unit. *See, e.g.*, Exhibit 16, U.S. Pat. No. 4,718,081, issued January 5,

1988, at col. 5, ll. 64-67 ("[c]ell site controller 26 may be any conventional digital signal processor, and preferably includes a central processing unit.").

(b) and an entire ring oscillator variable speed system clock in said single integrated circuit and connected to said central processing unit for clocking said central processing unit,

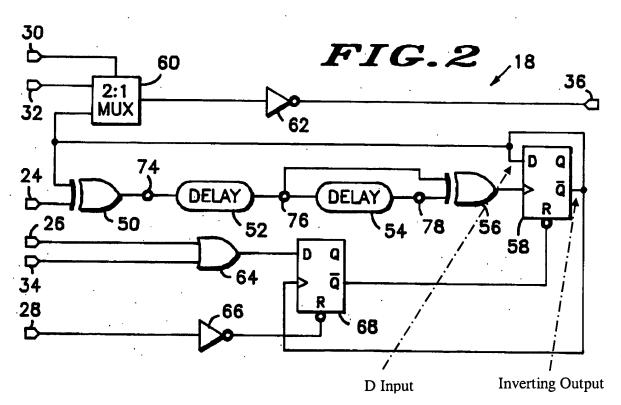

The '124 patent further discloses an entire ring oscillator variable speed system clock in said single integrated circuit. For example, Fig. 2 shows clock generator 18, which is part of the integrated circuit as shown in Fig. 1. Clock generator 18 has a D-Flip Flop connected in ring form, as indicated by the dashed arrows below, which have been added to Fig. 2:

The non-clock input to the D flip flop is connected to the inverting output. This arrangement is nothing more than an odd number (one) of inverting elements connected in a ring, *i.e.* a ring oscillator. Ring oscillators with similar delay schemes are shown in the 1980 Mead & Conway textbook. *See* Exhibit 18, page 235. The elements 50, 52, 54 and 56 are delays and

exclusive-OR gates used to generate a pulse of width corresponding to delay 54 to activate the D

flip-flop every time the inverting output Q' signal changes. This results in a clock signal which

is routed to clock output 36, and used to clock the central processing unit:

.

Clock generator 18 contains a clock output node 36 which couples to clock input node 37 of functional circuit 16 and a process complete input node 34 which couples to process complete output node 35 of functional circuit 16. Additionally, clock generator 18 contains an external clock node 32 that couples to processor bus 12." [col. 3, 1. 64-col. 4, 1. 2].

(c) said central processing unit and said ring oscillator variable speed system clock each including a plurality of electronic devices correspondingly constructed of the same process technology with corresponding manufacturing variations, a processing frequency capability of said central processing unit and a speed of said ring oscillator variable speed system clock varying together due to said manufacturing variations and due to at least operating voltage and temperature of said single integrated circuit;

The '124 patent discloses that the ring oscillator and CPU are manufactured with

the same process technology, and thus vary together in speed:

Since both clock generator 18 and functional circuit 16 are constructed on substrate 14, clock generator 18 compensates for temperature and process caused variations in the true maximum speed of functional circuit 16. The frequency of the clock signal produced by clock generator 18 varies to reflect process and temperature variances. Accordingly, process caused variations are compensated because clock generator 18 is always physically made from the same batch and section of a semiconductor wafer as functional circuit 16. Slowest signal path 38 of functional circuit 16 controls the true maximum speed. Accordingly, process variations which affect slowest signal path 38 also affect clock generator 18. [Col. 4, lines 5-14.]

Furthermore, as disclosed in the summary of the invention:

Accordingly, it is an object of the present invention to provide an improved integrated circuit (IC) which successfully operates at its true maximum speed. Another object of the present invention concerns providing an improved IC that is self-compensated so that IC speed changes with temperature and process variations to insure operation at the IC's true maximum speed. [Col. 1, ll. 45-52].

(d) an on-chip input/output interface connected to exchange coupling control signals, addresses and data with said central processing unit;

Fig. 1 of the '124 patent, shown below, indicates that the CPU and processor bus

are connected by an on-chip<sup>1</sup> input/output interface comprising a number of latches 20-23 and

control registers that exchange coupling control signals, addresses and data:

Latches 20-22 represent conventional devices which pass data between functional circuit 16 and processor bus 12. As shown in FIG. 1, latches 20 and 21 represent input ports in which the processor writes data for use by functional circuit 16. Latch 22 represents an output port in which functional circuit 16 stores data so that the processor may read the data. No limit is placed on the number of data latches utilized by the present invention. Rather, the particular requirements of functional circuit 16 for each application control the number of data input and output latches." col. 3, lines 32-42.

<sup>&</sup>lt;sup>1</sup> See Col. 2, ll. 29-32: "A functional circuit 16, a clock generator 18, and interface devices, such as latches 20, 21, 22, and 23 reside on a substrate 14 within IC 10."

The '124 patent, much like the '336 patent, deals with the problems of interprocessor communications. The typical communication arrangement described in the '124 patent involves processor 16 communicating over an input/output interface comprised of latches 20-23 with another processor on the processor bus 12. The input/output interface is required for processor 16, which operates asynchronously (at a different clock speed) to the processor bus, to communicate with another processor on the bus 12. *See, e.g.*, Abstract, ll. 3-5 ("The integrated

circuit operates asynchronously from a processor bus and contains circuitry for interfacing with the processor bus"); col. 1, ll. 57-59 ("another object of the present invention concerns providing an improved IC which operates asynchronously with other devices.").

Coupling with the processor bus 12 requires the exchange of addresses, data and control signals between the processor 16 and the input/output interface. *See, e.g.*, col. 2, ll. 26-29 ("Processor bus 12 includes conventional address, data and control lines as may be required for a processor (not shown) to successfully communicate with IC 10."). A person of ordinary skill in the art in 1989 would have immediately recognized that the processor 16 exchanges coupling control signals, data and addresses with the input/output interface, comprising at least input/output latches 20-23.

As one specific example of control signals, the '124 patent discloses that latch 23 that exchanges control signals that allow a processor on the processor bus to control the clock generator 18 and obtain information about when data from a particular process is available:

Latch 23 represents a status/control interface between clock generator 18 and functional circuit 16 on one side and processor bus 12 on the other. Accordingly, outputs from latch 23 connect to a run node 24, a stop node 26, reset node 28, and a clock select node 30 of clock generator 18 as well as to inputs of functional circuit 16. Corresponding inputs of latch 23 couple to processor bus 12. Additionally, the process complete node 35 of functional circuit 16 connects to an input node of latch 23 with a corresponding output node coupled to processor bus 12. The processor writes bits of data to latch 23 to control operation of clock generator 18 and functional circuit 16. The processor reads bits of data from latch 23 to monitor the status of operations within functional circuit 16. Latch 23 is not limited to the particular number and description of signals described above but may accommodate any number of signals required by a particular application. For example, other signals may couple to processor bus 12 through latch 23 to communicate information about error conditions. [Col. 3, ll. 43-63].

One of the coupling control signals exchanged between the processor 16 and the input/output interface is the "process complete" signal 35. *See, e.g.*, col. 3, ll. 25-30. This signal informs other processors on the processor bus 12 that data is available to be read from the input/output interface, and is thus a form of handshaking signal.

## (e) and a second clock independent of said ring oscillator variable speed system clock connected to said input/output interface.

The '124 patent discloses that a second clock (shown in Fig. 1 as signal trace 32) is found on the processor bus and connected to the input/output interface comprising latches 20-23. *See, e.g.*, col. 3, l. 67 – col. 4, l. 2 ("Additionally, clock generator 18 contains an external clock node 32 that couples to processor bus 12.").

As shown in Fig. 1, the external clock is both on processor bus 12 and applied to an input of clock generator 18. The processor bus 12 is connected to the input/output interface latches 20-23. The processor bus clock is also used to clock input / output latches 20-23 when the clock generator 18 is disabled in favor of the external clock, since it is then the only available clock. *See* Col. 6, ll. 11-16.

2. *Claim* 2

The microprocessor system of claim 1 in which said second clock is a fixed frequency clock.

The '124 patent describes that the clock 32 may be a "synchronous clock". See col. 6, ll. 14-16. In the prior art, a synchronous bus clock is almost always a fixed-frequency clock driven by a frequency-stable resonator. For example, Crosby, *et al.*, U.S. Pat. No. 4,750,111, describe the use of a synchronous processor bus having an asynchronous interface. The processor bus is clocked with a signal operating at a constant speed of 10 MHz (col. 19, ll. 44-45). This signal is used to clock each processor device interface. *See* '111 patent, col. 13, ll. 22-27; col. 9, ll. 19-26; col. 7, ll. 37-49; col. 10, ll. 26-42; Fig. 5 (inputs PBCLK and PBSYNC); col. 9, ll. 3-6. Thus, it would have been obvious to choose a fixed-frequency clock source based on the teaching of a processor bus with a synchronous clock in Ledzius *et al.*