## UNITED STATES PATENT AND TRADEMARK OFFICE

UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| PPLICATION NO.                                    | FILIN     | G DATE     | FIRST NAMED INVENTOR | ATTORNEY DOCKET NO. | CONFIRMATION N |

|---------------------------------------------------|-----------|------------|----------------------|---------------------|----------------|

| 90/008,474                                        | 01/3      | 00/2007    | 5809336              | •                   | 2845           |

| 40972                                             | 7590      | 04/05/2007 |                      | EXAM                | IINER          |

| HENNEMAN & ASSOCIATES, PLC 714 W. MICHIGAN AVENUE |           |            |                      |                     |                |

|                                                   | ERS, MI 4 |            |                      | ART UNIT            | PAPER NUMBER   |

DATE MAILED: 04/05/2007

Please find below and/or attached an Office communication concerning this application or proceeding.

Commissioner for Patents United States Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450 www.uspro.gov

### DO NOT USE IN PALM PRINTER

(THIRD PARTY REQUESTER'S CORRESPONDENCE ADDRESS)

Daniel B. Ravicher Public Patent Foundation 1375 Broadway, Suite 600 New York, NY 10018

### **EX PARTE REEXAMINATION COMMUNICATION TRANSMITTAL FORM**

REEXAMINATION CONTROL NO. 90/008,474.

PATENT NO. <u>5809336</u>.

ART UNIT <u>3992</u>.

Enclosed is a copy of the latest communication from the United States Patent and Trademark Office in the above identified *ex parte* reexamination proceeding (37 CFR 1.550(f)).

Where this copy is supplied after the reply by requester, 37 CFR 1.535, or the time for filing a reply has passed, no submission on behalf of the *ex parte* reexamination requester will be acknowledged or considered (37 CFR 1.550(a)).

### Control No. Pat nt Under Reexamination 90/008,474 5809336 Order Granting / D nying R qu st F r Examiner **Art Unit** Ex Parte R examination Joseph R. Pokrzywa 3992 -- The MAILING DATE of this communication appears on the cover sheet with the correspondence address--The request for ex parte reexamination filed 30 January 2007 has been considered and a determination has been made. An identification of the claims, the references relied upon, and the rationale supporting the determination are attached. Attachments: a) PTO-892, b) ☐ PTO/SB/08, c) ☐ Other: The request for ex parte reexamination is GRANTED. RESPONSE TIMES ARE SET AS FOLLOWS: For Patent Owner's Statement (Optional): TWO MONTHS from the mailing date of this communication (37 CFR 1.530 (b)). EXTENSIONS OF TIME ARE GOVERNED BY 37 CFR 1.550(c). For Requester's Reply (optional): TWO MONTHS from the date of service of any timely filed Patent Owner's Statement (37 CFR 1.535). NO EXTENSION OF THIS TIME PERIOD IS PERMITTED. If Patent Owner does not file a timely statement under 37 CFR 1.530(b), then no reply by requester is permitted. 2. The request for *ex parte* reexamination is DENIED. This decision is not appealable (35 U.S.C. 303(c)). Requester may seek review by petition to the Commissioner under 37 CFR 1.181 within ONE MONTH from the mailing date of this communication (37 CFR 1.515(c)). EXTENSION OF TIME TO FILE SUCH A PETITION UNDER 37 CFR 1.181 ARE AVAILABLE ONLY BY PETITION TO SUSPEND OR WAIVE THE REGULATIONS UNDER 37 CFR 1.183. In due course, a refund under 37 CFR 1.26 ( c ) will be made to requester: a) by Treasury check or.

Joseph R. Pokrzywa **Primary Examiner**

Art Unit: 3992

cc:Requester ( if third party requester )

b) Deposit Account No. \_\_\_\_\_, or

U.S. Patent and Trademark Office PTOL-471 (Rev. 08-06)

c) by credit to a credit card account, unless otherwise notified (35 U.S.C. 303(c)).

Art Unit: 3992

### **DETAILED ACTION**

### Response to Request for ex parte Reexamination

- 1. Reexamination has been requested for claims 1-10 of U.S. Patent Number 5,809,336 ('336 Patent).

- 2. A substantial new question of patentability affecting claims 1-10 of United States Patent Number 5,809,336 is raised by the request for *ex parte* reexamination.

- 3. A prior art patent or printed publication raises a substantial new question of patentability where there is:

- (A) a substantial likelihood that a reasonable Examiner would consider the prior art patent or printed publication important in deciding whether or not the claim is patentable, MPEP §2242 (I) and,

- (B) the same question of patentability as to the claim has not been decided in a previous or pending proceeding or in a final holding of invalidity by a federal court. See MPEP §2242 (III).

Application/Control Number: 90/008,474

Art Unit: 3992

4. The '336 Patent is currently assigned to:

Patriot Scientific Corporation

10989 Via Frontera

San Diego, California 92127

- 5. The '336 Patent application issued on Sep. 15, 1998, with a filing date of Jun. 7, 1995, being a division of U.S. Appl. No. 07/389,334, filed on Aug. 3, 1989, now U.S. Patent No. 5,440,749.

- 6. The '336 Patent is the subject of the litigation *Technology Properties Limited, Inc. v.*Fujitsu Limited et al., No. 2:05-CV-00494-TJW, Federal District Court for the Eastern District of Texas, Marshall Division.

### Discussion of References

- 7. In the request for reexamination, the third party requester alleges that the '336 Patent claims 1-10 are anticipated and/or rendered obvious in light of the following references:

- a. U.S. Patent No. 4,691,124, issued to Ledzius *et al*. (hereafter Ledzius)

- b. U.S. Patent No. 4,718,081, issued to Brenig (hereafter "Brenig")

- Mostek Corp., Mostek 1981 3870/F8 Microcomputer Data Book, Feb. 1981, pp.

III-76 through III-77, III-100 through III-129 and VI-1 through VI-11 (hereafter "Mostek")

- d. Mostek Corp., EDN, Nov. 20, 1976, Advertising (hereafter "EDN")

Application/Control Number: 90/008,474

Art Unit: 3992

Page 4

- e. United Technical Publications, IC Master, 1980, pp. 1and 2016-2040 (hereafter "IC Master")

- f. U.S. Patent No. 4,710,648, issued to Hanamura et al. (hereafter "Hanamura")

- g. Guttag, K.M., "The TMS34010: An Embedded Microprocessor", IEEE Micro, Vol. 8, No. 3, pp. 39-52 (1988), published as the May/June 1988 volume (hereafter "Guttag")

- h. U.S. Patent No. 4,660,155, issued to Thaden et al. (hereafter "Thaden")

- Hitachi America LTD., 8-bit Single Chip Microcomputer Data Book, July 1985,

Table of Contents, pp. 251-279 (hereafter "Hitachi")

- j. U.S. Patent No. 4,334,268, issued to Boney et al. (hereafter "Boney")

- 8. The aforementioned newly cited references are not of record in the file of the '336 Patent and are not cumulative to the art of record in the original file.

- 9. The prior art reference of Ledzius was previously deemed to raise a substantial new question of patentability in a copending reexamination (90/008,306). Thus, the discussion of the teachings of Ledzius, and the corresponding proposed rejections using Ledzius, which are noted as Ledzius in view of Mostek, Ledzius in view of Guttag, and Ledzius in view of Thaden, would not be considered as raising a substantial *new* question for this request. The references of Guttag and Thaden alone, both teach portions of the limitations, as noted by the Third Party Requester.

Art Unit: 3992

However, Guttag and Thaden, alone do not raise a SNQ of patentability to the claims of the '336 Patent.

- 10. Contrarily, it is agreed that the reference of Mostek would have been considered important by a reasonable examiner in deciding whether or not at least independent **claim 6** was patentable, for the reasons discussed *infra*.

- 11. Particularly, Mostek teaches of a microprocessor and clock being constructed on the same IC using the same process technology [see pages III-77 and III-105], and that the on-chip oscillator frequency varies due to changes in manufacturing process, supply voltage, and temperature [see page III-118]. With this, Mostek is seen as teaching of a central processing unit disposed upon an integrated circuit substrate, and varying the processing frequency of a first plurality of electronic devices and the clock rate of a second plurality of electronic devices in the same way as a function of parameter variation in one or more fabrication or operational parameters associated with said integrated circuit substrate. Further Mostek can be interpreted as teaching of an on-chip input/output interface [see page III-105], and an external clock, independent of said oscillator, connected to the input/output interface [see pages III-114 and III-115].

Application/Control Number: 90/008,474

Art Unit: 3992

12. Further, it is also agreed that the combination of references of Hitachi and Boney would have been considered important by a reasonable examiner in deciding whether or not at least independent **claim 1** was patentable, for the reasons discussed *infra*.

Page 6

- 13. Specifically, Hitachi teaches of an integrated circuit that includes an oscillator entirely on-chip, therein being constructed of the same processing technology, having corresponding manufacturing variations [see pages 251 and 262]. Further Hitachi teaches that the HD6805 chip includes an input/output interface [see page 259] and an external timer, being independent of the ring oscillator variable speed clock [seen as Timer 2 on page 259]. The reference of Boney teaches of utilizing an entire ring oscillator variable speed system clock in a single integrated circuit [see Figs. 1 and 7F, and col. 7, lines 14-23].

- 14. Thus, the references of Mostek, Hitachi, and Boney, introduced by the Third Party requester, would likely have been important to a reasonable examiner in deciding whether or not the claims were patentable. The above discussed teachings were not present during the prosecution of the application which became the '336 Patent. Thereby, the references raise a substantial new question regarding at least independent claim 1 and/or independent claim 6 of the instant '336 Patent.

#### Conclusion

15. Claims 1-10 for U.S. Patent Number 5,809,336 are subject to reexamination.

Application/Control Number: 90/008,474

Art Unit: 3992

16. Extensions of time under 37 CFR 1.136(a) will not be permitted in these proceedings

Page 7

because the provisions of 37 CFR 1.136 apply only to "an applicant" and not to parties in a

reexamination proceeding. Additionally, 35 U.S.C. 305 requires that ex parte reexamination

proceedings "will be conducted with special dispatch" (37 CFR 1.550(a)). Extensions of time in

ex parte reexamination proceedings are provided for in 37 CFR 1.550(c).

17. The patent owner is reminded of the continuing responsibility under 37 CFR 1.565(a) to

apprise the Office of any litigation activity, or other prior or concurrent proceeding, involving

Patent No. 5,809,336 throughout the course of this reexamination proceeding. The third party

requester is also reminded of the ability to similarly apprise the Office of any such activity or

proceeding throughout the course of this reexamination proceeding. See MPEP §§ 2207, 2282

and 2286.

18. ALL correspondence relating to this ex parte reexamination proceeding should be

directed as follows:

Please mail any communications to:

Attn: Mail Stop "Ex Parte Reexam"

Central Reexamination Unit

Commissioner for Patents

P. O. Box 1450

Alexandria VA 22313-1450

Please FAX any communications to:

(571) 273-9900

Central Reexamination Unit

Art Unit: 3992

### Please hand-deliver any communications to:

Customer Service Window Attn: Central Reexamination Unit Randolph Building, Lobby Level 401 Dulany Street Alexandria, VA 22314

Any inquiry concerning this communication or earlier communications from the Reexamination Legal Advisor or Examiner, or as to the status of this proceeding, should be directed to the Central Reexamination Unit at telephone number (571) 272-7705.

Signed:

JOSEPH R. POKRZYWA

Joseph R. Pokrzywa

Central Reexamination Unit 3992

(571) 272-7410

Conferees:

ROLAND G. FOSTER CRU EXAMINER-AU 3992 RRAS

PTO/SB/57 (04-05)

Approved for use through 04/30/2007. OMB 0651-0033

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

(Also referred to as FORM PTO-1465)

| REQUEST FOR EX PARTE REEXAMIN                                                                                                                                   | IATION TRANSMITTAL FORM                                                                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Address to: Mail Stop <i>Ex Parte</i> Reexam Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450                                                   | Attorney Docket No.:  Date: January 30, 2007                                             |  |  |

| This is a request for ex parte reexamination pursuit issued September 15, 1998 The requesting the september 15.                                                 | ant to 37 CFR 1.510 of patent number 5,809,336                                           |  |  |

|                                                                                                                                                                 | arty requester. 90008474                                                                 |  |  |

| The name and address of the person requesting re     Public Patent Foundation                                                                                   | examination is:                                                                          |  |  |

| 1375 Broadway, Suite 600                                                                                                                                        | 01/30/07                                                                                 |  |  |

| New York, New York 10018                                                                                                                                        |                                                                                          |  |  |

| 3. X a. A check in the amount of \$\frac{2,520.00}{} is                                                                                                         | enclosed to cover the reexamination fee, 37 CFR 1.20(c)(1);                              |  |  |

| b. The Director is hereby authorized to charge to to Deposit Account No                                                                                         | he fee as set forth in 37 CFR 1.20(c)(1)(submit duplicative copy for fee processing); or |  |  |

| c. Payment by credit card. Form PTO-2038 is a                                                                                                                   | ittached.                                                                                |  |  |

| Any refund should be made by  check or  credit to Deposit Account No. 37 CFR 1.26(c). If payment is made by credit card, refund must be to credit card account. |                                                                                          |  |  |

| 5. A copy of the patent to be reexamined having a double column format on one side of a separate paper is enclosed. 37 CFR 1.510(b)(4)                          |                                                                                          |  |  |

| 6. CD-ROM or CD-R in duplicate, Computer Progra                                                                                                                 | m (Appendix) or large table                                                              |  |  |

| 7. Nucleotide and/or Amino Acid Sequence Submis If applicable, items a. – c. are required.                                                                      | sion                                                                                     |  |  |

| <ul><li>a. Computer Readable Form (CRF)</li><li>b. Specification Sequence Listing on:</li></ul>                                                                 |                                                                                          |  |  |

| i. CD-ROM (2 copies) or CD-R (2 copi                                                                                                                            | es); or                                                                                  |  |  |

| c.  Statements verifying identity of above copic                                                                                                                | ∍8                                                                                       |  |  |

| 8. X A copy of any disclaimer, certificate of correction of                                                                                                     | r reexamination certificate issued in the patent is included.                            |  |  |

| 9. X Reexamination of claim(s) 1 - 10                                                                                                                           | is requested.                                                                            |  |  |

| 10. X A copy of every patent or printed publication relied Form PTO/SB/08, PTO-1449, or equivalent.                                                             | upon is submitted herewith including a listing thereof on                                |  |  |

| <ol> <li>An English language translation of all necessary an<br/>publications is included.</li> </ol>                                                           | d pertinent non-English language patents and/or printed                                  |  |  |

|                                                                                                                                                                 | 62/67/2007 NSALDANA GODGODNA 9000A47A                                                    |  |  |

Page 1 of 2]

This collection of Information is required by 37 CFR 1.510. The information is required to obtain or retain \$\tilde{\text{Berick}(\text{Bi})}\$\text{this}\$ public which is to file (and by the USFTED 0 0 pto process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 2 hours to complete, including gathering, preparing, and submitting the completed application form to the USFTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Mail Stop Ex Parte Reexam, Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

PTO/SB/57 (04-05)

Approved for use through 04/30/2007. OMB 0651-0033

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

|                                                                                                                                                                                                                                                                                                                                                                                                                | ser the Paperwork Reduction Act of 1995, no persons are required to i                                                                                                                                                                                  | respond to a collection of information unles | ss it displays a valid OMB control number. |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|--|--|

| 12. X The attached detailed request includes at least the following items:                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                        |                                              |                                            |  |  |

| <ul> <li>a. A statement identifying each substantial new question of patentability based on prior patents and printed publications. 37 CFR 1.510(b)(1)</li> <li>b. An identification of every claim for which reexamination is requested, and a detailed explanation of the pertinency and manner of applying the cited art to every claim for which reexamination is requested. 37 CFR 1.510(b)(2)</li> </ul> |                                                                                                                                                                                                                                                        |                                              |                                            |  |  |

| 13. 🗌                                                                                                                                                                                                                                                                                                                                                                                                          | A proposed amendment is included (only where the                                                                                                                                                                                                       |                                              |                                            |  |  |

| 14. X                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                                                                                      |                                              |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | the patent owner as provided in 37 CFR 1.33(c).  The name and address of the party served and the                                                                                                                                                      |                                              | been served in its entirety on             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Daniel E. Leckrone, Technology Properties Lin                                                                                                                                                                                                          | nited Drew S. Hamilton,                      |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | 20400 Stevens Creek Blvd., 5th Floor                                                                                                                                                                                                                   | Knobbe, Martens, C                           | Dison & Bear LLP,                          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Cupertino, CA 95014                                                                                                                                                                                                                                    | 550 W.C. St., STE 1                          | 200, San Diego, CA 92101                   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Date of Service:                                                                                                                                                                                                                                       |                                              | ; or                                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | b. A duplicate copy is enclosed since service on pa                                                                                                                                                                                                    | tent owner was not possible.                 |                                            |  |  |

| 15. Co                                                                                                                                                                                                                                                                                                                                                                                                         | rrespondence Address: Direct all communication about                                                                                                                                                                                                   | t the reexamination to:                      |                                            |  |  |

| <u></u>                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                        |                                              |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | address associated with Customer Number:                                                                                                                                                                                                               |                                              |                                            |  |  |

| OR Fire                                                                                                                                                                                                                                                                                                                                                                                                        | n or                                                                                                                                                                                                                                                   |                                              |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | lvidual Name Public Patent Foundation                                                                                                                                                                                                                  |                                              |                                            |  |  |

| Address                                                                                                                                                                                                                                                                                                                                                                                                        | Address 1375 Broadway, Suite 600                                                                                                                                                                                                                       |                                              |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                        |                                              |                                            |  |  |

| City                                                                                                                                                                                                                                                                                                                                                                                                           | New York                                                                                                                                                                                                                                               | State New York                               | Zip 10018                                  |  |  |

| Country                                                                                                                                                                                                                                                                                                                                                                                                        | U.S.A.                                                                                                                                                                                                                                                 |                                              |                                            |  |  |

| Telephor                                                                                                                                                                                                                                                                                                                                                                                                       | ne (212) 796-0570                                                                                                                                                                                                                                      | Email info@pubpat.org                        |                                            |  |  |

| 16. 📉                                                                                                                                                                                                                                                                                                                                                                                                          | The patent is currently the subject of the following concurrent proceeding(s):  a. Copending reissue Application No.  b. Copending reexamination Control No. 90/008,237 and 90/008,306  c. Copending interference No.  d. Copending litigation styled: |                                              |                                            |  |  |

| WAF                                                                                                                                                                                                                                                                                                                                                                                                            | RNING: information on this form may become publicated on this form. Provide credit card information a                                                                                                                                                  | c. Credit card information shot              | uld not be                                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                        | <i>1</i>                                     | 2007                                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Authorized Signature                                                                                                                                                                                                                                   | Date                                         |                                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Daniel B. Ravicher                                                                                                                                                                                                                                     | 47,015                                       | For Patent Owner Requester                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                | Typed/Printed Name                                                                                                                                                                                                                                     | Registration No.                             | For Third Party Requester                  |  |  |

## IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re U.S. Patent No: 5,809,336

Patentee:

Moore et al.

Serial No.:

08/484,918

Filing Date:

June 7, 1995

Issue Date:

September 15, 1998

For:

HIGH PERFORMANCE MICROPROCESSOR HAVING VARIABLE

SPEED SYSTEM CLOCK

# REQUEST FOR EX PARTE REEXAMINATION; REQUESTER'S DETAILED STATEMENT PURSUANT TO 37 C.F.R. §1.510

MS *Ex Parte* Reexamination Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Sir:

The Public Patent Foundation (hereinafter "Requester") is a not-for-profit public service organization that aims to protect the public from the harms caused by undeserved patents and unsound patent policy. Requester, under provisions of 35 U.S.C. 302-307 and 37 C.F.R. § 1.510 et seq., requests ex parte reexamination of claims 1-10 of United States Patent No. 5,809,336 for

"High Performance Microprocessor Having Variable Speed System Clock," issued September 15, 1998 to Charles H. Moore et al. ("the '336 patent") and presently assigned to Technology Properties Limited, Inc. ("TPL"), in view of substantial new questions of patentability raised against the '336 patent by the prior art submitted with this request.

Pursuant to 35 U.S.C. § 303, Requester respectfully submits that the prior art cited herewith raises substantial new questions of patentability with respect to each of claims 1-10 of the '336 patent. This request for reexamination is based on printed publications that were not presented to nor considered by the Patent Office during examination of the '336 patent. Pursuant to 37 C.F.R. § 1.510(b)(1), Requester provides a statement pointing out each substantial new question of patentability for each claim for which it has requested reexamination. Requester also includes a detailed explanation of the pertinence and manner of applying the cited patents and publications to each identified claim pursuant to 37 C.F.R. § 1.510(b)(2). Under 37 C.F.R. § 1.510(b)(3) and (b)(4), Requester includes copies of the pertinent patents and publications relied upon, and a copy of the entire '336 Patent including the front face, drawings, and specification/claims. Requester also includes the fee for requesting reexamination provided under 37 C.F.R. § 1.20(c)(1).

## TABLE OF CONTENTS

| I.  | STATEMENT UNDER 37 C.F.R. §1.510(B)(1) POINTING OUT SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY1                                                                     |                                                                                                                                                                                                                                                                                                           |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | A.                                                                                                                                                                  | Introduction1                                                                                                                                                                                                                                                                                             |  |  |

|     | B.                                                                                                                                                                  | Summary of the Law Governing Reexamination1                                                                                                                                                                                                                                                               |  |  |

|     | C.                                                                                                                                                                  | Subject Matter Background of the '336 Patent2                                                                                                                                                                                                                                                             |  |  |

|     | D.                                                                                                                                                                  | Notice of Pending Litigation Involving the '336 Patent3                                                                                                                                                                                                                                                   |  |  |

|     | E.                                                                                                                                                                  | A substantial new question of patentability as to claims 1-10 is raised by Ledzius in light of Mostek, as further evidenced by prior prosecution correspondences, Paper 6 and Paper 12                                                                                                                    |  |  |

|     | F.                                                                                                                                                                  | A substantial new question of patentability as to claims 1-10 is raised by Mostek                                                                                                                                                                                                                         |  |  |

|     | G.                                                                                                                                                                  | A substantial new question of patentability as to claims 1-10 is raised by Ledzius in light of Guttag                                                                                                                                                                                                     |  |  |

|     | H.                                                                                                                                                                  | A substantial new question of patentability as to claims 1-10 is raised by Ledzius in light of Thaden                                                                                                                                                                                                     |  |  |

|     | I.                                                                                                                                                                  | A substantial new question of patentability as to claims 1-5 is raised by <i>Hitachi</i> in light of <i>Boney</i>                                                                                                                                                                                         |  |  |

| II. | DETAILED EXPLANATION UNDER 37 C.F.R. §1.510(B)(2) OF THE PERTINENCY AND MANNER OF APPLYING THE CITED PRIOR ART TO EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED7 |                                                                                                                                                                                                                                                                                                           |  |  |

|     | A.                                                                                                                                                                  | Cited References                                                                                                                                                                                                                                                                                          |  |  |

|     | B.                                                                                                                                                                  | Claims 1-10 are obvious over <i>Ledzius</i> in light of <i>Mostek</i> , as further evidenced by <i>Brenig</i> and prior prosecution correspondences. <i>Paper</i> 6 and                                                                                                                                   |  |  |

|     |                                                                                                                                                                     | Paper 12       9         1. Claim 1       9         2. Claim 2       17         3. Claim 3       17         4. Claim 4       19         5. Claim 5       19         6. Claim 6       20         7. Claim 7       22         8. Claim 8       22         9. Claim 9       24         10. Claim 10       24 |  |  |

|     |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                           |  |  |

### TABLE OF CONTENTS

| C. | Cla       | Claims 1-10 are obvious over <i>Mostek</i> , and claims 6-8 and 10 are anticipated by <i>Mostek</i> , as further evidenced by <i>EDN</i> , <i>IC Master</i> and |               |  |  |

|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

|    | На        | anamura and prior prosecution correspondences, Paper 6 and                                                                                                      | and           |  |  |

|    | ••••      | Prosecution correspondences, Taper o and                                                                                                                        | raper 12<br>2 |  |  |

|    | 1.        |                                                                                                                                                                 |               |  |  |

|    | 2.        | Claim 2                                                                                                                                                         | 27            |  |  |

|    | 3.        | Claim 3                                                                                                                                                         | 30            |  |  |

|    | 3.<br>4.  | Claim 4                                                                                                                                                         | 32            |  |  |

|    | 5.        | Claim 4Claim 5                                                                                                                                                  | 33            |  |  |

|    | 6.        | Claim 6                                                                                                                                                         | 34            |  |  |

|    | 7.        | Claim 7                                                                                                                                                         | 34            |  |  |

|    | 8.        | Claim 8                                                                                                                                                         | 36            |  |  |

|    | 9.        | Claim 9.                                                                                                                                                        | 36            |  |  |

|    | 10.       | Claim 10                                                                                                                                                        |               |  |  |

| D. | Cla       | ims 1-10 are obvious over <i>Ledzius</i> in light of <i>Guttag</i> and prior                                                                                    | 3/<br>-       |  |  |

|    | pro       | secution correspondence, <i>Paper 6</i>                                                                                                                         |               |  |  |

|    |           |                                                                                                                                                                 |               |  |  |

|    | 1.<br>2.  | Claim 1                                                                                                                                                         | 39            |  |  |

|    | 2.<br>3.  | Claim 2                                                                                                                                                         | 42            |  |  |

|    | 3.<br>4.  | Claim 3                                                                                                                                                         | 43            |  |  |

|    | 5.        | Claim 4                                                                                                                                                         | 44            |  |  |

|    | 5.<br>6.  | Claim 5                                                                                                                                                         | 45            |  |  |

|    | 7.        | Claim 6                                                                                                                                                         | 45            |  |  |

|    | 7.<br>8.  | Claim 7                                                                                                                                                         | 47            |  |  |

|    | 9.        | Claim 8                                                                                                                                                         | 47            |  |  |

|    | 9.<br>10. | Claim 9                                                                                                                                                         | 48            |  |  |

| E. |           | Claim 10                                                                                                                                                        | 48            |  |  |

|    | evid      | ims 1-10 are obvious over <i>Ledzius</i> in light of <i>Thaden</i> , as further                                                                                 | r             |  |  |

|    |           | lenced by prior prosecution correspondence, Paper 6                                                                                                             |               |  |  |

|    | 1.        | Claim 1                                                                                                                                                         | 51            |  |  |

|    | 2.        | Claim 2                                                                                                                                                         | 55            |  |  |

|    | 3.        | Claim 3                                                                                                                                                         | 55            |  |  |

|    | 4.<br>-   | Claim 4                                                                                                                                                         | 57            |  |  |

|    | 5.        | Claim 5                                                                                                                                                         | 57            |  |  |

|    | 6.        | Claim 6                                                                                                                                                         | 58            |  |  |

|    | 7.        | Claim 7                                                                                                                                                         | 60            |  |  |

|    | 8.        | Claim 8                                                                                                                                                         | 61            |  |  |

|    | 9.        | Claim 9                                                                                                                                                         | 61            |  |  |

| D  | 10.       | Claim 10                                                                                                                                                        | 62            |  |  |

| F. | Clair     | ms 1-5 are obvious over <i>Hitachi</i> in light of <i>Boney</i> , as further                                                                                    |               |  |  |

|    | evide     | enced by prior prosecution correspondence, Paper 6                                                                                                              | 64            |  |  |

## TABLE OF CONTENTS

|      | 1.        | Claim 1          | 6/       |

|------|-----------|------------------|----------|

|      | 2.        | Claim 2          | -        |

|      | 3.        | Claim 3          | 70       |

|      | 4.        | Claim 4          | 71       |

|      |           | Claims F         |          |

| III. | CONCLUS   | ION              | 73       |

| IV.  | CERTIFICA | ATION OF SERVICE | 72<br>74 |

# I. STATEMENT UNDER 37 C.F.R. §1.510(B)(1) POINTING OUT SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY

### A. Introduction

Requester respectfully submits that the prior art cited herewith raises substantial new questions of patentability with respect to each of claims 1-10 of the '336 Patent and believes that the '336 Patent warrants reexamination. These questions are summarized in this section I below and discussed in more detail in section II.

## B. Summary of the Law Governing Reexamination

### 1: Claim interpretation

In determining whether a "substantial new question of patentability" warrants reexamination, "the PTO must apply the broadest reasonable meaning to the claim language, taking into account any definitions presented in the specification." *In re Bass*, 314 F.3d 575, 577 (Fed. Cir. 2002). Thus, in the analysis and discussion that follows, the identified claims are given their broadest reasonable interpretation consistent with the '336 Patent specification, even though a narrower interpretation may be appropriate in an infringement suit.

Also, during reexamination, no claim is entitled to a presumption of validity; only a preponderance of the evidence is required in order to invalidate a claim during reexamination.<sup>1</sup>

## 2. Evidence that may be used in a reexamination

In addition to patents and printed publications, admissions by a patentee also may be used as evidence to establish a substantial new question of patentability in combination with a patent

See Xerox Corp. v. 3Com Corp., 69 F. Supp. 2d 404, 407 (W.D.N.Y. 1999) ("[I]n a reexamination proceeding before the PTO, there is no presumption of validity and there must only be a preponderance of the evidence to show unpatentability before the PTO may reject the patent claim(s).").

or a printed publication. MPEP §2217. An admission by a patentee may reside in a record created during litigation. *Id.* Such patentee admissions may be relied upon for any matter affecting patentability. 37 C.F.R. §1.104(c)(3). Many such admissions have been made in the specification.

## C. Subject Matter Background of the '336 Patent

U.S. Patent No. 5,809,336 to Moore, et. al. ("the '336 Patent") (attached hereto as Appendix I) is titled "High Performance Microprocessor Having Variable Speed System Clock." The parent application leading to the patent was filed on August 3, 1989, and the patent was issued on September 15, 1998. The '336 Patent is directed to methods for clocking microcomputers in order to control operation of the microprocessor and other microcomputer components, and to synchronize communications between the microcomputer and external components.

The patent describes a system in which a single integrated chip includes a microprocessor, an oscillator and an input/output (I/O) interface. The microprocessor is clocked by a clock signal derived from the oscillator, and the input/output (I/O) interface is clocked, at least in part, from a different clock source. Some claims require that the oscillator is a ring oscillator. The oscillator is constructed on the same integrated chip and realized with the same type of processing and layout as is used for the processor. Because of this, as the patentee disclosed in the '336 Patent specification and argued during the previous examination, the process variations which affect the processor's speed capability will be matched by variations in the frequency of the clock signal derived from the ring oscillator. For example, when the process

characteristics provide a processor capable of operating at a higher than average frequency, the clock frequency produced by the ring oscillator will also be higher.

During the previous examination of the '336 Patent, the patentee argued that when the microprocessor and oscillator are constructed on the same integrated circuit of the same process technology, their frequencies inherently vary together with changes in various parameters:

The placement of [the clock and the microprocessor] within the same integrated circuit obviates the need for provision of the type of frequency control information described by Sheets, since the microprocessor and clock will naturally tend to vary commensurately in speed as a function of various parameters (e.g., temperature) affecting performance. ('336 Patent Prosecution History, Paper 6, Exhibit 1, p. 8, ¶ 2, emphasis added) ("Paper 6").

The patentee argued that the oscillator and processor frequencies "automatically varying together", which occurs "since both the oscillator...and driven device are on the same substrate", is "crucial to the present invention," and "differs from all cited references." ('336 Patent Prosecution History, Paper 12, Exhibit 2, p. 5, ¶ 1, emphasis added) ("Paper 12"). The patentee distinguished references, such as the Magar reference, that have the oscillator frequency determined by external components because the oscillator and processor frequencies "would inherently not vary due to variations in [parameters] in the same way...as claimed." (Id. at p. 4, ¶ 2).

### D. Notice of Pending Litigation Involving the '336 Patent

Requester is aware that U.S. Pat. No. 5,809,336 is being asserted by Technology Properties Limited, Inc. and Patriot Scientific Corp. before the U.S. District Court for the Eastern District of Texas in the case styled:

Technology Properties Limited, Inc. v. Fujitsu Limited, et al., Case No. 2:05-cv-00494-TJW, U.S. District Court for the Eastern District of Texas;, Marshall Division.

# E. A substantial new question of patentability as to claims 1-10 is raised by *Ledzius* in light of *Mostek*, as further evidenced by prior prosecution correspondences, *Paper 6* and *Paper 12.*<sup>2</sup>

U.S. Patent No. 4,691,124 to Ledzius, et al. ("Ledzius"), entitled "Self-Compensating, Maximum Speed Integrated Circuit," was filed on May 16, 1986, and issued on September 1, 1987. The Mostek 1981 3870/F8 Microcomputer Data Book ("Mostek") describes the 3870 Single Chip family of microcomputers manufactured by Mostek Corp., including the MK3873 chip. The data book was published in February 1981. Neither Ledzius nor Mostek was cited during the previous examination, and both references are prior art under 35 U.S.C. 102(b) and 103(a).

Ledzius in light of Mostek discloses all elements of claims 1-10. In general, both Ledzius and Mostek disclose an integrated circuit that contains a processor clocked by an on-chip ring oscillator and input/output interfaces that can be clocked by an external clock for interfacing asynchronously with external components, such as external memory.

In particular, both references disclose features not disclosed by any reference considered during the previous examination. As discussed in section C above, during prosecution of the '336 patent, the applicant argued that because the claimed oscillator and processor are on the same integrated circuit, their frequencies will inherently vary together due to changes in various parameters, and that this is "crucial to the present invention" and "differs from all cited references." (Paper 6; Paper 12, emphasis added). Ledzius discloses a ring oscillator,

In accord with MPEP § 2131.01, prior prosecution correspondences, *Paper 6* and *Paper 12* are provided to show that it is inherent that the discussed frequenies would vary together and that one skilled in the art in 1989 would know of the inherency.

microprocessor and input/output interface on the same IC, where the oscillator and processor frequencies vary together with changes in various parameters. *Mostek* too discloses an oscillator, microprocessor and input/output interface on the same IC with the interface clocked by an external clock. Requester believes that a reasonable examiner would consider these teachings important, perhaps "crucial", in determining whether claims 1-10 of the '336 patent are patentable. Therefore, the teachings raise a substantial new question of patentability with respect to claims 1-10.

## F. A substantial new question of patentability as to claims 1-10 is raised by Mostek.

As discussed in section E above, *Mostek* is prior art under 35 U.S.C. 102(b) and 103(a), and discloses, either expressly or inherently, or renders obvious all elements of the claims, including features not disclosed by any reference considered during the previous examination, such as a ring oscillator, microprocessor and input/output interface on the same IC, where the oscillator and processor frequencies vary together with changes in various parameters and the interface is clocked by an external clock. Requester believes that a reasonable examiner would consider these teachings important in determining whether claims 1-10 of the 336 patent are patentable, and they raise a substantial new question of patentability with respect to claims 1-10.

# G. A substantial new question of patentability as to claims 1-10 is raised by *Ledzius* in light of *Guttag*.

A technical article by Guttag, et al., entitled "The TMS34010: An Embedded Microprocessor" ("Guttag"), was published in the May/June 1988 volume of the IEEE Micro journal. Guttag describes the structure and operation of the TMS34010 microprocessor chip, which can be used as an input/output interface between a host microprocessor and memory that is

local to the interface. The reference was not cited during the previous examination and is prior art under 35 U.S.C. 102(b) and 103(a).

Ledzius, with Guttag, discloses all elements of the claims, including features not disclosed by any reference considered during the previous examination, such as an oscillator, microprocessor and input/output interface on the same IC with the interface clocked in part by the processor's clock and in part by an external clock. Requester believes that a reasonable examiner would consider these teachings important in determining whether claims 1-10 of the '336 patent are patentable, and they raise a substantial new question of patentability with respect to claims 1-10.

# H. A substantial new question of patentability as to claims 1-10 is raised by *Ledzius* in light of *Thaden*.

U.S. Patent No. 4,660,155 to Thaden, et al. ("Thaden"), entitled "Single Chip Video System With Separate Clocks For Memory Controller, CRT Controller," was filed on July 23, 1984 and issued on April 21, 1987. Thaden describes an interface between a microprocessor and video circuitry, including memory. The reference was not cited during the previous examination and is prior art under 35 U.S.C. 102(b) and 103(a).

Ledzius, with Thaden, discloses all elements of the claims, including features not disclosed by any reference considered during the previous examination, such as an oscillator, microprocessor and input/output interface on the same IC with the interface clocked in part by the processor's clock and in part by an external clock. Requester believes that a reasonable examiner would consider these teachings important in determining whether claims 1-10 of the '336 patent are patentable, and they raise a substantial new question of patentability with respect to claims 1-10.

6

# I. A substantial new question of patentability as to claims 1-5 is raised by *Hitachi* in light of *Boney*.

The 8-Bit Single-Chip Microcomputer Data Book ("Hitachi") was published in July 1985 by Hitachi Corp. U.S. Patent No. 4,334,268 to Boney, et al. ("Boney"), entitled "Microcomputer With Branch On Bit Set/Clear Instructions," was filed on May 1, 1979 and issued on June 8, 1982. Hitachi describes the HD6800 family of microcomputer chips, including the HD6805W1 integrated circuit chip. Boney also describes a single-chip microcomputer. Neither reference was cited during the previous examination, and both references are prior art under 35 U.S.C. 102(b) and 103(a).

Hitachi, with Boney, discloses all elements of the claims, including features not disclosed by any reference considered during the previous examination, such as a ring oscillator, microprocessor and input/output interface on the same IC with the interface clocked in part by the processor's clock and in part by an external clock. Requester believes that a reasonable examiner would consider these teachings important in determining whether claims 1-5 of the '336 patent are patentable, and they raise a substantial new question of patentability with respect to claims 1-5.

# II. DETAILED EXPLANATION UNDER 37 C.F.R. §1.510(B)(2) OF THE PERTINENCY AND MANNER OF APPLYING THE CITED PRIOR ART TO EVERY CLAIM FOR WHICH REEXAMINATION IS REQUESTED

#### A. Cited References

A copy of every patent or publication relied upon or referred to is attached as listed below and is cited in the attached modified Form PTO/SB/42.

Exhibit 1 Moore, et al., Prosecution History for U.S. Patent No. 5,809,336, Paper 6, Apr. 11, 1996 Amendment, pp. 1-10, ("Paper 6");

- Exhibit 2 Moore, et al., Prosecution History for U.S. Patent No. 5,809,336, Paper 12, July 3, 1997 Amendment, pp. 1-5, ("Paper 12");

- Exhibit 3 Ledzius, et al., U.S. Patent No. 4,691,124, "Self-Compensating, Maximum Speed Integrated Circuit," filed on May 16, 1986 and issued on September 1, 1987, ("Ledzius");

- Exhibit 4 Brenig, U.S. Patent No. 4,718,081, "Method and apparatus for reducing handoff errors in a cellular radio telephone communications system," filed on November 13, 1986 and issued on January 5, 1988, ("Brenig");

- Exhibit 5 Mostek Corp., Mostek 1981 3870/F8 Microcomputer Data Book, Feb. 1981, pp. III-76 through III-77, III-100 through III-129 and VI-1 through VI-11("Mostek");

- Exhibit 6 Mostek Corp., EDN, Nov. 20, 1976, Advertising, ("EDN");

- Exhibit 7 United Technical Publications, IC Master, 1980, pp. 1 and 2016-2040, ("IC Master");

- Exhibit 8 Hanamura, et al., U.S. Patent No. 4,710,648, "Semiconductor Including Signal Processor And Transient Detector For Low Temperature Operation," filed May 6, 1985, issued December 1, 1987, ("Hanamura");

- Exhibit 9 Guttag, K. M., "The TMS34010: An Embedded Microprocessor," IEEE Micro, Vol. 8, No. 3, pp. 39-52 (1988), published as the May/June 1988 volume, ("Guttag");

- Exhibit 10 Thaden, et al., U.S. Patent No. 4,660,155, "Single Chip Video System With Separate Clocks For Memory Controller, CRT Controller," filed July 23, 1984, issued April 21, 1987, ("Thaden");

- Exhibit 11 Hitachi America Ltd., 8-Bit Single-Chip Microcomputer Data Book, July 1985, Table of Contents, pp. 251-279, ("Hitachi"); and

- Exhibit 12 Boney, et al., U.S. Patent No. 4,334,268, "Microcomputer With Branch On Bit Set/Clear Instructions," filed May 1, 1979, issued June 8, 1982, ("Boney").

Additionally, Appendix I is a copy of the patent to be reexamined, U.S. Patent No. 5,809,336 to Moore, et al., in double column format.

# B. Claims 1-10 are obvious over *Ledzius* in light of *Mostek*, as further evidenced by *Brenig* and prior prosecution correspondences, *Paper 6* and *Paper 12*.<sup>3</sup>

Ledzius, alone, arguably discloses all elements of claims 1-10 and therefore anticipates the claims. However, in any event, all elements of claims 1-10 would at least have been obvious to one of ordinary skill in 1989 over Ledzius in light of Mostek and the knowledge of one skilled in the art in 1989 as shown in Brenig (U.S. Patent No. 4,718,081, filed on November 13, 1986 and issued on January 5, 1988).

### 1. Claim 1

# (a) A microprocessor system, comprising a single integrated circuit including a central processing unit

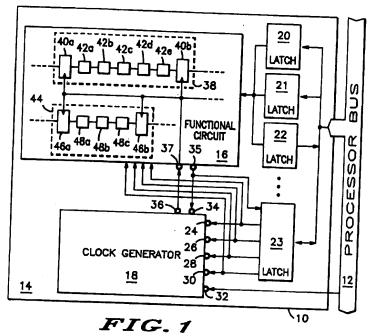

Ledzius discloses an integrated circuit (IC) 10 that includes a microprocessor system that has a central processing unit, "functional circuit 16." (Exhibit 3, Fig. 1 (shown in section B(1)(b), below); 2:28-31; 4:5-7). Functional circuit 16 is a processor that performs "a relatively large quantity of arithmetic operations on initial data" for "any of a wide variety of diverse tasks," including digital signal processing or cryptographic algorithms. (2:32-38; 2:43-54). It would have been obvious to one of ordinary skill in 1989 that the disclosed digital signal processor was commonly implemented as a programmable microprocessor. (See, e.g., Brenig (Exhibit 4) at 5:64-67 ("[c]ell site controller 26 may be any conventional digital signal processor, and preferably includes a central processing unit.")). As discussed in section C below, Mostek also discloses a single integrated circuit with a CPU.

In accord with MPEP § 2131.01, prior prosecution correspondences, *Paper 6* and *Paper 12* are provided to show that it is inherent that the discussed frequenies would vary together and that one skilled in the art in 1989 would know of the inherency. Similarly, the Brenig reference is provided to show that a digital signal processor is commonly implemented as a microprocessor.

# (b) and an entire ring oscillator variable speed system clock in said single integrated circuit and connected to said central processing unit for clocking said central processing unit,

Ledzius discloses an "integrated circuit 10" that includes an entire ring oscillator, "clock

generator 18", and a central processing unit, "functional circuit 16." (Fig. 1; 1:65-68; *also* 2:28-31; 4:5-7; Abstract) The oscillator is complete and operates "without communication or interference from other ICs or devices." (2:33-40; *also* 4:22-23; 5:53-58; 6:63-65) The oscillator has a variable speed: "[t]he frequency of the clock signal produced by clock generator 18 varies...." (4:5-21).

Ledzius teaches that the on-chip oscillator clocks the processor: "signal 58' [becoming signal 36 in Figs. 1 and 2] represents the clock which drives functional circuit 16 (see FIG. 1)." (5:56-58; also 1:53-56; 1:65-68; 2:58-60; 4:22-23; and Figs. 1-2). Additionally, as discussed in section C below, Mostek, Exhibit 5, discloses that the single IC, with a CPU, also has an entire on-chip oscillator connected to drive the CPU with a varying frequency.

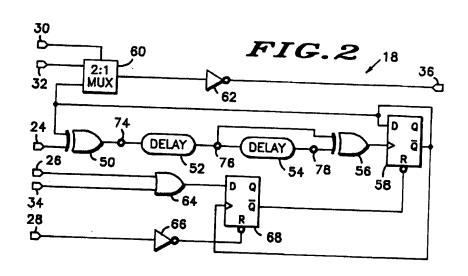

Ledzius discloses that the on-chip clock includes a ring oscillator. Although a common configuration, the meaning of "ring oscillator" should not be limited to having only inverters connected in a loop. It should be reasonably construed to include any cascade of delay elements connected in a circular circuit path that provides unstable feedback (signals that cause the elements to switch from their previous state) to generate a clock signal. Ledzius discloses a

"Clock generator 18" that includes three logic components, 50, 56 and 58, and two additional delays, 52 and 54, connected in a circular circuit path to provide an unstable feedback that generates clock signal 58'. (Figs. 2-3; 4:50-5:60)