04/24/09

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US Mailing Date: April 24, 2009

publications is included.

PTO/SB/57 (08-08) Approved for use through 08/31/2010. OMB 0651-0033

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE DTCUnder the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

(Also referred to as FORM PTO-1465) Address to: Mail Stop Ex Parte Reexam Attorney Docket No.: 24567-0002RX1 **Commissioner for Patents** P.O. Box 1450 Date: April 24, 2009 Alexandria, VA 22313-1450 1.  $| \checkmark |$  This is a request for ex parte reexamination pursuant to 37 CFR 1.510 of patent number 5,809,336 issued September 15, 1998 . The request is made by: ✓ third party requester. patent owner. Fish & Richardson, P.C. 3200 RBC Plaza, 60 South Sixth Street Minneapolis, MN 55402 a. A check in the amount of \$\frac{1}{20}\$ is enclosed to cover the reexamination fee, 37 CFR 1.20(c)(1); The Director is hereby authorized to charge the fee as set forth in 37 CFR 1.20(c)(1) to Deposit Account No. <u>0</u>6-1050 c. Payment by credit card. Form PTO-2038 is attached. Any refund should be made by \_\_ check or \_\_ credit to Deposit Account No. 06-1050 37 CFR 1.26(c). If payment is made by credit card, refund must be to credit card account. A copy of the patent to be reexamined having a double column format on one side of a separate paper is enclosed. 37 CFR 1.510(b)(4) CD-ROM or CD-R in duplicate, Computer Program (Appendix) or large table Landscape Table on CD Nucleotide and/or Amino Acid Sequence Submission If applicable, items a. - c. are required. a. Computer Readable Form (CRF) b. Specification Sequence Listing on: i. CD-ROM (2 copies) or CD-R (2 copies); or c. Statements verifying identity of above copies A copy of any disclaimer, certificate of correction or reexamination certificate issued in the patent is included. Reexamination of claim(s) 1-10 is requested. A copy of every patent or printed publication relied upon is submitted herewith including a listing thereof on Form PTO/SB/08\_PTO-1449, or equivalent 65/61/2669 REELL1 6666661 661656 96669 57 Form PTO/SB/08, PTO-1449, or equivalent. An English language translation of all necessary and pertinent non-English language patents and/or printed

> [Page 1 of 2] This collection of information is required by 37 CFR 1.510. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 2 hours to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent

> and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Mail Stop Ex Parte Reexam, Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

If you need assistance in completing the form, call 1-800-PTO-9199 and select option 2.

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US Mailing Date: April 24, 2009

Express Mail Laber No.: EV 8316459/U US

Mailing Date: April 24, 2009

Approved for use through 08/31/2010. OMB 0651-0033

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

| 12. The attached detailed request includes at least the fo                                                                                                                                                                    | llowing items:                                                             |                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------|

| <ul> <li>a. A statement identifying each substantial new ques publications. 37 CFR 1.510(b)(1)</li> <li>b. An identification of every claim for which reexamin and manner of applying the cited art to every claim</li> </ul> | ation is requested, and a det                                              | tailed explanation of the pertinency |

| 13. A proposed amendment is included (only where the p                                                                                                                                                                        | patent owner is the requester                                              | r). 37 CFR 1.510(e)                  |

| <ul> <li>a. It is certified that a copy of this request (if filed by of the patent owner as provided in 37 CFR 1.33(c).</li> <li>The name and address of the party served and the</li> </ul>                                  | ·                                                                          | has been served in its entirety on   |

| Larry E. Henneman, Jr., Reg. No. 41,063                                                                                                                                                                                       |                                                                            |                                      |

| Henneman & Associates, PLC                                                                                                                                                                                                    |                                                                            |                                      |

| 714 W. Michigan Avenue, Three Rivers, MI 4                                                                                                                                                                                    | 9093                                                                       |                                      |

| Date of Service: April 24, 2009                                                                                                                                                                                               |                                                                            | ; or                                 |

| b. A duplicate copy is enclosed since service on pa                                                                                                                                                                           | tent owner was not possible                                                |                                      |

| 15. Correspondence Address: Direct all communication about                                                                                                                                                                    | t the reexamination to:                                                    |                                      |

| The address associated with Customer Number: 21691                                                                                                                                                                            |                                                                            |                                      |

| OR Firm or O H O H I S H O B H                                                                                                                                                                                                | ·                                                                          |                                      |

| Individual Name Greg H. Gardella, Fish & Richardso                                                                                                                                                                            | n P.C.                                                                     |                                      |

| Address                                                                                                                                                                                                                       |                                                                            |                                      |

| 60 South Sixth Street, 3200 RBC Plaza                                                                                                                                                                                         |                                                                            |                                      |

| City Minneapolis                                                                                                                                                                                                              | State MN                                                                   | <sup>Zip</sup> 55402                 |

| Country USA                                                                                                                                                                                                                   |                                                                            |                                      |

| Telephone 612-335-5070                                                                                                                                                                                                        | Email ghg@fr.com                                                           |                                      |

| 16. The patent is currently the subject of the following c  a. Copending reissue Application No.  b. Copending reexamination Control No.  c. Copending Interference No.  d. Copending litigation styled:                      |                                                                            | ·                                    |

| WARNING: Information on this form may become pub included on this form Provide credit card information                                                                                                                        | lic. Credit card information<br>and authorization on PTO<br>April 24, 2009 | n should not be<br>0-2038.           |

| Authorized Signature                                                                                                                                                                                                          | Date                                                                       |                                      |

| Greg H, Gardella                                                                                                                                                                                                              | 46,045                                                                     | ☐ For Patent Owner Requester         |

| Typed/Printed Name                                                                                                                                                                                                            | Registration No.                                                           | For Third Party Requester            |

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US

Mailing Date: April 24, 2009

#### **Privacy Act Statement**

The **Privacy Act of 1974 (P.L. 93-579)** requires that you be given certain information in connection with your submission of the attached form related to a patent application or patent. Accordingly, pursuant to the requirements of the Act, please be advised that: (1) the general authority for the collection of this information is 35 U.S.C. 2(b)(2); (2) furnishing of the information solicited is voluntary; and (3) the principal purpose for which the information is used by the U.S. Patent and Trademark Office is to process and/or examine your submission related to a patent application or patent. If you do not furnish the requested information, the U.S. Patent and Trademark Office may not be able to process and/or examine your submission, which may result in termination of proceedings or abandonment of the application or expiration of the patent.

The information provided by you in this form will be subject to the following routine uses:

- The information on this form will be treated confidentially to the extent allowed under the Freedom of Information Act (5 U.S.C. 552) and the Privacy Act (5 U.S.C 552a). Records from this system of records may be disclosed to the Department of Justice to determine whether disclosure of these records is required by the Freedom of Information Act.

- A record from this system of records may be disclosed, as a routine use, in the course of presenting evidence to a court, magistrate, or administrative tribunal, including disclosures to opposing counsel in the course of settlement negotiations.

- A record in this system of records may be disclosed, as a routine use, to a Member of Congress submitting a request involving an individual, to whom the record pertains, when the individual has requested assistance from the Member with respect to the subject matter of the record.

- 4. A record in this system of records may be disclosed, as a routine use, to a contractor of the Agency having need for the information in order to perform a contract. Recipients of information shall be required to comply with the requirements of the Privacy Act of 1974, as amended, pursuant to 5 U.S.C. 552a(m).

- 5. A record related to an International Application filed under the Patent Cooperation Treaty in this system of records may be disclosed, as a routine use, to the International Bureau of the World Intellectual Property Organization, pursuant to the Patent Cooperation Treaty.

- 6. A record in this system of records may be disclosed, as a routine use, to another federal agency for purposes of National Security review (35 U.S.C. 181) and for review pursuant to the Atomic Energy Act (42 U.S.C. 218(c)).

- 7. A record from this system of records may be disclosed, as a routine use, to the Administrator, General Services, or his/her designee, during an inspection of records conducted by GSA as part of that agency's responsibility to recommend improvements in records management practices and programs, under authority of 44 U.S.C. 2904 and 2906. Such disclosure shall be made in accordance with the GSA regulations governing inspection of records for this purpose, and any other relevant (i.e., GSA or Commerce) directive. Such disclosure shall not be used to make determinations about individuals.

- 8. A record from this system of records may be disclosed, as a routine use, to the public after either publication of the application pursuant to 35 U.S.C. 122(b) or issuance of a patent pursuant to 35 U.S.C. 151. Further, a record may be disclosed, subject to the limitations of 37 CFR 1.14, as a routine use, to the public if the record was filed in an application which became abandoned or in which the proceedings were terminated and which application is referenced by either a published application, an application open to public inspection or an issued patent.

- A record from this system of records may be disclosed, as a routine use, to a Federal, State, or local law enforcement agency, if the USPTO becomes aware of a violation or potential violation of law or regulation.

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US Mailing Date: April 24, 2009

PTO/SB/57 (08-08) Approved for use through 08/31/2010. OMB 0651-0033 U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

(Also referred to as FORM PTO-1465)

### REQUEST FOR EX PARTE REEXAMINATION TRANSMITTAL FORM Address to: Mail Stop Ex Parte Reexam Attorney Docket No.: 24567-0002RX1 Commissioner for Patents P.O. Box 1450 Date: April 24, 2009 Alexandria, VA 22313-1450 This is a request for ex parte reexamination pursuant to 37 CFR 1.510 of patent number 5,809,336 issued September 15, 1998 ...... The request is made by: patent owner. ✓ third party requester. 2. \ \ The name and address of the person requesting reexamination is: Fish & Richardson, P.C. 3200 RBC Plaza, 60 South Sixth Street Minneapolis, MN 55402 a. A check in the amount of \$ is enclosed to cover the reexamination fee, 37 CFR 1.20(c)(1); The Director is hereby authorized to charge the fee as set forth in 37 CFR 1.20(c)(1) to Deposit Account No. 06-1050 Payment by credit card. Form PTO-2038 is attached. Any refund should be made by Check or occupied credit to Deposit Account No. 06-1050 37 CFR 1.26(c). If payment is made by credit card, refund must be to credit card account. A copy of the patent to be reexamined having a double column format on one side of a separate paper is enclosed. 37 CFR 1.510(b)(4) CD-ROM or CD-R in duplicate, Computer Program (Appendix) or large table Landscape Table on CD Nucleotide and/or Amino Acid Sequence Submission If applicable, items a. - c. are required. a. Computer Readable Form (CRF) b. Specification Sequence Listing on: i. CD-ROM (2 copies) or CD-R (2 copies); or c. Statements verifying identity of above copies A copy of any disclaimer, certificate of correction or reexamination certificate issued in the patent is included. Reexamination of claim(s) is requested. A copy of every patent or printed publication relied upon is submitted herewith including a listing thereof on Form PTO/SB/08, PTO-1449, or equivalent. An English language translation of all necessary and pertinent non-English language patents and/or printed publications is included.

[Page 1 of 2] This collection of information is required by 37 CFR 1.510. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 2 hours to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Mail Stop Ex Parte Reexam, Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US

Mailing Date: April 24, 2009

COPY

PTO/SB/57 (08-08)

Approved for use through 08/31/2010. OMB 0651-0033

U.S. Patent and Trademark Office; U.S. DEPARTMENT OF COMMERCE Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number 12. ✓ The attached detailed request includes at least the following items: a. A statement identifying each substantial new question of patentability based on prior patents and printed publications. 37 CFR 1.510(b)(1) b. An identification of every claim for which reexamination is requested, and a detailed explanation of the pertinency and manner of applying the cited art to every claim for which reexamination is requested. 37 CFR 1.510(b)(2) A proposed amendment is included (only where the patent owner is the requester). 37 CFR 1.510(e) a. It is certified that a copy of this request (if filed by other than the patent owner) has been served in its entirety on the patent owner as provided in 37 CFR 1.33(c). The name and address of the party served and the date of service are: Larry E. Henneman, Jr., Reg. No. 41,063 Henneman & Associates, PLC 714 W. Michigan Avenue, Three Rivers, MI 49093 Date of Service: April 24, 2009 b. A duplicate copy is enclosed since service on patent owner was not possible. 15. Correspondence Address: Direct all communication about the reexamination to: The address associated with Customer Number: 21691 OR Firm or Greg H. Gardella, Fish & Richardson P.C. Individual Name Address 60 South Sixth Street, 3200 RBC Plaza City State Zip 55402 Minneapolis MN Country USA Telephone 612-335-5070 ghg@fr.com The patent is currently the subject of the following concurrent proceeding(s): 16. a. Copending reissue Application No. □ b. Copending reexamination Control No. c. Copending Interference No. d. Copending litigation styled: WARNING; Information on this form may become public. Credit card information should not be included on this Provide credit card information and authorization on PTO-2038. April 24, 2009 Authorized Signature Date Greg H. Gardella 46,045 For Patent Owner Requester Typed/Printed Name Registration No. For Third Party Requester

CERTIFICATE OF FILING BY EXPRESS MAIL Express Mail Label No.: EV 831645970 US

Mailing Date: April 24, 2009

#### **Privacy Act Statement**

The **Privacy Act of 1974 (P.L. 93-579)** requires that you be given certain information in connection with your submission of the attached form related to a patent application or patent. Accordingly, pursuant to the requirements of the Act, please be advised that: (1) the general authority for the collection of this information is 35 U.S.C. 2(b)(2); (2) furnishing of the information solicited is voluntary; and (3) the principal purpose for which the information is used by the U.S. Patent and Trademark Office is to process and/or examine your submission related to a patent application or patent. If you do not furnish the requested information, the U.S. Patent and Trademark Office may not be able to process and/or examine your submission, which may result in termination of proceedings or abandonment of the application or expiration of the patent.

The information provided by you in this form will be subject to the following routine uses:

- The information on this form will be treated confidentially to the extent allowed under the Freedom of Information Act (5 U.S.C. 552) and the Privacy Act (5 U.S.C 552a). Records from this system of records may be disclosed to the Department of Justice to determine whether disclosure of these records is required by the Freedom of Information Act.

- A record from this system of records may be disclosed, as a routine use, in the course of

presenting evidence to a court, magistrate, or administrative tribunal, including disclosures to

opposing counsel in the course of settlement negotiations.

- A record in this system of records may be disclosed, as a routine use, to a Member of Congress submitting a request involving an individual, to whom the record pertains, when the individual has requested assistance from the Member with respect to the subject matter of the record.

- 4. A record in this system of records may be disclosed, as a routine use, to a contractor of the Agency having need for the information in order to perform a contract. Recipients of information shall be required to comply with the requirements of the Privacy Act of 1974, as amended, pursuant to 5 U.S.C. 552a(m).

- A record related to an International Application filed under the Patent Cooperation Treaty in this system of records may be disclosed, as a routine use, to the International Bureau of the World Intellectual Property Organization, pursuant to the Patent Cooperation Treaty.

- 6. A record in this system of records may be disclosed, as a routine use, to another federal agency for purposes of National Security review (35 U.S.C. 181) and for review pursuant to the Atomic Energy Act (42 U.S.C. 218(c)).

- 7. A record from this system of records may be disclosed, as a routine use, to the Administrator, General Services, or his/her designee, during an inspection of records conducted by GSA as part of that agency's responsibility to recommend improvements in records management practices and programs, under authority of 44 U.S.C. 2904 and 2906. Such disclosure shall be made in accordance with the GSA regulations governing inspection of records for this purpose, and any other relevant (i.e., GSA or Commerce) directive. Such disclosure shall not be used to make determinations about individuals.

- 8. A record from this system of records may be disclosed, as a routine use, to the public after either publication of the application pursuant to 35 U.S.C. 122(b) or issuance of a patent pursuant to 35 U.S.C. 151. Further, a record may be disclosed, subject to the limitations of 37 CFR 1.14, as a routine use, to the public if the record was filed in an application which became abandoned or in which the proceedings were terminated and which application is referenced by either a published application, an application open to public inspection or an issued patent.

- A record from this system of records may be disclosed, as a routine use, to a Federal, State, or local law enforcement agency, if the USPTO becomes aware of a violation or potential violation of law or regulation.

with early they be the

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Patent of:

Moore et al.

U.S. Patent No.:

5,809,336

Issue Date:

Sept. 15, 1998

Serial No.:

09/484,918

Filing Date:

June 7, 1995

Mail Stop Ex Parte Reexam Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

## REQUEST FOR EX PARTE REEXAMINATION UNDER 35 U.S.C. § 302 AND 37 C.F.R. § 1.510

Reexamination under 35 U.S.C. § 302 and 37 C.F.R. § 1.510 is requested for all claims (i.e., claims 1-10) of U.S. Patent No. 5,809,336 (the '336 patent) which issued on September 15, 1998 to Moore et al..

| CERTIFICATE           | OF MAILING BY EXPRESS MAIL |

|-----------------------|----------------------------|

| Express Mail Label No | EV 831645970 US            |

|                       | · April 24, 2009           |

| Date of Deposit       | April 24, 2007             |

### TABLE OF CONTENTS

|                | <u>Page</u>                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| I.             | INTRODUCTION                                                                                                                                 |

| II.            | CLAIMS FOR WHICH REEXAMINATION IS REQUESTED                                                                                                  |

| III.           | PATENTS AND PRINTED PUBLICATIONS PRESENTED TO SHOW SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY                                                |

| IV.            | CO-PENDING PROSECUTION AND LITIGATION                                                                                                        |

| V.             | THE PROSECUTION HISTORY OF THE '336 PATENT 4                                                                                                 |

| VI.            | POSITIONS TAKEN BY PATENT OWNER THAT ARE MATERIAL TO PATENTABILITY                                                                           |

| VII.           | QUESTIONS OF PATENTABILITY PRESENTED HEREIN ARE NEW RELATIVE TO THE PENDING REEXAMINATION PROCEEDINGS                                        |

| VIII.          | THE MOSTEK REFERENCE ANTICIPATES OR RENDERS OBVIOUS CLAIMS 1- 10 OF THE '336 PATENT                                                          |

| A.<br>B.<br>C. | Summary of the Teachings of the Mostek Reference                                                                                             |

| D.<br>E.       | Claim Chart Setting Forth the Correspondence Between the Mostek Reference and Claims 1-10 of the '336 Patent                                 |

| IX.            | THE DOZIER REFERENCE ANTICIPATES OR RENDERS OBVIOUS CLAIMS 1-10 OF THE '336 PATENT                                                           |

| A.<br>B.       | Summary of the Teachings of the Dozier Reference                                                                                             |

| C.             | The Dozier Reference, in Light of the Mostek, Kato, and Ledzius References, Renders                                                          |

| D.             | Obvious Claims 1-10 of the '336 Patent                                                                                                       |

| E.             | The Dozier Reference Anticipates or Renders Obvious the Newly Introduced Claims of the '336 Patent                                           |

| X.<br>A.       | THE RICHTER REFERENCE ANTICIPATES OR RENDERS OBVIOUS CLAIMS 1- 10 OF THE '336 PATENT 63 Summary of the Teachings of the Richter Reference 63 |

| А.<br>В.       | The Richter Reference Anticipates Claims 1-10 of the '336 Patent                                                                             |

| C.             | The Richter Reference, in Light of the McDermott, Ledzius, and Kato References, Renders Obvious Claims 1-10 of the '336 Patent               |

### TABLE OF CONTENTS

| D.  | <b>D.</b> Claim Chart Setting Forth the Correspondence Between the Richter Reference and            |  |

|-----|-----------------------------------------------------------------------------------------------------|--|

|     | Claims 1-10 of the '336 Patent                                                                      |  |

| E.  | The Richter Reference Anticipates or Renders Obvious the Newly Introduced Claims of the '336 Patent |  |

|     | the 350 ratent                                                                                      |  |

| XI. | CONCLUSION87                                                                                        |  |

#### TABLE OF CONTENTS

#### APPENDICES

APPENDIX A - U.S. Patent No. 5,809,336 to Moore et al.

**APPENDIX B** - Relevant portions of the '336 patent file history.

**APPENDIX C** - Relevant portions of the merged '336 reexamination (Control No. 90/008,474)

**APPENDIX D** - U.S. Patent No. 4,853,841 to Richter.

**APPENDIX E** - U.S. Patent No. 4,348,743 to Dozier.

**APPENDIX** F - Mostek, 3870 Microcomputer Data Book (Feb. 1981).

APPENDIX G - U.S. Patent No. 4,931,748 to McDermott et al.

APPENDIX H - U.S. Patent No. 4,766,567 to Kato.

APPENDIX I - U.S. Patent No. 4,691,124 to Ledzius et al.

APPENDIX J - IC Master 1980 (United Technical Publications) (1980)

#### I. INTRODUCTION

The independent claims of the '336 patent are directed to a microprocessor system that includes a ring oscillator for a system clock and a central processing unit (CPU) on a single integrated circuit. The independent claims require the ring oscillator and CPU to be constructed of the same process technology so that the speed of the ring oscillator and the CPU vary together. The independent claims further require an on-chip input/output (I/O) interface, to which a second clock independent of the ring oscillator is connected.

During prosecution of the underlying application the Patent Owner amended the independent claims in response to a prior art rejection to recite the second clock independent of the variable speed system clock for clocking the I/O interface. A summary of an examiner interview conducted on April 23, 1998 indicated that the claims were allowed because the Examiner believed that the prior art contained no disclosure or suggestion of clocking an I/O interface with a second clock independent of the variable speed system clock.

The Mostek reference (Appendix F), which was not before the original Examiner, discloses precisely this feature. Mostek describes a single semiconductor chip containing a main control logic that is clocked by a variable frequency internal oscillator. The chip includes a serial I/O port that is clocked by a fixed frequency external clock that is independent of the internal oscillator. (Appendix F, pages III-105 and III-114 to III-115) Furthermore, the Mostek reference teaches every other feature recited in each of the independent claims of the '336 patent with the sole exception that the Mostek reference does not explicitly state that the on-chip "variable speed oscillator" is a "ring oscillator" as recited in the claims. However, according to the Patent Owner, a variable speed oscillator qualifies as a ring oscillator as that term is used in the '336 patent. In connection with recent attempts to persuade major companies to take licenses under the '336 patent the Patent Owner has repeatedly asserted in writing that "industry best practices dictate" that clock generators include ring oscillators. If the Office accepts this premise, then the Mostek reference would be understood by one skilled in the art as disclosing a ring oscillator given that commercial clock generators have not substantially changed in material respect since the date of the Mostek reference. If interpreted in this way, the Mostek reference anticipates claims 1-7, 9, and 10 of the '336 patent.

In any case, one skilled in the art would have found apparent reasons to combine the Mostek reference with the ring oscillator system clock taught by the Kato reference (Appendix H). One skilled in the art would realize the benefits of implementing Kato's ring oscillator as Mostek's variable oscillator to reduce power consumption during periods of lessened processing demand and to increase clock speed (and power consumption) during periods of increased processing demand. (Appendix H, col. 11, lines 2-7). As explained in more detail below, claims 1-10 of the '336 patent are at a minimum rendered obvious by Mostek in view of Kato.

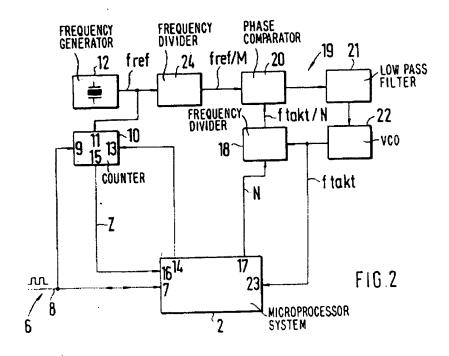

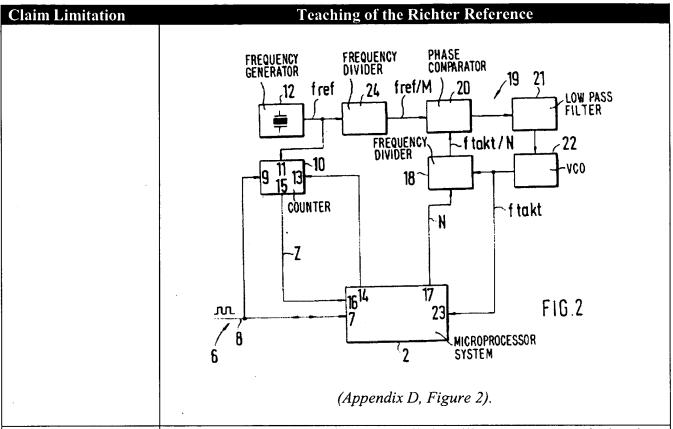

Moreover, two additional references that were not before the Examiner – Richter (Appendix D) and Dozier (Appendix E) – each disclose the second, independent I/O clock thought to be missing from the prior art. Richter teaches clocking an on-chip I/O port with an oscillator independent of a system clock. Richter teaches a microprocessor system having a serial interface which is connected by an input/output port to a signal line of a serial bus system. Richter teaches a signal "ftakt" for clocking the serial I/O port of the microprocessor that is independent of the CPU clock: "the data transmission of the serial interface is supplied with the clock frequency signal 'ftakt', and the microprocessor of the microprocessor system 2 is equipped with its own system clock generator." (Appendix D, col. 4, lines 34-43 and 58-62) Richter describes the system clock of the microprocessor as a "separate system clock generator for the microprocessor" that is independent of the I/O clock signal. (Appendix D, col. 4, lines 36-47) The remaining features recited in the claims of the '336 patent are plainly disclosed in Richter. Dozier also discloses the above described features of the claims of the '336 patent. Both Richter and Dozier, alone or in combination with other references, at a minimum render obvious all claims of the '336 patent (i.e. claims 1-10) as explained in detail in the claim charts set forth below.

The foregoing questions of patentability are new even with respect to the reexamination requests previously filed against the '336 patent. Neither the Richter reference (Appendix D) nor the Dozier reference (Appendix E) were before the examiner during the original examination of the '336 patent and are not currently before the examiner in the pending merged reexamination proceeding (Reexamination Control Number 90/008,306). As to the Mostek reference, the arguments presented herein are substantially different than those presented in the reexamination request filed by the Public Patent Foundation on January 30, 2007. For example, that earlier request did not argue that the Mostek reference anticipates any claim of the '336 patent. The

Mostek reference has not been relied upon to support a rejection in the pending reexamination proceedings (and as to the underlying application the Mostek reference was not of record).

#### II. CLAIMS FOR WHICH REEXAMINATION IS REQUESTED

Reexamination is requested for all claims (i.e., claims 1-10) of the '336 patent in view of the publications discussed below. A copy of the '336 patent (including a certificate of correction) is attached as Appendix A of this document, and copies of the relevant portions of the '336 patent prosecution history are attached as Appendix B.

## III. PATENTS AND PRINTED PUBLICATIONS PRESENTED TO SHOW SUBSTANTIAL NEW QUESTIONS OF PATENTABILITY

- 1. U.S. Patent No. 4,853,841 to Richter (hereinafter "Richter"), attached as Appendix D.

- 2. U.S. Patent No. 4,348,743 to Dozier (hereinafter "Dozier"), attached as Appendix E.

- 3. Mostek, 3870 Microcomputer Data Book (Feb. 1981) (hereinafter "Mostek") attached as Appendix F.

- 4. U.S. Patent No. 4,931,748 to McDermott et al (hereinafter "McDermott") attached as Appendix G.

- 5. U.S. Patent No. 4,766,567 to Kato (hereinafter "Kato") attached as Appendix H.

- 6. U.S. Patent No. 4,691,124 to Ledzius et al (hereinafter "Ledzius") attached as Appendix I.

- 7. IC Master 1980 (United Technical Publications) (1980) (hereinafter "IC Master") attached as Appendix J.

It is believed that the references in Appendices D-J were not before the Examiner during prosecution of the '336 patent. Further, it is believed that the references in Appendices D, E, and G are not before the Examiner in the below described reexaminations of the '336 patent. For convenience, the aforementioned references are cited on the attached Form PTO-1449.

#### IV. CO-PENDING PROSECUTION AND LITIGATION

Requester believes that the '336 patent has not yet been adjudged invalid or unenforceable. Three reexaminations of the '336 patent, control numbers 90/008,237, 90/008,306, and 90/008,474, have been merged and are ongoing as of this request's filing date. Requester is aware of several pending lawsuits involving the '336 patent:

- Acer, Inc. et al. v. Technology Properties Limited et al., CV 08-00877 HRL, Filed Feb. 8, 2008 (N.D. Cal.)

- HTC Corp. et al. v. Technology Properties Limited et al., CV 08-00882 JL, Filed Feb. 8, 2008 (N.D. Cal.)

- BARCO v. Technology Properties Limited et al., CV 08-05398, Filed Dec. 1, 2008 (N.D. Cal.)

#### V. THE PROSECUTION HISTORY OF THE '336 PATENT

The application that matured into the '336 patent was filed on June 7, 1995 as a division of U.S. Patent No. 5,440,749 which itself was filed on August 3, 1989. The '336 application included 70 claims, although all but six were immediately cancelled. Claim 19, the only claim to survive the entire prosecution, eventually became Claim 1 of the '336 patent and originally read:

A microprocessor system, comprising a central processing unit and a ring counter variable speed system clock connected to said central processing unit, said central processing unit and said ring counter variable speed system clock being provided in a single integrated circuit.

(Appendix B, Application, June 6, 1995, original page 68).

During examination of the '336 application, the Examiner issued four office actions and the Applicant amended the claims in response to each. The Examiner rejected the independent claims after each subsequent amendment by the Applicant. After the fourth office action, an Examiner interview was held on April 23, 1998. During the interview, the Examiner proposed amendment of original dependent claims 20, 66, 75, and 79 and indicated that the amended claims 20, 66, 75, and 79 would be allowable if rewritten in independent form. (Appendix B, Applicant Remarks, April 24, 1998; Examiner Interview Summary Record, May 13, 1998) Each of original claims 20, 66, 75, and 79 included a limitation directed toward an input/output interface that is connected to a second clock which is independent of the ring oscillator. The Applicant accordingly amended the independent claims to include the limitations of original

dependent claims 20, 66, 75, and 79. Namely, the independent claims were amended to recite an on-chip I/O interface and a second I/O clock that is independent of the ring oscillator. For example, claim 19 was amended:

A microprocessor system, comprising a single integrated circuit including a central processing unit and an entire ring oscillator variable speed system clock in said single integrated circuit and connected to said central processing unit for clocking said central processing unit, said central processing unit and said ring oscillator variable speed system clock each including a plurality of electronic devices correspondingly constructed of the same process technology with corresponding manufacturing variations, a processing frequency capability of said central processing unit and of said ring oscillator variable speed system clock varying together due to said manufacturing variations and due to at least operating voltage and temperature of said single integrated circuit; an on-chip input/output interface connected to exchange coupling control signals, addresses and data with said central processing unit; and a second clock independent of said ring oscillator variable speed system clock connected to said input/output interface.

(Appendix B, Applicant Remarks, April 24, 1998 at Claim 19). The application was subsequently allowed.

Accordingly, the '336 patent was allowed principally because the prior art before the Examiner was believed not to disclose an integrated circuit with an on-chip I/O interface clocked by a second clock independent of the variable speed system clock.

### VI. POSITIONS TAKEN BY PATENT OWNER THAT ARE MATERIAL TO PATENTABILITY

The Patent Owner has sent numerous communications to third parties in an attempt to solicit licenses under the '336 patent. The communications generally include claim charts stamped "confidential" that purport to show the correspondence between the third party processor systems and the claims of '336 patent.

In these claim charts the Patent Owner has taken various positions to the effect that any processors having certain features would necessarily have other features recited in the claims of the '336 patent. These are particularly relevant to the Office's assessment of how one skilled in the art would interpret various prior art references. In particular, if the Patent Owner's assertions are accepted, then various prior art references explicitly teaching certain features would be understood by one skilled in the art as implicitly disclosing other features.

Where the Patent Owner has taken a position in third party correspondence which would dictate a finding that a certain feature would be understood to be present in a prior art system, that fact is noted in the claim charts set forth below.

The Office is encouraged to request from the Patent Owner the claim charts and related third party communications concerning the '336 patent under Rule 105. <sup>1</sup> Requester understands that scores of substantially similar claim charts have been sent to various companies throughout the semiconductor and other industries.

The Requester notes that the functionality of prior art processors are the same in material respect as commercial processors referred to by the Patent Owner in the above mentioned communications to third parties (e.g., with regard to on-chip oscillators, serial I/O ports, etc.). For example, the Mostek 3870 family of processors of the 1980's included serial I/O ports with independent I/O clocks for conducting asynchronous I/O functions. (See, e.g., Mostek, 3870 Microcomputer Data Book (Feb. 1981) at page III-105). Therefore, if the Patent Owner's assertions are true today as to commercial processors, then they are also true as to the prior art processors.

## VII. QUESTIONS OF PATENTABILITY PRESENTED HEREIN ARE NEW RELATIVE TO THE PENDING REEXAMINATION PROCEEDINGS

The prior art references provided in this request present a substantial new question of patentability as to claims 1-10 of the '336 patent even with respect to the reexamination requests previously filed against the '336 patent. Both the Richter reference (Appendix D) and the Dozier reference (Appendix E) were not before the examiner during the original examination of the '336

Requester submits that the Office is empowered to request this information under Rule 105, which provides in pertinent part:

<sup>(</sup>a) (1) In the course of examining or treating a matter in a pending or abandoned application filed under 35 U.S.C. 111 or 371 (including a reissue application), in a patent, or in a reexamination proceeding, the examiner or other Office employee may require the submission, from individuals identified under § 1.56(c), or any assignee, of such information as may be reasonably necessary to properly examine or treat the matter, for example:

<sup>(</sup>viii) Technical information known to applicant. <u>Technical information known to applicant concerning the related art, the disclosure, the claimed subject matter, other factual information pertinent to patentability, or concerning the accuracy of the examiner's stated interpretation of such items.</u>

The assertions of infringement made by Patent Owner explicitly contain a technical assessment of architecture defining a ring oscillator, a second clock independent of the ring oscillator, and whether the ring oscillator and a CPU clocked by the ring oscillator inherently include a plurality of devices and whether the frequency of the ring oscillator and the speed of the CPU would vary together due to manufacturing due to manufacturing variations. Requestor respectfully submits that this information is clearly "factual information pertinent to patentability." The Office is accordingly urged to request that the Patent Owner produce claim charts and other materials submitted to third parties sufficient to demonstrate the technical and claim construction positions taken by the Patent Owner.

patent and are not currently before the examiner in the pending merged reexamination proceeding (Reexamination Control Number 90/008,306). As to the Mostek reference, the arguments presented herein are substantially different than those presented in the reexamination request filed by the Public Patent Foundation on January 30, 2007. For example, that earlier request did not argue that the Mostek reference anticipates any claim of the '336 patent. Furthermore, the Mostek reference has never been adopted for use in a rejection during the pending reexamination proceedings. The following sections set forth in detail the correspondence between claims 1-10 and the Mostek, Richter, and Dozier references.

# VIII. THE MOSTEK REFERENCE ANTICIPATES OR RENDERS OBVIOUS CLAIMS 1-10 OF THE '336 PATENT

The prior art references provided in this request raise substantial new questions of patentability as to claims 1-10 of the '336 patent. Specifically, claims 1-7, 9, and 10 are anticipated by the Mostek reference and additionally all claims (e.g. claims 1-10) are rendered obvious by Mostek in light of the Kato reference.

#### A. Summary of the Teachings of the Mostek Reference

The Mostek, 3870 Microcomputer Data Book (Feb. 1981) ("Mostek") teaches the MK3873, which the data book describes as a single semiconductor chip containing a main control logic that is clocked by a variable internal oscillator. The MK3873 single semiconductor chip also includes a serial I/O port that can be clocked by a fixed frequency, external clock that is independent of the internal oscillator.

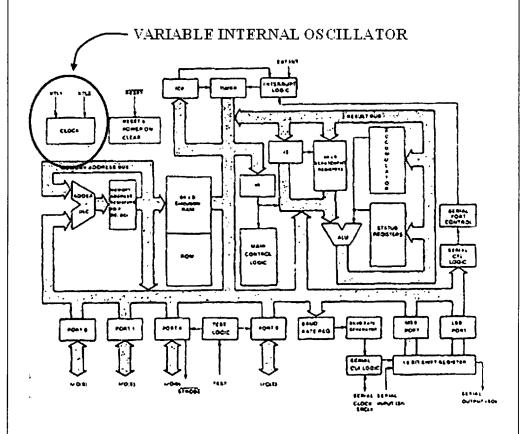

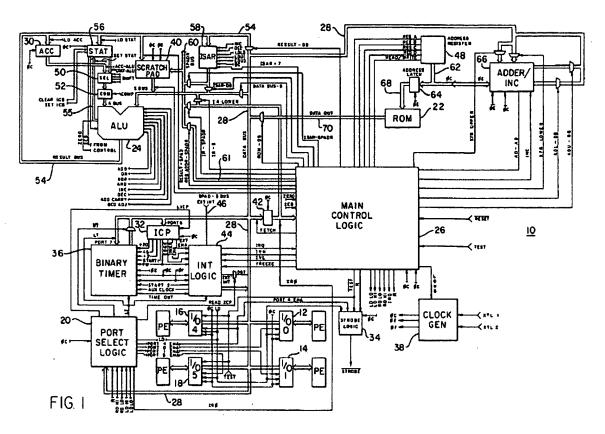

More specifically, Mostek teaches a "single chip microcomputer" that includes an "on-chip oscillator circuit which provides an internal clock." (Appendix F, pages III-114 to III-115). The frequency of the on-chip oscillator, and thus the processing speed of the main control logic, varies in response to temperature and Vcc variations, as one skilled in the art would understand from reference to other data books describing the MK3873 microprocessor. (Appendix J, Fig. 3; pages 2019 and 2024-2026).

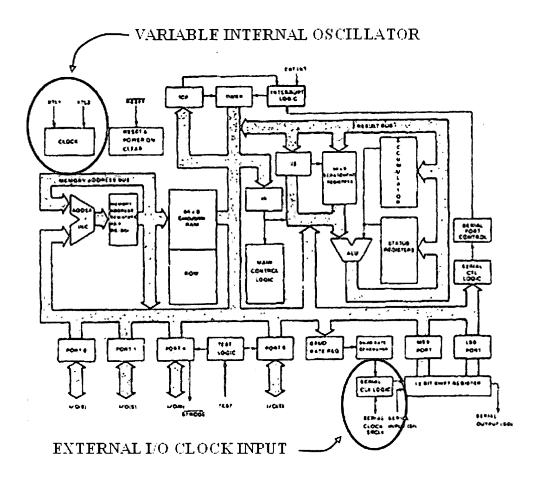

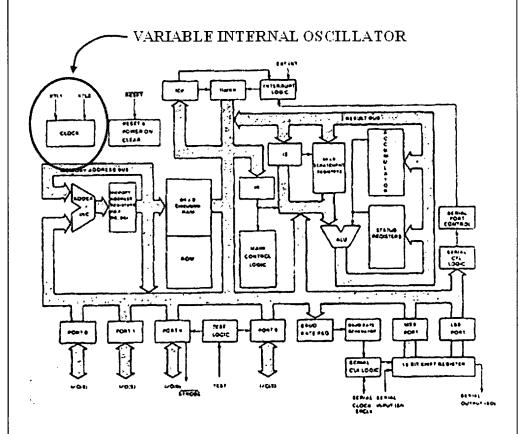

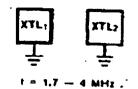

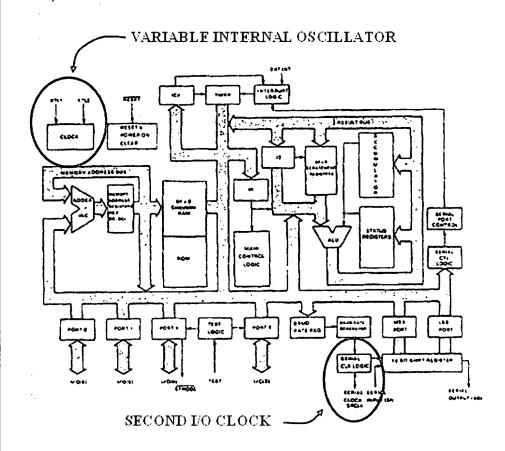

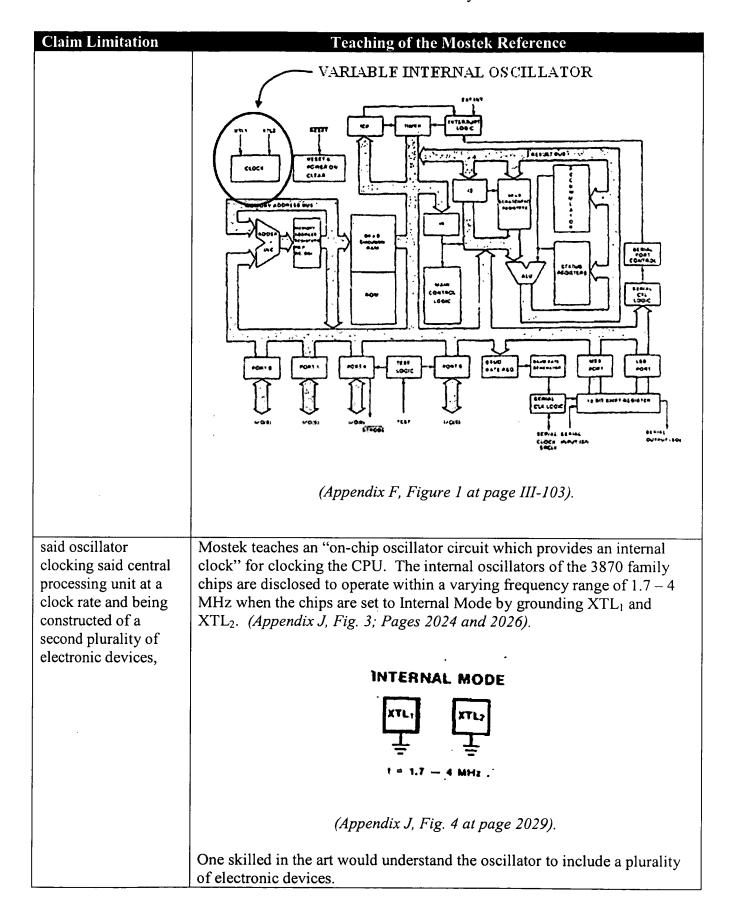

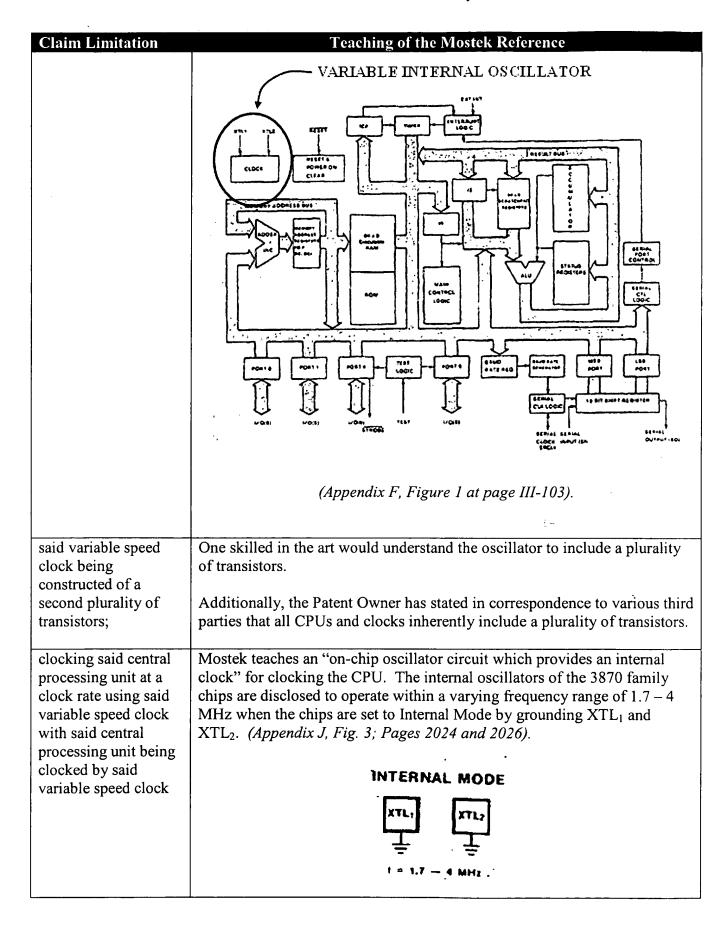

(Appendix F, Figure 1 at page III-103).

Mostek teaches a serial I/O port that is clocked by an external clock independent of the on-chip oscillator circuit. (Appendix F, pages III-105 and III-114 to III-115). The external clock may use a crystal to provide a fixed frequency signal. (Appendix F, pages III-109 to III-110). Additionally, the serial port is "very flexible so that it could be used . . . as an interface to . . . serial memory devices." (Appendix F, page III-102, col. 1).

#### B. The Mostek Reference Anticipates Claims 1-7, 9 and 10 of the '336 Patent

The '336 patent claims the same functionality described above in connection with the Mostek reference. The patent claims a microprocessor system comprising a single integrated circuit that includes a ring oscillator and a central processing unit (CPU), where the ring oscillator clocks the CPU. (Appendix A, Claim 1). The claimed ring oscillator and CPU include a plurality of electronic devices that are constructed of the same process technology so that the frequency of the central processing unit and the speed of the ring oscillator vary together.

(Appendix A, Claim 1). The claimed integrated circuit also includes an on-chip I/O interface, to which a second clock independent of the ring oscillator is connected. (Appendix A, Claim 1).

This is precisely the functionality taught by the Mostek reference. Mostek teaches a microcomputer implemented on a single chip that includes a main control logic clocked by an internal oscillator, where the frequency of the main control logic and the internal oscillator vary together due to variations in at least temperature and Vcc. The Patent Owner has asserted in correspondence with third parties that an internal oscillator indicates the presence of a ring oscillator and that a CPU and an on-chip oscillator inherently include a plurality of devices and are constructed of the same process technology. Significantly, Mostek discloses a serial input/output port that is clocked by an external clock that is independent of the variable speed oscillator.

Detailed correspondence between the Mostek reference and claims 1-7, 9, and 10 of the '336 patent is shown in the claim chart in section D below.

### C. The Mostek Reference, in Light of the Kato Reference, Renders Obvious Claims 1-10 of the '336 Patent

In addition to Mostek's anticipation of the '336 patent as described above, the Mostek reference, when viewed in light of the Kato reference, further renders obvious several of the limitations already taught by Mostek.

It would have been obvious for one skilled in the art to modify the teachings of Mostek so that a ring oscillator was implemented as Mostek's disclosed variable speed oscillator. This is because the Kato reference discloses a "one-chip semiconductor device" (Appendix H, col. 1, lines 6-9) that is clocked by a ring oscillator because the clock signal "need not have a very accurate frequency." (Appendix H, col. 10, line 64 to col. 11, line 7). The ring oscillator's "output frequency lowers in proportion to the speed of the data processing circuit which is lowered due to the drop of power supply voltage." (Appendix H, col. 11, lines 1-5).

One skilled in the art would have seen an apparent reason to implement the variable speed oscillator disclosed in Mostek with Kato's ring oscillator, namely because the family of chips described by the Mostek data book also operate from their internal oscillators when "timing is not critical" and a ring oscillator is an obvious selection for an internal oscillator. (Appendix J, page 2019). One skilled in the art would realize the benefits of implementing Kato's ring oscillator as Mostek's variable oscillator to reduce power consumption during

periods of lessened processing demand and to increase clock speed (and power consumption) during periods of increased processing demand. (Appendix H, col. 11, lines 2-7). Kato additionally teaches a second clock connected to the I/O port which operates synchronously relative to the ring oscillator as recited in claim 8 of the '336 patent. Therefore, claims 1-10 of the '336 patent are at a minimum rendered obvious by Mostek in view of Kato.

## D. Claim Chart Setting Forth the Correspondence Between the Mostek Reference and Claims 1-10 of the '336 Patent

As described herein, the Mostek reference (Appendix F) taken alone or in combination with the Kato reference, raises substantial new questions of patentability for all claims of the '336 patent. The following claim chart demonstrates that all elements in claims 1-10 are anticipated or rendered obvious by the Mostek reference.

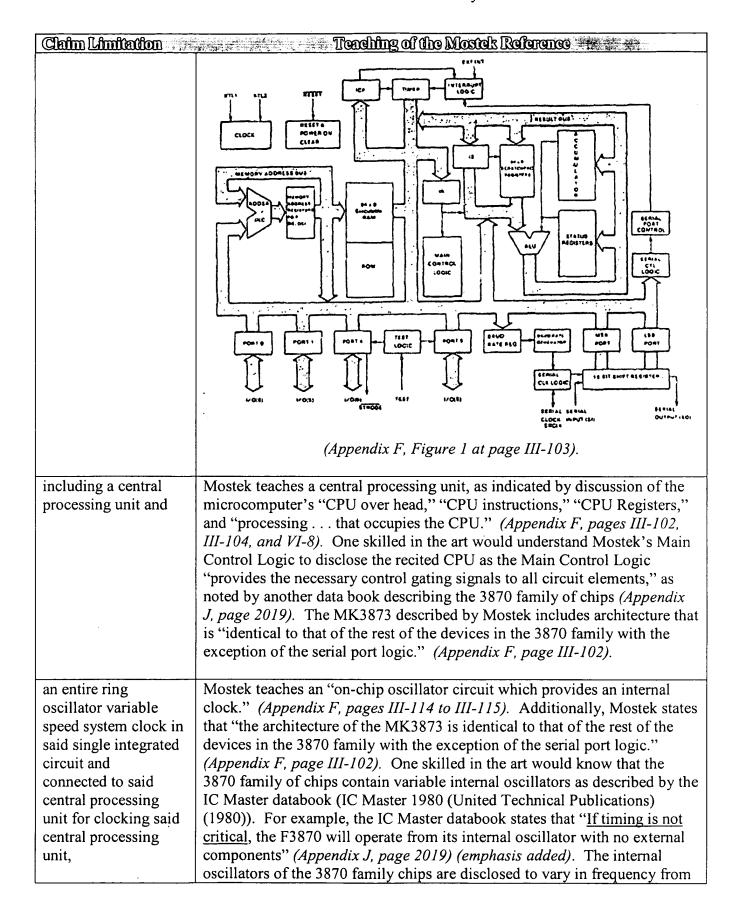

| Claim Limitation                                                   | Teaching of the Mostek Reference                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Claim 1                                                            |                                                                                                                                                                                                                                                                                                 |

| 1. A microprocessor system, comprising a single integrated circuit | This feature is taught by Mostek, 3870 Microcomputer Data Book (Feb. 1981) ("Mostek"). The Mostek reference discloses a "single chip microcomputer" with features including a main control logic, executable RAM, ROM, and a serial input/output port. (Appendix F, pages III-102 and III-103). |

#### **Claim Limitation**

#### **Teaching of the Mostek Reference**

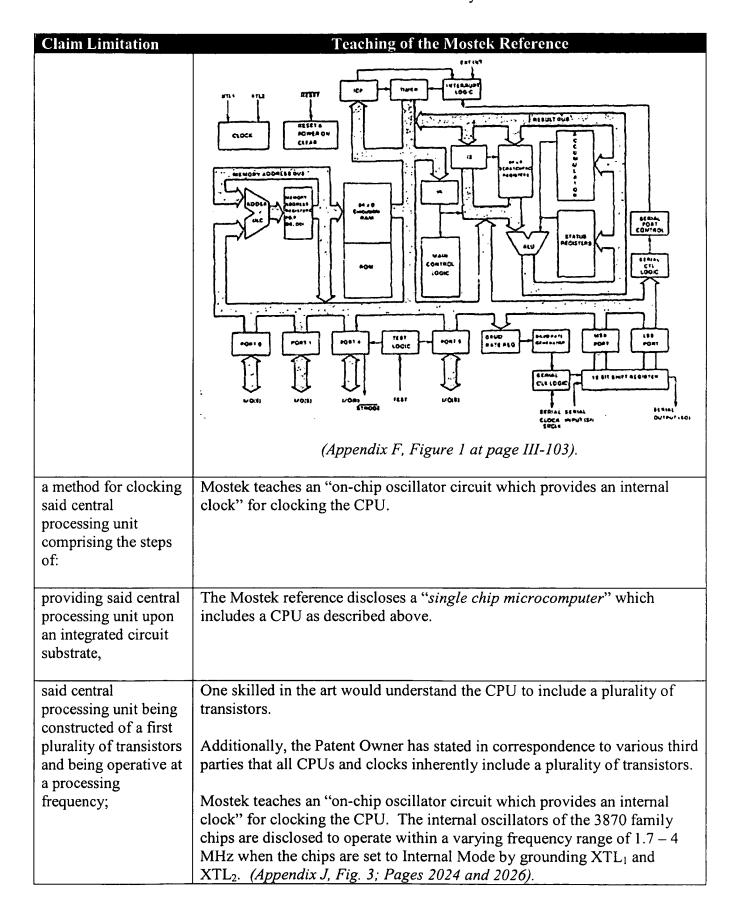

1.7 - 4 MHz when the chips are set to Internal Mode by grounding XTL<sub>1</sub> and XTL<sub>2</sub>. (Appendix J, Fig. 3; Pages 2024 and 2026).

### INTERNAL MODE

(Appendix J, Fig. 4 at page 2029).

(Appendix F, Figure 1 at page III-103).

The Patent Owner has asserted in correspondence to various third parties that all on-chip oscillators are variable and that the presence of an on-chip clock generation circuit indicates the presence of a ring oscillator (the Office is urged to require Patent Owner to produce this correspondence under Rule 105). The Requester notes that the functionality of prior art processors are the same in material respect to commercial processors referred to by the Patent Owner in the above mentioned communications to third parties. Therefore, such an allegation, if true with respect to today's

#### Teaching of the Mostek Reference Claim Limitation processors, would also be true with regard to the Mostek 3870 family of processors. Accordingly, if the office accepts this premise, one skilled in the art would have understood Mostek to disclose a ring oscillator for clocking the central processing unit. Alternatively, the use of a ring oscillator as Mostek's variable internal oscillator is obvious in view of United States Patent No. 4,766,567 to Kato. Kato describes a ring oscillator that can be used to supply clock signals for the CPU described in Mostek. This is because Kato similarly describes a "one-chip semiconductor device" (Appendix H, col. 1, lines 6-9) that utilizes a ring oscillator because the device "need not have a very accurate frequency." (Appendix H, col. 10, line 64 to col. 11, line 7). The ring oscillator's "output frequency lowers in proportion to the speed of the data processing circuit which is lowered due to the drop of power supply voltage." (Appendix H, col. 11, lines 1-5). One skilled in the art would have seen an apparent reason to implement Kato's ring oscillator as the variable speed oscillator of Mostek, namely because the family of chips described by the Mostek data book also operate from their internal oscillators when "timing is not critical" and a ring oscillator is an obvious selection for an internal oscillator. (Appendix J. page 2019). One skilled in the art would realize the benefits of implementing Kato's ring oscillator as Mostek's variable oscillator to reduce power consumption during periods of lessened processing demand and to increase clock speed (and power consumption) during periods of increased processing demand. (Appendix H, col. 11, lines 2-7). said central One skilled in the art would understand the on-chip oscillator circuit and the processing unit and main control logic to include a plurality of electronic devices. said ring oscillator variable speed system With respect to the limitation of the CPU and ring oscillator being clock each including a constructed of the same process technology, Mostek teaches a plurality of electronic microprocessor system fabricated on a single chip, which would necessarily devices be constructed by a single process technology. Mostek describes the internal oscillator as an "on-chip oscillator circuit" indicating that the correspondingly constructed of the oscillator is fabricated on the same chip as the CPU and that the oscillator same process and CPU would therefore be constructed by the same process technology. technology with (Appendix F, page III-114) corresponding manufacturing It is noteworthy that the Patent Owner has stated in correspondence to variations, various third parties that the features of this limitation are inherent in an integrated circuit with a CPU and a clock (the Office is urged to require Patent Owner to produce this correspondence under Rule 105). As one specific example, the Patent Owner has stated that because of "the laws of physics and the state of the art of microprocessor manufacturing, the

processing frequency of said central processing unit and the speed of the

#### Claim Limitation

#### Teaching of the Mostek Reference

ring oscillator, because they are located on the same integrated circuit, vary together due to manufacturing variations." (Reexamination Control Number 90/008,306, Original Ex Parte Request by Third Party, Exhibit 13 at 6).

As an aside, Requestor notes that this feature was commonplace at the time of filing, as shown by U.S. Patent No. 4,691,124 to Ledzius et al. ("Ledzius"). Ledzius teaches that manufacturing circuits from the "same batch and section of semiconductor wafer" results in process variations throughout the circuit. (Appendix I, col. 4, lines 11-12). One skilled in the art would have found an apparent reason to combine Ledzius with Mostek, namely to produce Mostek's processor with minimal cost and defects.

a processing

frequency capability

of said central

processing unit and a

speed of said ring

oscillator variable

speed system clock

varying together due

to said manufacturing

variations and due to

at least operating

voltage and

temperature of said

single integrated

circuit;

Mostek's microcomputer varies in frequency from 1.7-4MHz when operating from its internal oscillator due in part to a varying ambient temperature range of 0-70 °C and a varying VCC of +5V +/- 10%, as one skilled in the art would understand by referencing the IC Master data book that describes the entire 3870 family. (Appendix J, pages 2025-2026).

In any case, the Patent Owner has stated in correspondence to various third parties that because of "the laws of physics and the state of the art of microprocessor manufacturing, the processing frequency of said central processing unit and the speed of the ring oscillator, because they are located on the same integrated circuit, vary together due to manufacturing variations, operating voltage and temperature." (Reexamination Control Number 90/008,306, Original Ex Parte Request by Third Party, Exhibit 13 at 6).

Further, during the examination of the '336 patent, the Applicant stated that "the placement of [the ring oscillator clock and the microprocessor] within the same integrated circuit" causes the microprocessor and clock to naturally "vary commensurately in speed as a function of various parameters (e.g., temperature) affecting circuit performance." (Appendix B, April 15, 1996 Applicant Arguments, original page 6.)

Additionally and as describe previously, one skilled in the art would see an apparent reason to implement the ring oscillator of Kato as the variable oscillator of Mostek. One skilled in the art would realize the benefits of implementing Kato's ring oscillator as Mostek's variable oscillator to reduce power consumption during periods of lessened processing demand and to increase clock speed (and power consumption) during periods of increased processing demand. (Appendix H, col. 11, lines 2-7).

As an aside, Requestor notes that Ledzius teaches that manufacturing circuits from the "same batch and section of semiconductor wafer" results

| Claim Limitation                                                                                                             | Teaching of the Mostek Reference                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              | in frequency variations due to process and temperature variations throughout the circuit. (Appendix I, col. 4, lines 3-21). One skilled in the art would have found an apparent reason to combine Ledzius with Mostek, namely to produce the processor of Mostek with minimal cost and defects.                                                                                                                                                                         |

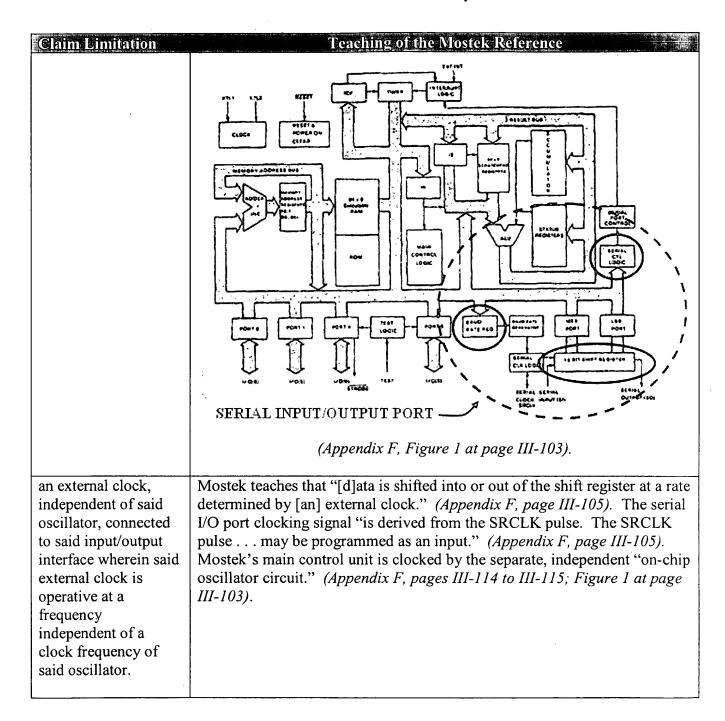

| an on-chip input/output interface connected to exchange coupling control signals,                                            | Mostek teaches a "Serial Input/Output Port [that] consists of a serial Shift Register, baud rate generator, and control logic." (Appendix F, page III-105).                                                                                                                                                                                                                                                                                                             |

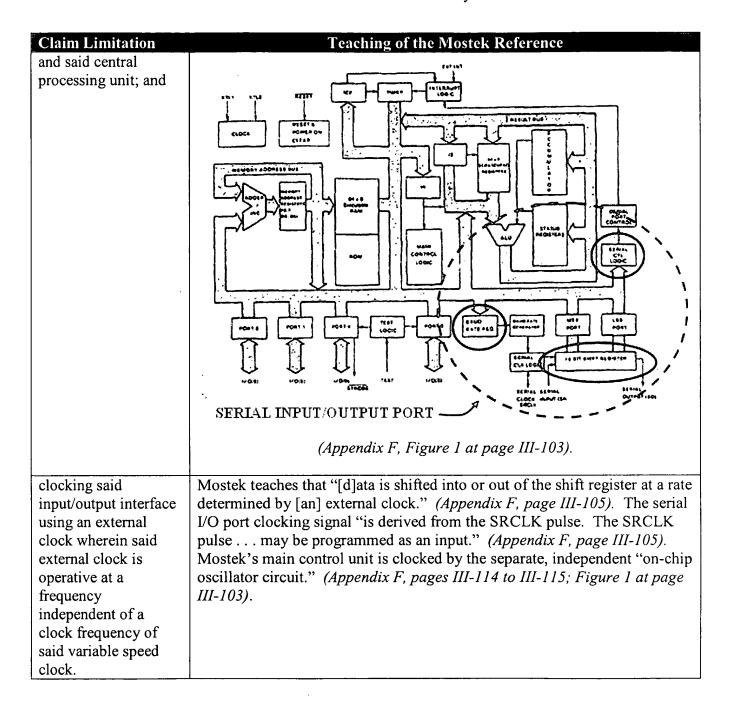

| addresses and data with said central processing unit;                                                                        | SERIAL INPUT/OUTPUT PORT  (Appendix F, Figure 1 at page III-103).                                                                                                                                                                                                                                                                                                                                                                                                       |

| and a second clock independent of said ring oscillator variable speed system clock connected to said input/output interface. | Mostek teaches that "[d]ata is shifted into or out of the shift register at a rate determined by [an] external clock." (Appendix F, page III-105). The serial I/O port clocking signal "is derived from the SRCLK pulse. The SRCLK pulse may be programmed as an input." (Appendix F, page III-105). Mostek's main control unit is clocked by the separate, independent "on-chip oscillator circuit." (Appendix F, pages III-114 to III-115; Figure 1 at page III-103). |

#### **Claim Limitation**

#### Teaching of the Mostek Reference

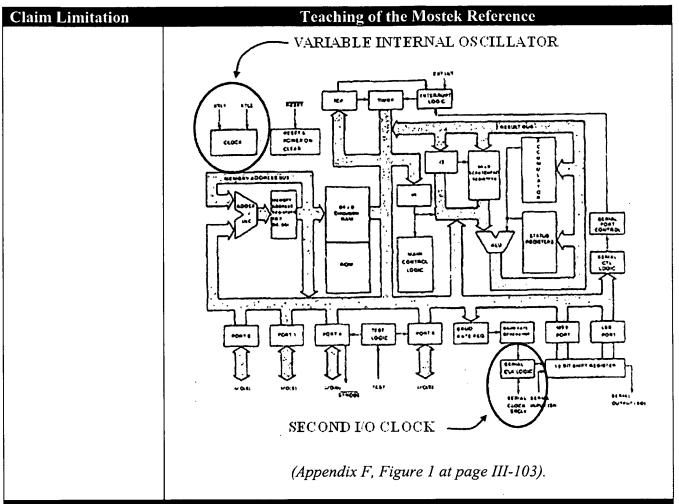

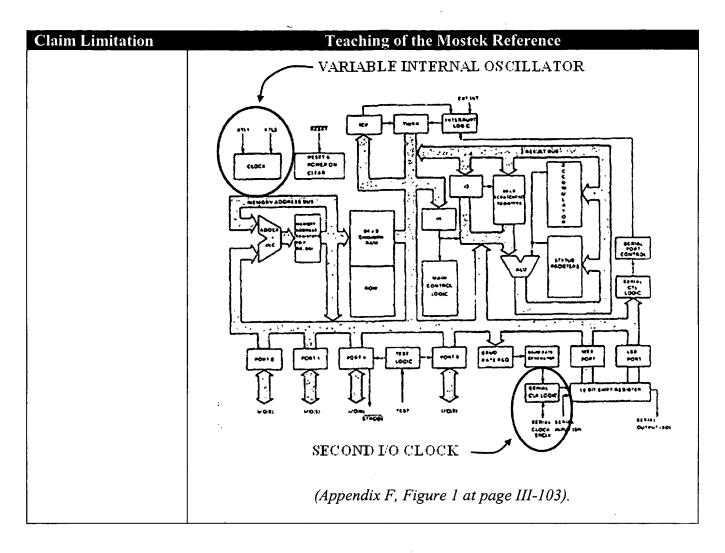

ring oscillator system clock

IC Master databook (IC Master 1980 (United Technical Publications) (1980)). For example, the IC Master databook states that "If timing is not critical, the F3870 will operate from its internal oscillator with no external components" (Appendix J, page 2019) (emphasis added). The internal oscillators of the 3870 family chips are disclosed to vary in frequency from 1.7 – 4 MHz when the chips are set to Internal Mode by grounding XTL<sub>1</sub> and XTL<sub>2</sub>. (Appendix J, Fig. 3; Pages 2024 and 2026).

#### INTERNAL MODE

(Appendix J, Fig. 4 at page 2029).

(Appendix F, Figure 1 at page III-103).

The Patent Owner has asserted in correspondence to various third parties that all on-chip oscillators are variable and that the presence of an on-chip clock generation circuit indicates the presence of a ring oscillator (the

| Claim Limitation                                                                                                               | Teaching of the Mostek Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                | Office is urged to require Patent Owner to produce this correspondence under Rule 105). The Requester notes that the functionality of prior art processors are the same in material respect to commercial processors referred to by the Patent Owner in the above mentioned communications to third parties. Therefore, such an allegation, if true with respect to today's processors, would also be true with regard to the Mostek 3870 family of processors. Accordingly, if the office accepts this premise, one skilled in the art would have understood Mostek to disclose a ring oscillator for clocking the central processing unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                | Alternatively, the use of a ring oscillator as Mostek's variable internal oscillator is obvious in view of United States Patent No. 4,766,567 to Kato. Kato describes a ring oscillator that can be used to supply clock signals for the CPU described in Mostek. This is because Kato similarly describes a "one-chip semiconductor device" (Appendix H, col. 1, lines 6-9) that utilizes a ring oscillator because the device "need not have a very accurate frequency." (Appendix H, col. 10, line 64 to col. 11, line 7). The ring oscillator's "output frequency lowers in proportion to the speed of the data processing circuit which is lowered due to the drop of power supply voltage." (Appendix H, col. 11, lines 1-5). One skilled in the art would have seen an apparent reason to implement Kato's ring oscillator as the variable speed oscillator of Mostek, namely because the family of chips described by the Mostek data book also operate from their internal oscillators when "timing is not critical" and a ring oscillator is an obvious selection for an internal oscillator. (Appendix J, page 2019). One skilled in the art would realize the benefits of implementing Kato's ring oscillator as Mostek's variable oscillator to reduce power consumption during periods of lessened processing demand and to increase clock speed (and power consumption) during periods of increased processing demand. (Appendix H, col. 11, lines 2-7). |

| constructed of electronic devices within the integrated circuit,                                                               | One skilled in the art would understand the on-chip oscillator circuit and the main control logic to include a plurality of electronic devices.  Additionally, the Patent Owner has stated in correspondence to various third parties that all CPUs and clocks inherently include a plurality of electronic devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| said electronic devices having operating characteristics which will, because said entire ring oscillator system clock and said | Mostek teaches a microprocessor system fabricated on a single chip, which would necessarily be constructed by a single process technology. Mostek describes the internal oscillator as an "on-chip oscillator circuit" indicating that the oscillator is fabricated on the same chip as the CPU and that the oscillator and CPU would therefore be constructed by the same process technology. (Appendix F, page III-114)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Claim Limitation                                                                                                                                                      | Teaching of the Mostek Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| microprocessor are located within the same integrated circuit, vary together with operating characteristics of electronic devices included within the microprocessor; | It is noteworthy that the Patent Owner has stated in correspondence to various third parties that the features of this limitation are inherent in an integrated circuit with a CPU and a clock (the Office is urged to require Patent Owner to produce this correspondence under Rule 105). As one specific example, the Patent Owner has stated that because of "the laws of physics and the state of the art of microprocessor manufacturing, the processing frequency of said central processing unit and the speed of the ring oscillator, because they are located on the same integrated circuit, vary together due to manufacturing variations." (Reexamination Control Number 90/008,306, Original Ex Parte Request by Third Party, Exhibit 13 at 6). |